本篇内容来源于中国大学mooc《计算机组成与CPU设计实验》 (江苏大学)中的课程视频、PPT等相关资料。

本篇内容为《计算机组成与CPU设计实验》——计数器

参考视频:

计数器

逻辑功能

- 对输入时钟脉冲进行计数

- 也可用于分频、定时、产生节拍脉冲等

分类

- 按时钟输入方式,分为同步和异步计数器

- 按进位体制,分为二进制、十进制和任意进制计数器

- 按计数方向,分为加法、减法和可逆计数器

计数器的“模”(Modulo)

计数器运行时,依次遍历规定的各状态后完成一次循环,它所经过的状态总数称为计数器的“模”,通常用M表示。

例子:

一个2位的二进制计数器循环输出00、01、10和11,称为模4计数器。

同理,3位的二进制计数器的M=8。

模2计数器的输出是?0 1

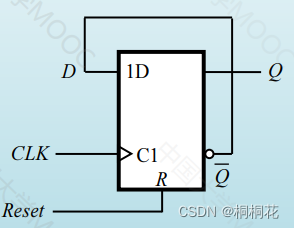

1位二进制计数器(模2)

1位二进制计数器电路

1位二进制计数器功能

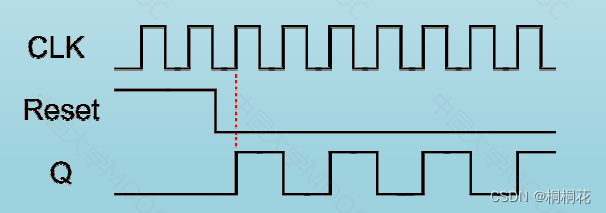

在Reset信号无效时,每当CLK上升沿到来时,触发器状态Q翻转一次。

输出信号Q的频率正好是CLK频率的二分之一,故称该电路为2分频电路。

1位二进制计数器波形图

1位二进制计数Verilog描述

module half_clk(

input CLK,

input Reset,

output reg Q

);

always@(posedge CLK)

begin

if(Reset)

Q<=0;

else

Q<=~Q;

end

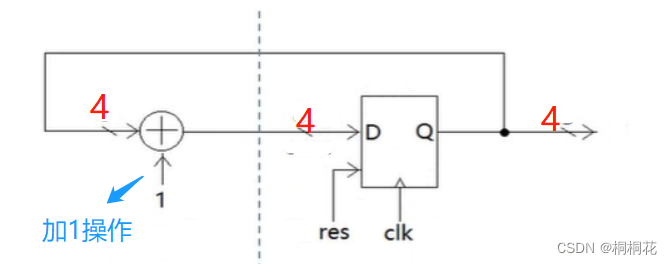

endmodule4位二进制加法计数器

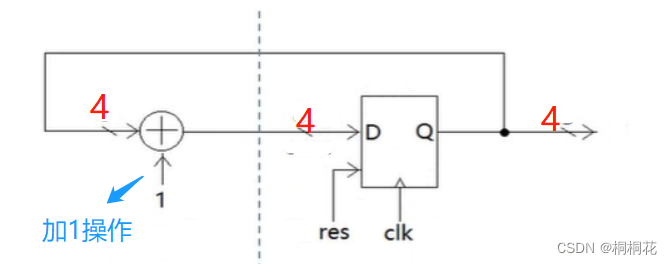

4位二进制加法计数器电路

4位二进制加法计数器波形图

4位二进制加法计数器Verilog描述

module upcount(

input CLK,

input Reset,

output reg [3:0] Q

);

always@(posedge CLK ,posedge Reset)//异步复位

begin

if(Reset)

Q<=0;

else

Q<=Q+1;

end

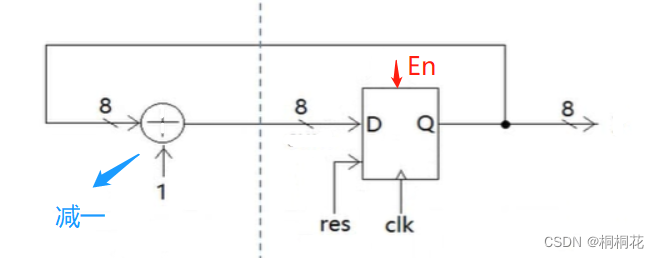

endmodule具有使能控制的 8 位减法计数器

module downcount(

input CLK,

input Reset,

input En,

output reg [3:0] Q

);

always@(posedge CLK)

begin

if(Reset)

Q<=0;

else if(En)

Q<=Q-1;

else

Q<= Q;

end

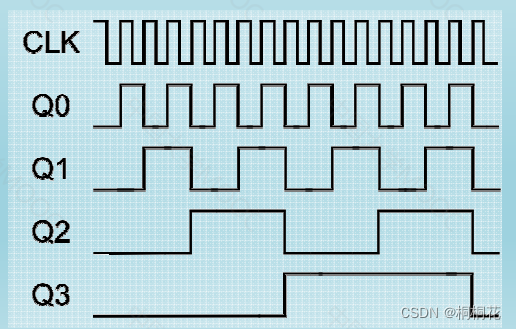

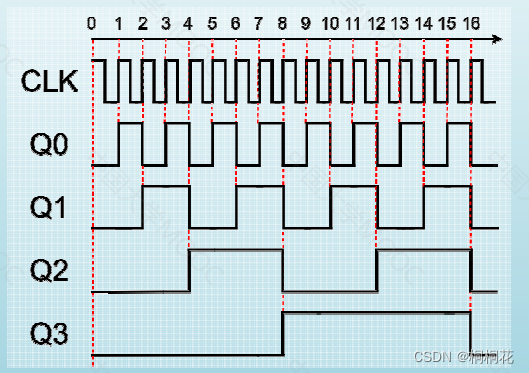

endmodule计数器的应用:分频

电路:

波形图

计数器的分频特性

- Q0:2分频

- Q1:4分频

- Q2: 8分频

- Q3: 16分频

问题:如果CLK是10MHz,希望得到2.5MHz的时钟,应采用哪个输出?

Q1四分频

Verilog描述

module upcount(

input CLK,

input Reset,

output reg [3:0] Q

);

always@(posedge CLK ,posedge Reset)

begin

if(Reset)

Q<=0;

else

Q<=Q+1;

end

endmodulen位二进制计数器(模),可实现

分频

占空比为50%的偶数分频器

占空比:在一个脉冲周期内,高电平时间相对于总时间所占的比例。

定义RATIO为分频数:应大于等于2且为偶数;可取值6、10等,实现非的分频数。

module clockdivider

#( parameter RATIO=10 )

//10分频

(

input CLK,

input Reset,

output reg Q

);

reg [26:0]cnt;

always@(posedge CLK ,posedge Reset)

begin

if(Reset)

begin

Q<=0;

cnt <=0;

end

else if(cnt==RATIO/2 - 1) //10分频,要50%占空比,高电平占5个周期,每5个周期翻以下

Q <= ~Q;

cnt <= 0;

else

cnt<=cnt+1;

end

endmodule小结:时序逻辑电路

时序逻辑电路基本模块

- 触发器/寄存器

- 移位寄存器

- 计数器

基本功能之外的变化

复位(Reset)

- 系统复位的时候,装入一个初值。

- 有同步复位、异步复位。

装入(Load)

- 并行数据

- 在工作过程当中,如果需要,可以装入一个数据

- 移位寄存器、计数器等,都可以设计装入

- 同步 不能写入敏感列表

使能(Enable )

- 使能信号主要针对功能来说

- 对于移位寄存器,使能是控制是否允许移位

- 对于计数器,使能是控制是否计数

- 触发器/寄存器的使能即 “装入 ”

- 同步 不能写入敏感列表

时序逻辑Verilog在线练习

练习网站:

7185

7185

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?