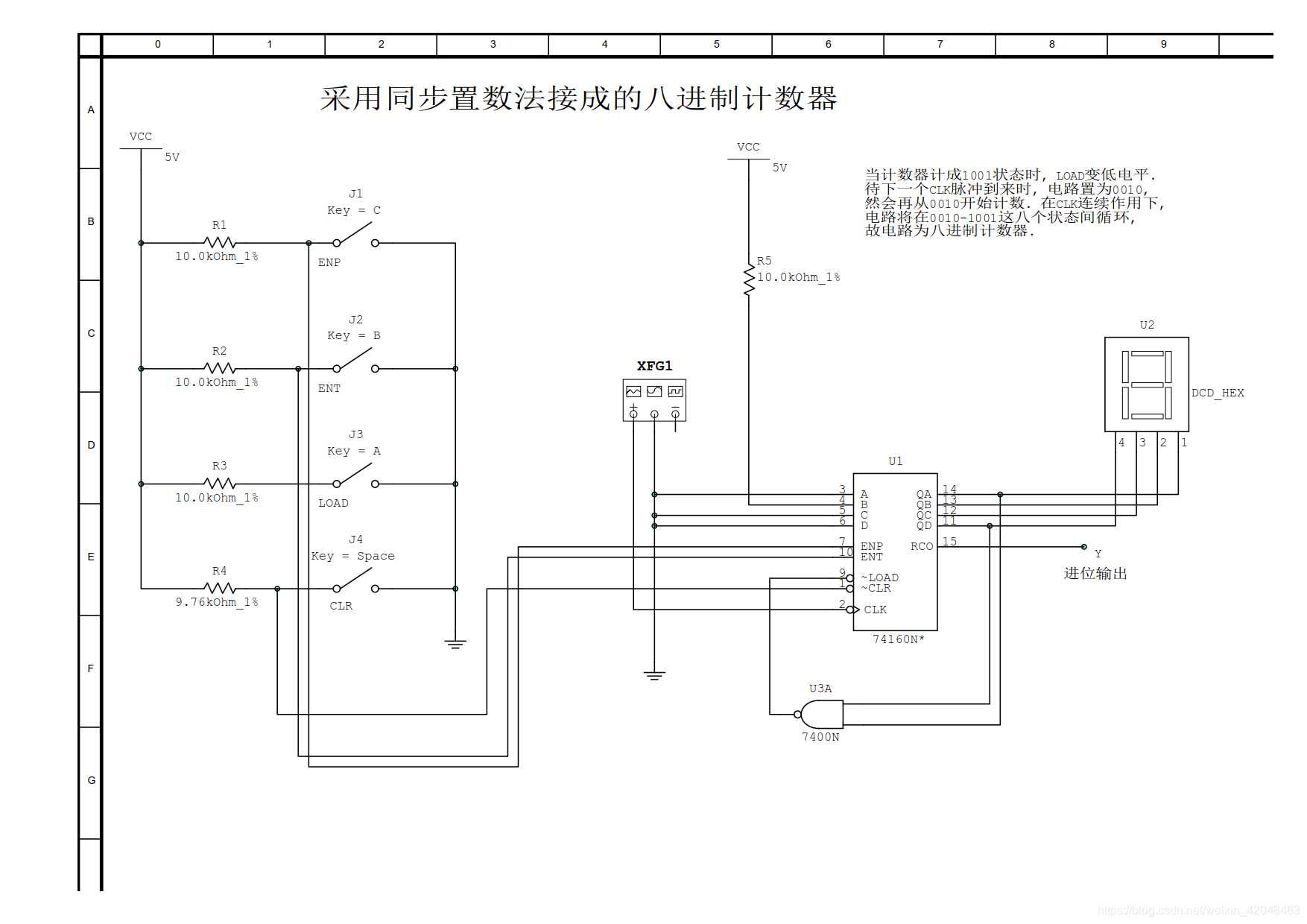

我们先来看一下电路逻辑图, 从中提取核心信息:

① 将QD、QC、QB、QA接成0010是为了配合LOAD引脚使用, 以将74160的状态置为0010.

②计数器的最大状态为1001, 当74160到达1001时, 通过7400N与非门将LOAD引脚置为0, 当下一个CLK上升沿到来时, 74160的状态即被置为0010; 当电路的状态到达0010时, LOAD引脚恢复高电平, 之后若干个CLK上升沿 74160正常计数.

③当QD、QC、QB、QA到达1001时, 计数器产生进位信号, 即RCO=1: 这正好与74160本身的性质一致, 所以可直接将74160的RCO引脚作为计数器输出引脚.

可能产生的疑问:

①ENT和ENP引脚是不是有些多余?

答: 不多余. ENT和ENP引脚有一个为低电平时, 74160即处于保持状态——后续要更新的博客"ENT引脚设计法解析"就是用这两个引脚的巧妙配合, 实现同步100进制加法计数器的功能.

②QD、QC、QB、QA被置为0010前后, 74160是如何工作的?

答: (QD, QC, QB, QA) = (1,0,0,0) -> 系统CLK上升沿到来 -> (QD, QC, QB, QA) = (1,0,0,1) -> LOAD 由 1->0 -> 系统CLK上升沿到来 -> (QD, QC, QB, QA) = (D, C, B, A) = (0,0,1,0) -> LOAD 由 0->1 -> 系统CLK上升沿到来 -> (QD, QC, QB, QA) = (0,0,1,1) -> ...... -> (QD, QC, QB, QA) = (1,0,0,0). 74160按照上述描述循环变化. 补充说明一下,

本文详细解析74160同步置数法,通过电路逻辑图解释如何配置74160状态以实现0010起始的同步八进制计数器。内容涵盖LOAD引脚作用、计数器最大状态、RCO进位信号的使用,以及在不同状态下的工作原理。此外,解答了关于74160的ENT和ENP引脚、同步置数法设计进位逻辑、RCO引脚的应用限制等问题。

本文详细解析74160同步置数法,通过电路逻辑图解释如何配置74160状态以实现0010起始的同步八进制计数器。内容涵盖LOAD引脚作用、计数器最大状态、RCO进位信号的使用,以及在不同状态下的工作原理。此外,解答了关于74160的ENT和ENP引脚、同步置数法设计进位逻辑、RCO引脚的应用限制等问题。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1788

1788

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?