SD-HOST模块功能简述

1.SD_IF(interface)模块:ahb_slave接口模块,内含控制寄存器,供CPU访问,决定HOST的工作模式;

AHB总线接口功能模块,用于CPU通过驱动软件对SD HOST控制器进行访问。

◆功能:

(1)AHB slave接口,允许CPU访问,控制sd_host的运行方式;

(2)同步逻辑,SD域产生的信号同步到AHB域,供软件判断。

2.sd_clk模块:hclk分频电路,作为HOST模块时钟输入;

◆功能:

(1)允许软件干预时钟分频(in_sd_clk_enable)

(a)是否输出时钟

(b)频率与参考时钟关系

(2)允许硬件干预时钟处理(hw_stop_clk)

(a)是否输出时钟

(b)频率与参考时钟关系

| Singals | I/O | Width | declaration |

| hclk hrst_n in_clk_divider in_sd_clk_enable hw_stop_clk out_sd_clk_dft in_TestMode | input input input input input output input | 1 1 [7:0] 1 1 1 1 | 时钟信号 复位信号 分频关系 分频使能 硬件停时钟使能 频率输出 测试模式 |

时钟输出描述

- 分频系数置0,则模块输出不分频;

- 停时钟有效使能(!in_sd_clk_enable || hw_stop_clk),输出0电平时钟;

- 测试模式下,输出外部时钟。

3.sd_cmd_fsm模块:命令操作控制模块,控制sd_cmd_send_shift_register和

sd_cmd_recrive_shift_register模块;

命令发送/响应接受控制模块,根据输入的控制信号,进行状态机的跳转判定,以控制sd_cmd_send_shift_register和 sd_cmd_recrive_shift_register模块进行符合SD协议的数据处理过程。

| Singals | I/O | Width | declaration | ||

| in_sd_clk | input | 1 | 时钟信号 | ||

| hrst_n | input | 1 | 异步复位 | ||

| in_soft_reset | input | 1 | 软件复位 | ||

| in_longresponse (R2) | input | 1 | Device有命令长回复信号 | ||

| in_response | input | 1 | Device有命令回复信号 | ||

| in_commang_ready | input | 1 | 命令有效,状态机启动信号 | ||

| in_sd_dat(注意是否只需一根线) | input | [3:0] | 数据输入端口 | ||

| in_sd_cmd | input | 1 | 命令输入端口 | ||

| current_state | output | [2:0] | 状态机标志位 | ||

| has_send_bit | output | [5:0] | 已发送命令bit位大小 | ||

| has_receive_bit | output | [7:0] | 已接收命令bit位大小 | ||

| end_command | output | 1 | 命令结束信号 | ||

| end_command_and_response | output | 1 | 命令结束且反馈接收完成信号 | ||

| response_timeout | output | 1 | 响应超时信号 | ||

STATE_STOP:空闲状态,软件配置新的命令时,有效in_command_read位,状态机进入STATE_WAIT_SEND状态;

STATE_WAIT_SEND:命令发送等待状态,in_sd_data[0]低有效时,跳入STATE_SEND状态,否则保持

STATE_SEND:进行命令数据的发送,在所有48bit数据发送结束之后,进行in_response信号的判断,如果高有效,进入STATE_WAIT_RECEIVE状态,准备接受device返回数据。否则,进入

STATE_STOP状态,结束命令操作

STATE_WAIT_RECEIVE:如果device准备命令返回数据的时间超过64sd_clk,则硬件跳入STATE_STOP,并给出timeout信号。否则跳入STATE_RECEIVE状态;

STATE_RECEIVE:命令接收状态,结束后,返回STATE_STOP状态

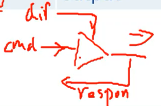

CMD状态机控制图

4.sd_cmd_send_shift_register模块: sd命令发送端口;

端口信号描述

| Singals | I/O | Width | declaration |

| in_sd_clk | input | 1 | 时钟信号 |

| hrst_n | input | 1 | 异步复位 |

| in_soft_reset | input | 1 | 软件复位 |

| in_current_state | input | [2:0] | cmd控制状态机标志位 |

| in_command_index | input | [5:0] | 待发送的命令 |

| in_command_argument | input | [31:0] | 待发送伴随命令的argument |

| in_has_send_bit | input | [5:0] | 已发送的命令bit位数 |

| in_TestMode | input | 1 | 测试模式 |

| out_sd_cmd | output | 1 | 命令输出端口 |

| out_cmd_dir(使能) | output | 1 | 命令线方向控制端口 |

因为CMD是三态双向输出,需要一个使能OEN。

因为CMD是三态双向输出,需要一个使能OEN。

◆功能描述:

(1)接收数据,转换成串行数据,送入命令线输出,其接口时序如下图所示:

(2)命令线的方向控制:默认为输入状态,只有在发送命令状态时(STATE_SEND)输出,

(3)产生CRC校验数据,并送入命令线输出。

5.sd_cmd_recrive_shift_register模块:sd命令返回端口;

| Singals | I/O | Width | declaration |

| in_sd_clk | input | 1 | 时钟信号 |

| in_soft_reset | input | 1 | 软件复位 |

| in_current_state | input | [2:0] | cmd控制状态机标志位 |

| in_serial_cmd | input | 1 | 命令输入端口 |

| in_has_receive_bit | input | [7:0] | 已接收的命令bit位数 |

| in_longresponse | input | 1 | Device有命令长回复信号 |

| out_cmd_receive_crc_error | output | 1 | 接收命令出错信号 |

| response0 | output | [31:0] | 命令返回信号寄存器0 |

| response1 | output | [31:0] | 命令返回信号寄存器1 |

| response2 | output | [31:0] | 命令返回信号寄存器2 |

| response3 | output | [31:0] | 命令返回信号寄存器3 |

◆功能:

- 接收卡返回的数据,转成并行数据,送入response0-3寄存器,供软件可读;

- 接收CRC数据,并和内部产生的CRC数据进行对比,判断数据接收是否出错(out_cmd_receive_crc_error),软件可查。

6.sd_data_fsm模块:数据操作控制模块,控制sd_data_send_shift_register和sd_data_recrive_shift_register模块;

数据发送/接收控制模块,根据输入的控制信号,进行状态机的跳转判定,以控制sd_data_send_shift_register和sd_data_recrive_shift_register模块进行符合SD协议的数据处理过程。

| Singals | I/O | Width | declaration |

| in_sd_clk | input | 1 | 时钟信号 |

| hrst_n | input | 1 | 异步复位 |

| in_soft_reset | input | 1 | 软件复位 |

| in_data_ready | input | 1 | 状态机启动信号 |

| in_sd_data | input | [3:0] | 数据读入信号 |

| in_data_direction | input | 1 | HOST读写控制信号->1:write 0:read |

| nend_to_receive_byte | input | [10:0] | 控制器每块需接收的数据量 |

| need_to_send_byte | input | [10:0] | 控制器每块需发送的数据量 |

| need_to_receive_block | input | [31:0] | 控制器需要多少块(接收) |

| need_to_send_block | input | [31:0] | 控制器需要多少块(发送) |

| in_data_width | input | 1 | HOST使用数据线判定信号 -> 1 or 4 data line |

| in_read_to | input | [31:0] | HOST读操作timeout(超时),状态机返回STOP状态 |

| current_state | output | [3:0] | 当前状态标志位 |

| next_state | output | [3:0] | 次状态标志位 |

| has_send_bit_counter_en | output | 1 | 不用输出 |

|

send_crc_counter | output | [3:0] | 已发送crc数据的bit大小,作为sd_data_send_shift_register模块的CRC输出控制信号 |

| has_receive_bit | output | [13:0] | HOST已发送的数据bit大小 |

| receive_crc_status_counter | output | [1:0] | 不用输出 |

| has_receive_bit | output | [13:0] | HOST已发送的数据bit大小 |

| out_transfer_complete | output | 1 | 数据传输结束状态标志位 |

|

interval_counter | output | [1:0] | 单块block写结束位时钟计数器,用于数据端口方向位的控制 |

| out_read_to_error | output | 1 | 读操作timeout标志位,ISR[6] == 1 |

| one_bk_re_end | output | 1 | 一个block数据读操作结束状态位,用于硬件停时钟 |

SD_DATA_FSM详述:

●STATE_STOP:停止状态,in_data_ready高有效时(写:sd_fifo_full,读:命令发送完),进入STATE_IDLE状态;

●STATE_IDLE:读写判断状态,in_data_direction高有效时,表示host准备开始发送数据,进入STATE_END_WAIT状态,反之,则表示host准备开始接收数据,进入RECEIVE_WAIT状态;

●STATE_WAIT_RECEIVE:读操作准备状态,首先判断已接收的数据块是否满足要求,若满足,则跳入STATE_STOP,状态机停止工作。若不满足,进行timeout判断,若等待时间超过软件定义的时间(in_read_to_),也返回STATE_STOP;状态机停止工作,并给出状态信号read_to_error。_最后,检查数据线data[0]是否低有效,有效则跳入STATE_RECEIVE状态,否则保持;

●STATE_RECEIVE:数据读操作处理过程,并需要判断每块byte数据是否读完(has_receive_bit==need_to_receive_bit-1),满足跳入STATE_RECEIVE_CRC状态,否则保持;

●STATE_RECEIVE_CRC:判断每块crc数据是否读完(receiv_CrC_counter==15),满足跳入STATE_RECEIVE_END_BIT状态,否则保持;

●STATE_RECEIVE_END_BIT:首先判断已接收的数据块是否满足要求,若满足,则跳入STATE_STOP,状态机停止工作。不满足,跳入STATE_WAIT_RECEIVE状态;

●DATA_STATE_WAIT_SEND:数据输出等待状态,在条件fifo已被写满情况下_,判断所有数据块是否发送完成,满足跳入STATE_STOP状态,状态机停止工作。否则进行data[0]数据的判断,高有效,跳入DATA_STATE_SEND状态,否则保持。

● DATA_STATE_SEND_Z :不做任何数据处理,进入DATA_STATE_SEND_P状态;

●DATA_STATE_SEND_P :总线方向改变状态

●DATA_SEND_START_BIT :开始数据发送状态,跳入STATE_SEND状态。

●STATE_SEND:数据发送状态,单块数据所有bit发送完成后(has_send_bit==need_to_send_bit-1) ,进入STATE_SEND_CRC,否则保持;

●STATE_SEND_CRC:CRC数据发送状态,完成后,跳入STATE_SEND_END_BIT;

●STATE_SEND_END_BIT:结束位发送状态,并用于数据线的方向切换(状态中间点),进入STATE_ RECEIVE_CRC_STATUS状态。

●STATE_RECEIVE_CRC STATUS :发送数据的CRC状态位接收状态,接收完成后,进入DATA_STATE_SEND_ BUSY状态;

●STATE_SEND_BUSY:数据块传输结束判断状态,所有block发送结束,跳入STATE_STOP状态,停止操作。否则,进入DATA_STATE_WAIT_SEND状态,等待下一次块数据传输的开始。

◆STATE_WAIT_RECEIVE状态和STATE_RECEIVE_END_BIT状态都进行已读取数据块的判断,但其作用却不相同:

●STATE_RECEIVE_END_BIT状态的判断,是正常情况下的操作,即软件配参数值need_to_receive_block之后,host硬件必须从device读取相等大小数据块。

●STATE_WAIT_RECEIVE状态的判断,是允许提前结束读操作。此状态内,软件修改参数need_to_receive_block(大小为has_receive_block+1),使得硬件状态机结束。

◆DATA_STATE_WAIT_SEND和STATE_SEND_BUSY状态都进行了已发送数据块的判断,意义同备注1相似

●STATE_SEND_BUS状态的判断,正常情况下的操作,即软件配参数值need_to_send_block之后,host硬件必须往device发送相等大小数据块。

●DATA_STATE_WAIT_END状态的判断,是允许提前结束写数据的操作,此状态内,软件修级数need_to_send_block(大小为has_send_block),使得硬件状态机结束。

Data数据的发送模块,根据sd_data_fsm模块状态机的状态,读取内部fifo数据和CRC数据,拆分成bit数据,送入data line。并根据接收的状态数据,判定一块数据发送是否正确。

| Singals | I/O | Width | declaration |

| in_sd_clk | input | 1 | 时钟信号 |

| hrst_n | input | 1 | 异步复位 |

| in_soft_reset | input | 1 | 软件复位 |

| in_sd_data | input | [3:0] | 数据读入端口 |

| sd_fifo_rdata |

| [31:0] | fifo数据读入端口 |

| in_current_state | input | [3:0] | 数据当前状态标志位 |

| in_next_state | input | [3:0] | 数据次状态标志位 |

| in_data_width | input | 1 | host使用数据线判定信号 -> 1/4 data line |

| in_send_crc_counter | input | [3:0] | Host已发送crc数据的bit大小 |

| in_has_send_bit | input | [13:0] | Host已发送的数据bit大小 |

| in_interval_conter | input | [1:0] | 单块block写结束位时钟计数器,用于数据端口方向位的控制 |

| in_high_speed_clk | input | 1 | 数据输出方式,1:高速0:低速 |

| out_serial_data | output | [3:0] |

|

| sd_fifo_re | output | 1 | fifo读请求信号 |

| out_crc_status_wrong | output | 1 | 数据发送crc校验错误 |

| out_data_dir | output | [3:0] | 数据方向控制端口 |

| out_data_half_delay | output | [3:0] | 数据输出端口(高速:上升沿低速:下降沿) |

| in_TestMode | input | 1 | 测试模式 |

7.sd_data_send_shift_register模块:sd数据发送端口;

◆功能:

数据线方向控制,根据状态信息,判定数据IO线是输入还是输出;

下图所示的是低速时钟下,host的数据发送和方向控制时序。在下降沿对输出的方向控制位寄存,得到下降沿输出数据;根据信号in_high_speed_clk(host是否工作在高速时钟情况),判定下降沿输出还是上升沿输出。

◆数据的输出:

(1)fifo数据的swap,fifo数据(word)是地址顺序存储的(the first byte is the least significant byte),但host数据的输出就是fifo数据左移出来的最高位,不符合SD协议,需要输出前进行4个byte的swap调整;

(2)读入fifo数据和模块生成的CRC数据左翼输出。

◆CRC数据的生成;

◆数据输出错误判定;

8.sd_data_recrive_shift_register模块:sd数据输入端口;

| Singals | I/O | Width | declaration |

| in_sd_clk | input | 1 | 时钟信号 |

| in_soft_reset | input | 1 | 软件复位 |

| in_current_state | input | [3:0] | 数据当前状态标志位 |

| in_serial_data | input | [3:0] | 数据读入端口 |

| in_data_width | input | 1 | Host使用数据线判定信号 -> 1/4 data line |

| in_has_receive_bit | input | [13:0] | Host已发送的数据bit大小 |

| sd_fifo_we | output | 1 | fifo写请求信号 |

| sd_fifo_wdata | output | [31:0] | fifo数据写入端口 |

| out_receive_data_crc_err | output | 1 | 数据读入数据crc校验错误 |

◆功能:

- 数据读入,并成一个word,swap,写入fifo;

- CRC数据读取,和内部生成的CRC数据作比较,以判定读入的数据是否出错,以out_receive_data_crc_err信号作为标志位。

3859

3859

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?