在Verilog测试方式中,即便只给设计提供时钟和复位信号,仿真也会一直持续(clk如同给仿真提供供血功能来保证设计可以正常跳动,rstn信号是为了让设计进入确定的状态),不会主动结束,这就需要Verilog系统函数主动暂停** s t o p ∗ ∗ → c o n t i n u e r u n 或者结束仿真 ∗ ∗ stop**→continue run或者结束仿真** stop∗∗→continuerun或者结束仿真∗∗finish**

仿真开始

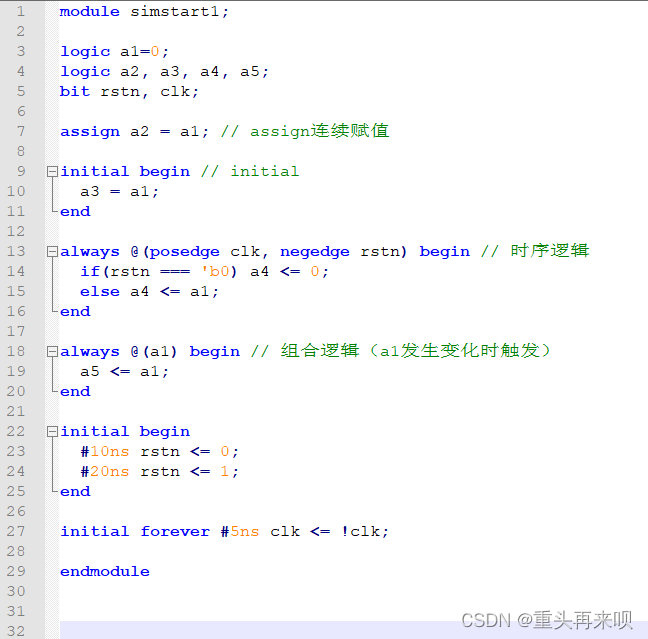

simsmart

simsmart代码

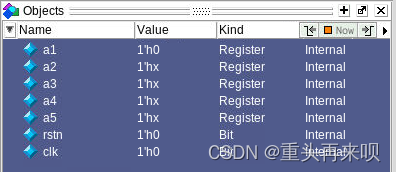

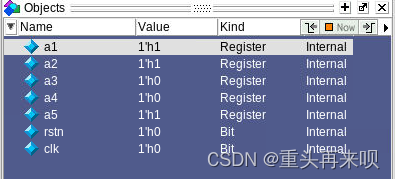

1.各变量初始值:a1已有初始值0,a2→a5为logic类型,默认初值为x,clk和rstn为bit型,默认初值为0

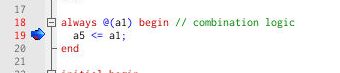

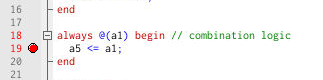

2.log -r /*保存波形,在19行设断点,然后run 0(一个Δcycle),看会不会进入19行

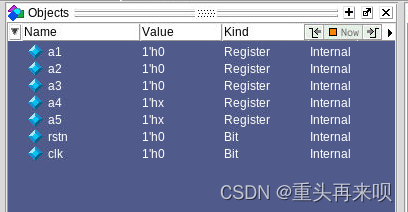

3.run 0,a2 a3被a1赋值(assign语句相当于用一根线把a1 a2连在一起,不管运行多短时间a1的变化能立即体现在a2上;initial语句也能在一个Δcycle时间内立即执行,将a1值赋给a3);13行敏感事件没被触发;没有进入19行(a1没有变化,没有触发initial执行条件)

4.modify a1:10ns后把1’h1赋给a1

5.run 20ns

6.10ns时在19行断点处停下,因为a1发生了变化

7.再run 0,通过断点,19行被执行,a5成功被a1赋值为1;a2被赋值为1,a3保持为0(initial只执行一次)

assign:在0时刻会执行一次; always:等到信号变化后才执行

仿真的结束

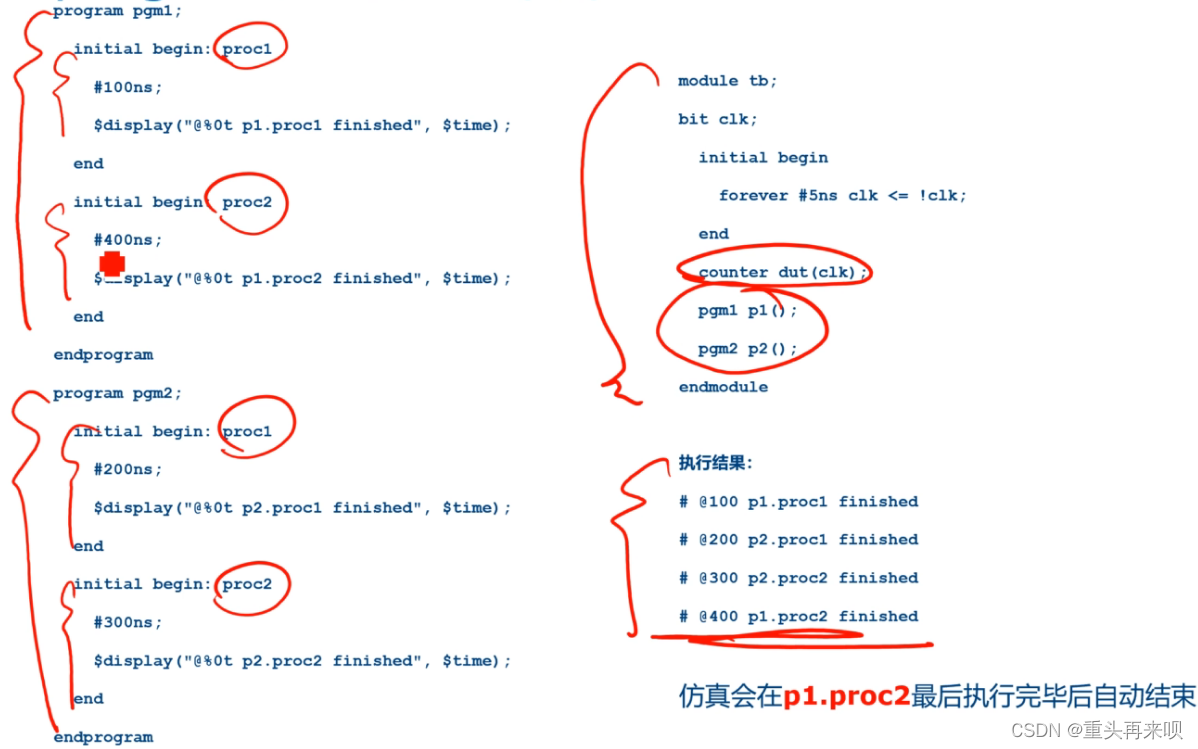

SV中推出program来将设计部分与验证部分分隔开:

program隐式结束:

如果tb中只有一个program,那么在此program的initial过程块执行完仿真会自动结束;

如果tb中有多个program,则仿真在所有program的最后一个initial过程块执行完后结束结束

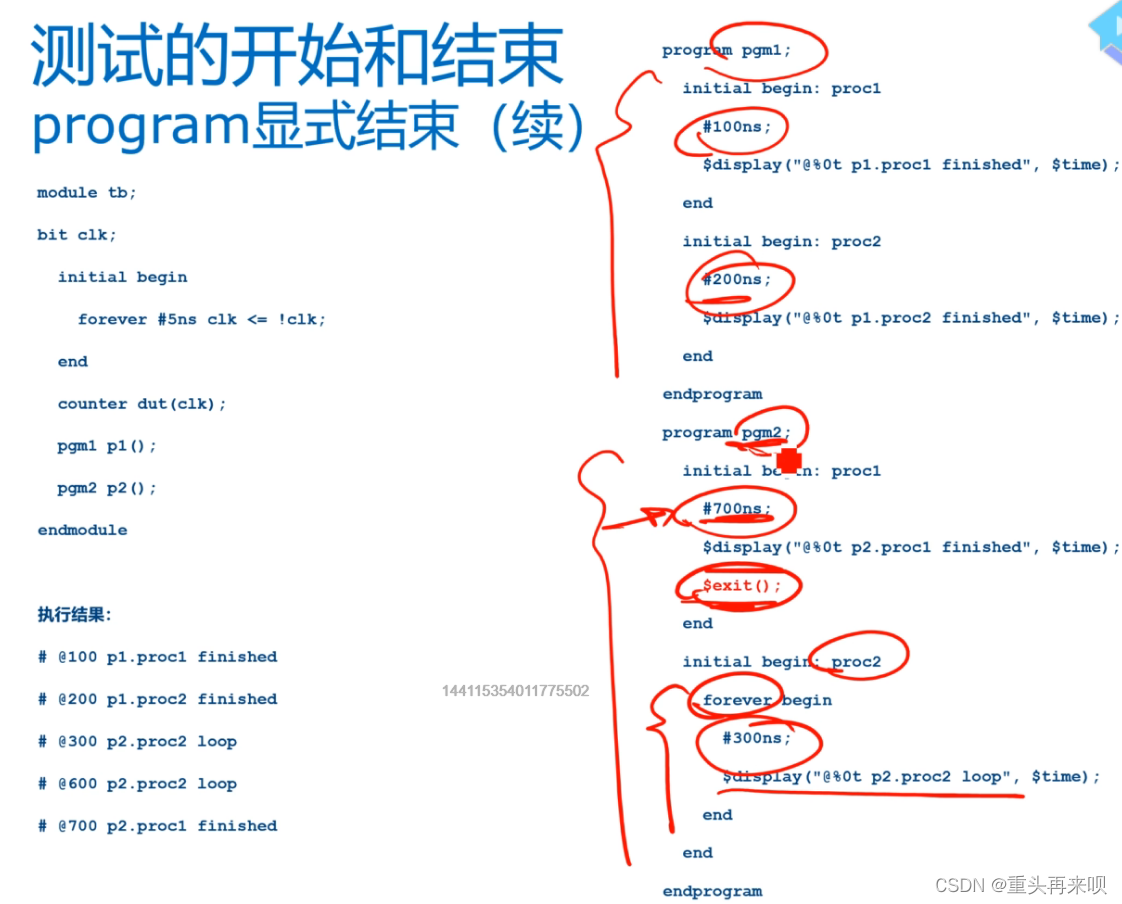

program显示结束:

在目标program中置入系统函数**$exit()**可将此program强行结束;

此program被强行结束后仿真器仍需等待其他program结束后再结束仿真

pgm2在700ns结束之后结束

使用program的要求和建议

- program是软件域,内部不能出现硬件域,如module always interface

- program不能例化program

- program内部定义变量采用阻塞赋值(软件方法)

- program驱动外部硬件信号采用非阻塞赋值(硬件方法)

设置断点

断点作用

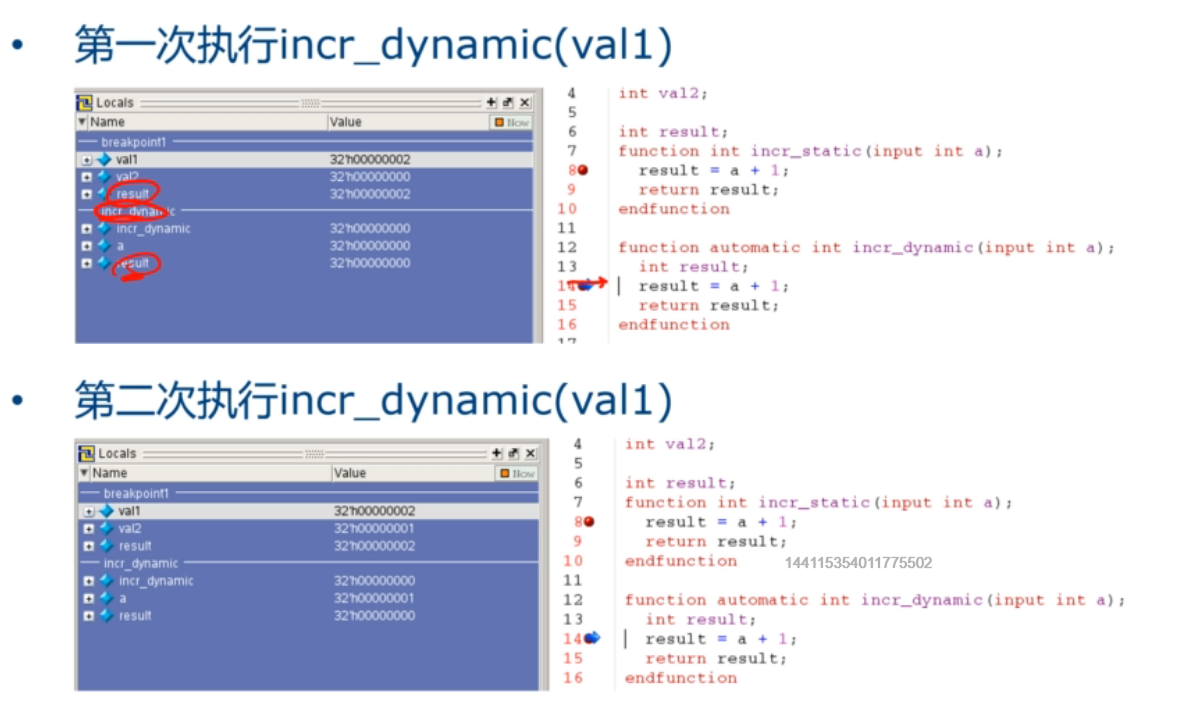

- 查看程序在执行到断点处(程序暂停执行)时的变量数值

- 软件部分变量(function task等) (动态变量)无法在波形窗口上显示,需借助断点来查看当前程序中的变量数值

- 调试程序执行的顺序比如设置了3个断点,在前两个断点都停下来了,但是在第三个断点没有停下来,这就说明,在第二个和第三个断电之间,没有顺利地执行到第三个断点

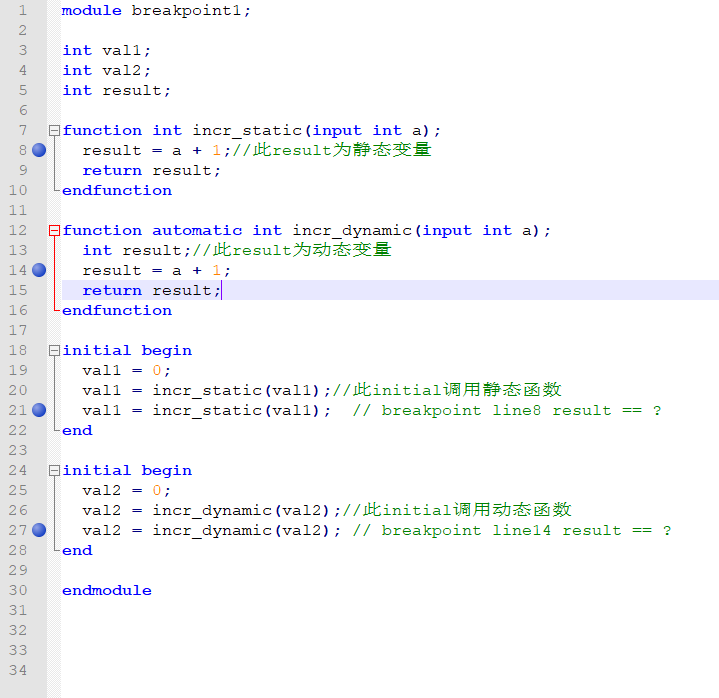

breakpoint代码

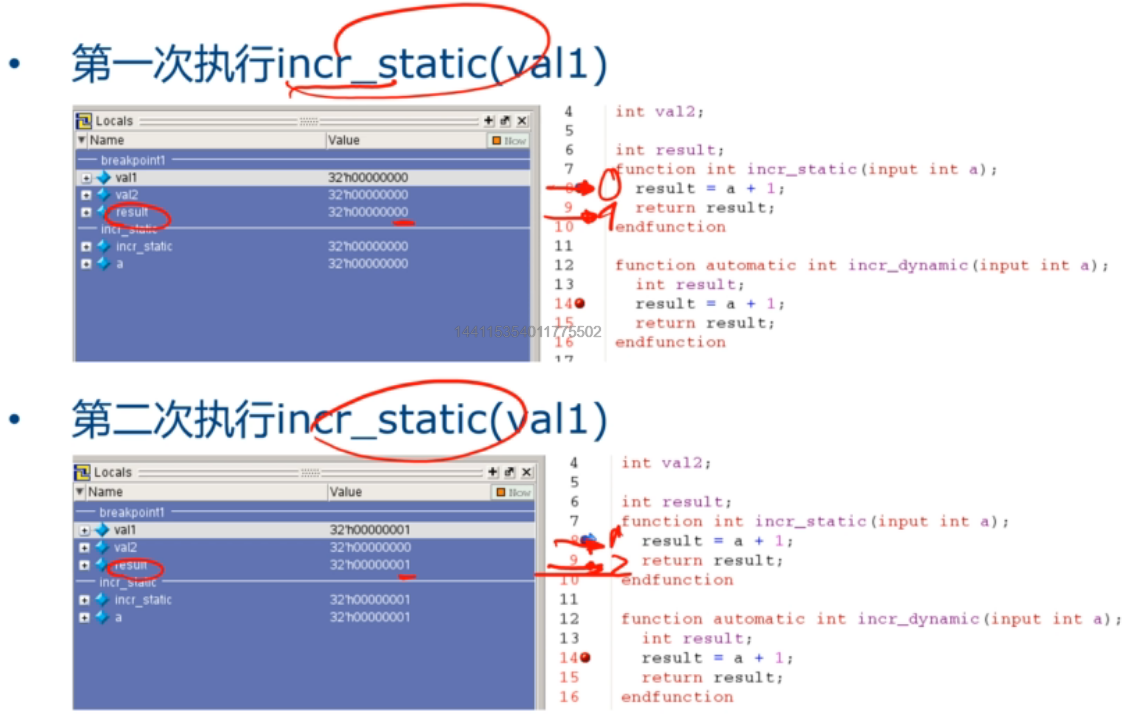

在8 14 21 27行设置断点,断点停在第八行表示断点的入口,刚停留在第八行但是第八行还没有执行结束;

执行结果如下图:

注:

没办法停在13行,因为13行是声明,不能执行;

local里面既可以显示动态的值,也可以显示静态的值,只不过更关心动态的值;object里面只能显示静态变量

2677

2677

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?