Vivado的安装以及使用

零. Vivado简要介绍

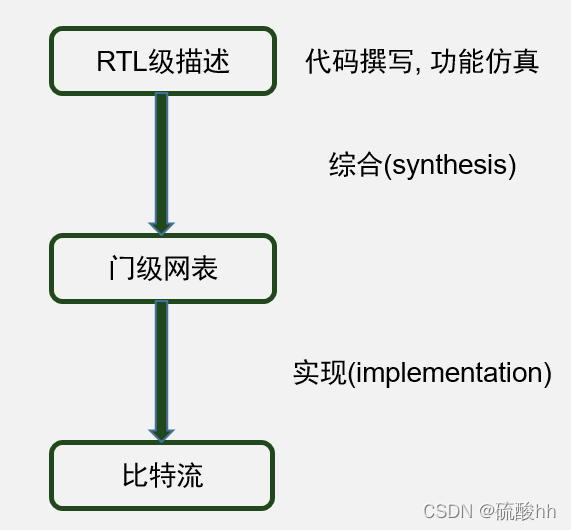

Vivado是FPGA厂商赛灵思提供的一款EDA(Electronic Design Automation)工具. 在电子设计自动化方面, 其主要提供了四种功能: RTL代码编写, 功能仿真, 综合(synthesis)以及实现(implementation).

- 其中, RTL代码编写用于编写设计的HDL描述(利用VHDL和System Verilog两种语言);

- 功能仿真用于测试编写出的代码功能是否符合预期, 需要编写相关的testbench文件;

- 综合用于讲RTL级描述转换为门级网表(门级网表是指设计的门级实现,包含门级元件和元件之间的连接, 从而更接近底层设计);

- 实现用于将门级网表转换为可以下载到FPGA开发板上的比特流.

| vivado在数字集成电路设计过程中的作用 |

|---|

一. vivado的安装

Vivado的安装已经有好多文章介绍过, 在这里给出一篇文章

https://blog.csdn.net/taowei1314520/article/details/74860356

二. 使用vivado完成一个小设计-计数器

在这里我们以一个4进制计数器的设计为例, 讲解我们如何使用Vivado进行工程设计

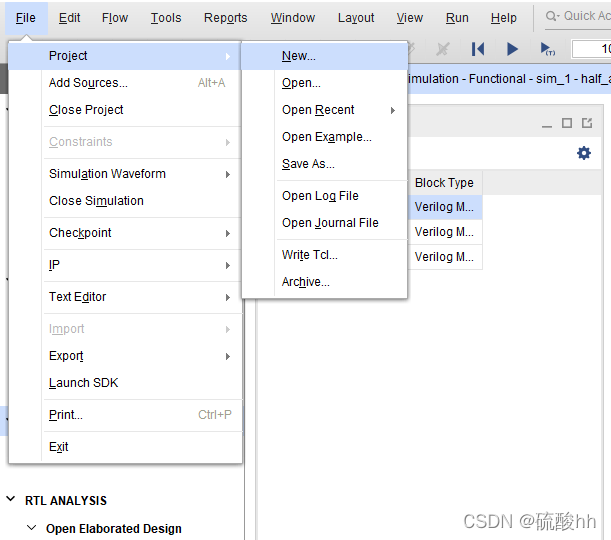

1. 新建工程

在菜单中点击file->project->new新建project

| 新建工程命令所在位置 |

|---|

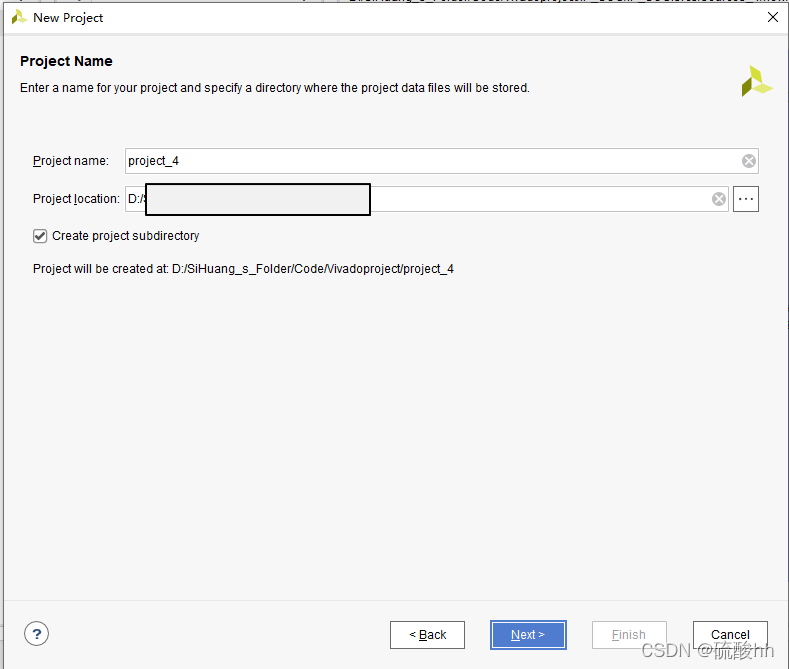

新建project的时候注意选择合适的存放路径, 然后点击next; 选择RTL Project, 点击next; 选择对应的开发板, 点击next; 点击finish, 完成工程的新建.

| 新建工程过程示意图 |

|---|

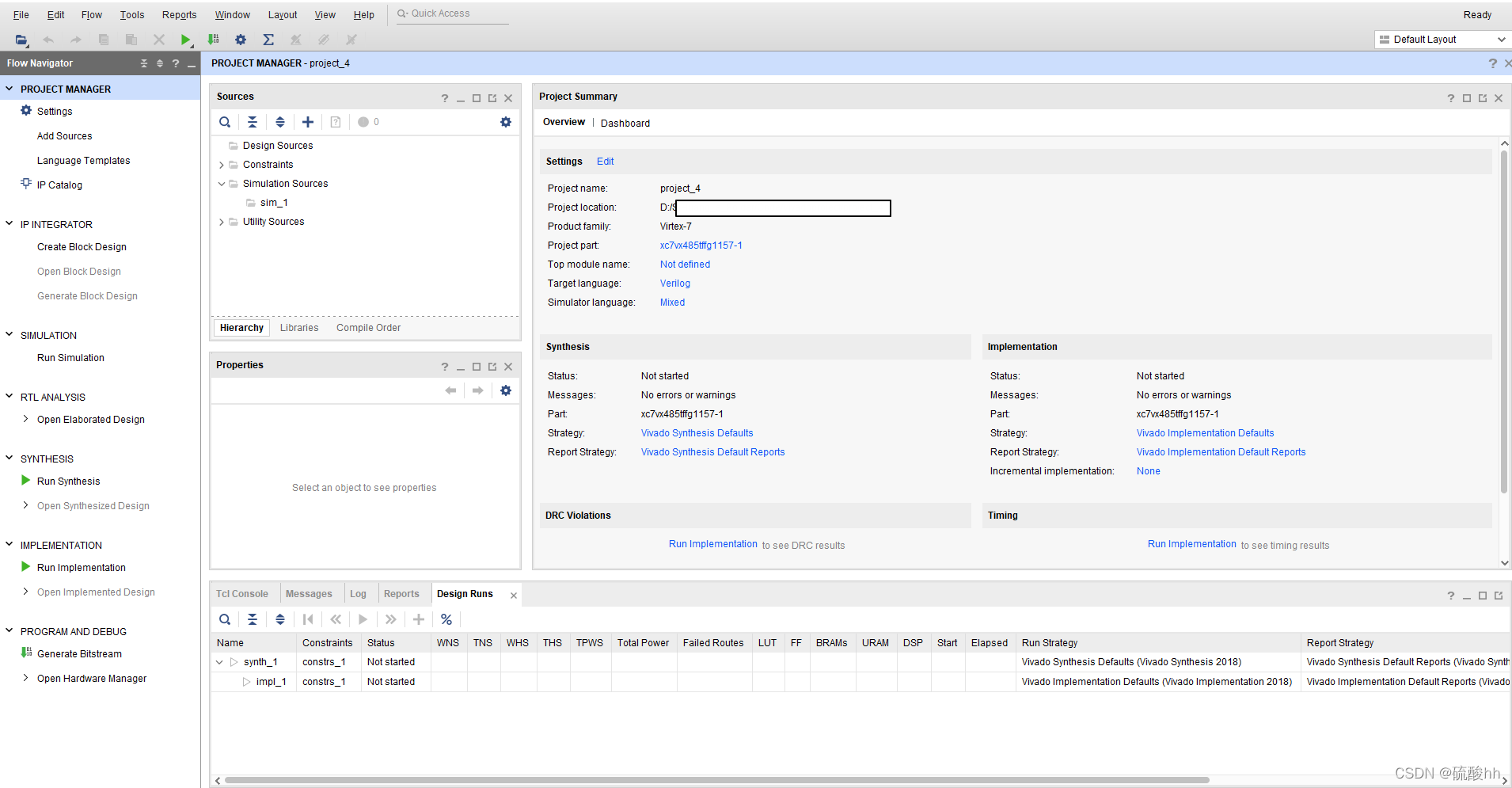

| 新建工程project 4 后的Vivado界面 |

|---|

- 新建设计文件

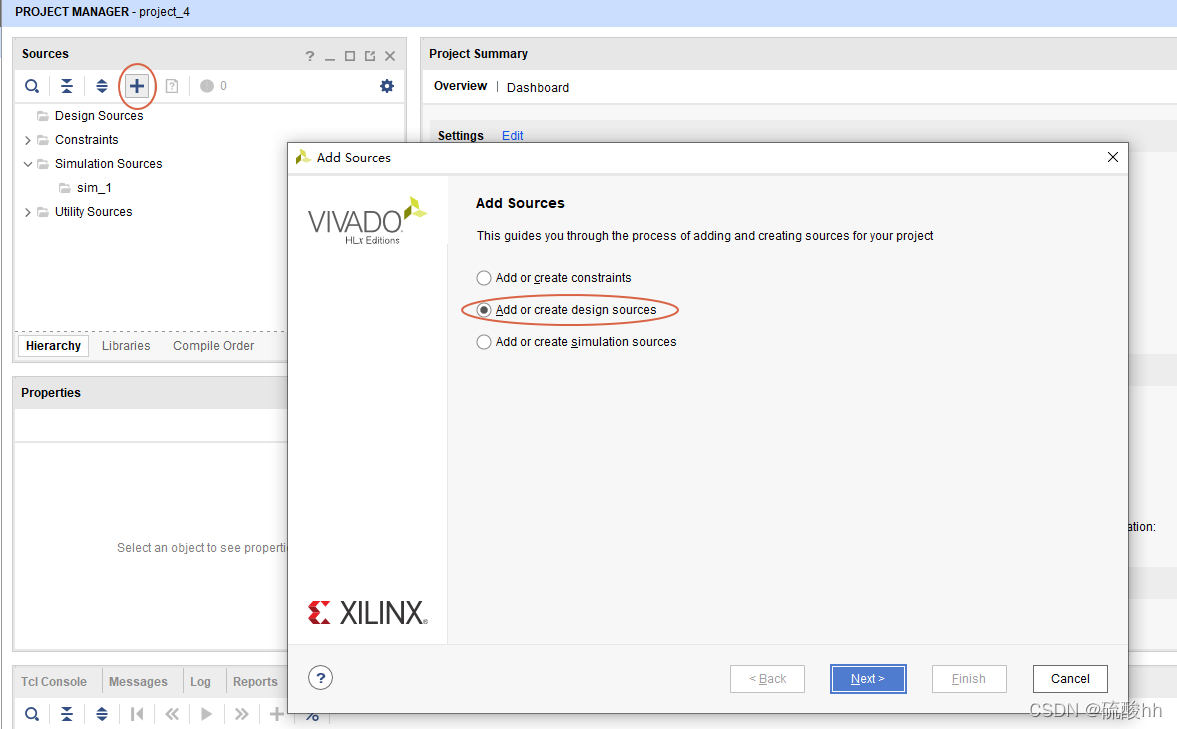

在界面中找到"Source"框, 点击"+", 选择"Add or create design sources", 点击next.

| 新建设计文件过程示意图一 |

|---|

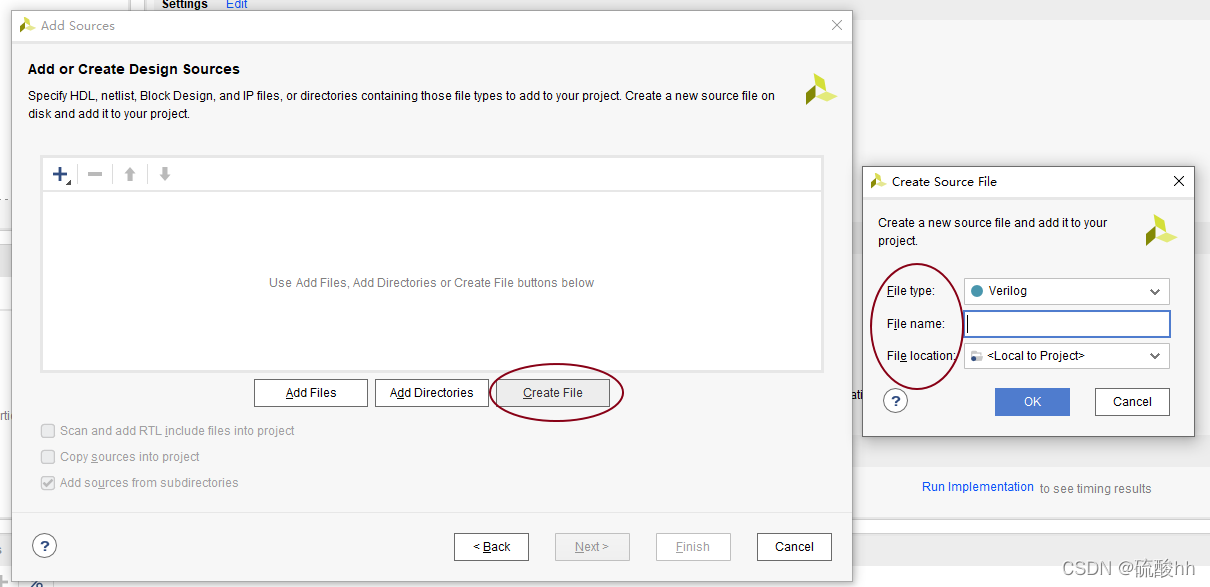

点击Creat file, 指定语言类型, 文件名字, 文件存放的位置, 完成设计文件的新建.

本文详述了Vivado的安装步骤及使用过程,包括创建RTL项目、设计4进制计数器、功能仿真、综合及实现。在Vivado中,通过编写HDL代码、测试仿真来验证功能,并最终生成可用于FPGA的比特流。同时,文中列举了在使用过程中可能遇到的问题及其解决方法。

本文详述了Vivado的安装步骤及使用过程,包括创建RTL项目、设计4进制计数器、功能仿真、综合及实现。在Vivado中,通过编写HDL代码、测试仿真来验证功能,并最终生成可用于FPGA的比特流。同时,文中列举了在使用过程中可能遇到的问题及其解决方法。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4530

4530

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?