作用:vivado调用VCS仿真可以加快工程的仿真和调试,提高效率。

前期准备:确认安装vivado软件和VCS软件

VCS软件最好安装VCS-MX的版本,可以混合编译Verilog和VHDL语言

由于在linux系统中个人用户各种权限被限制,导致很多地方无法正常使用软件之间的协调工作。

为了以防万一,在此以个人用户去实现vivado调用VCS仿真。

1、配置好个人用户下的.bashrc(只要运行cd命令即可到达该目录下(利用命令ll–la可查看该文件))。如图:

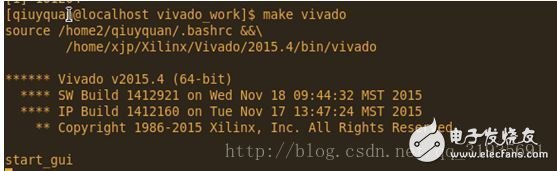

2、若因为服务器上的权限问题无法正常使用vivado,则可利用makefile命令打开vivado,在makefile中添加以下命令:(注意最后面不能跟空格键)

vivado:

source/home2/qiuyquan/.bashrc&&\

/home/xjp/Xilinx/Vivado/2015.4/bin/vivado

3、在终端makevivado命令打开vivado。如图:

4、打开vivado后设置VCS的路径。在工具栏打开Too

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3009

3009

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?