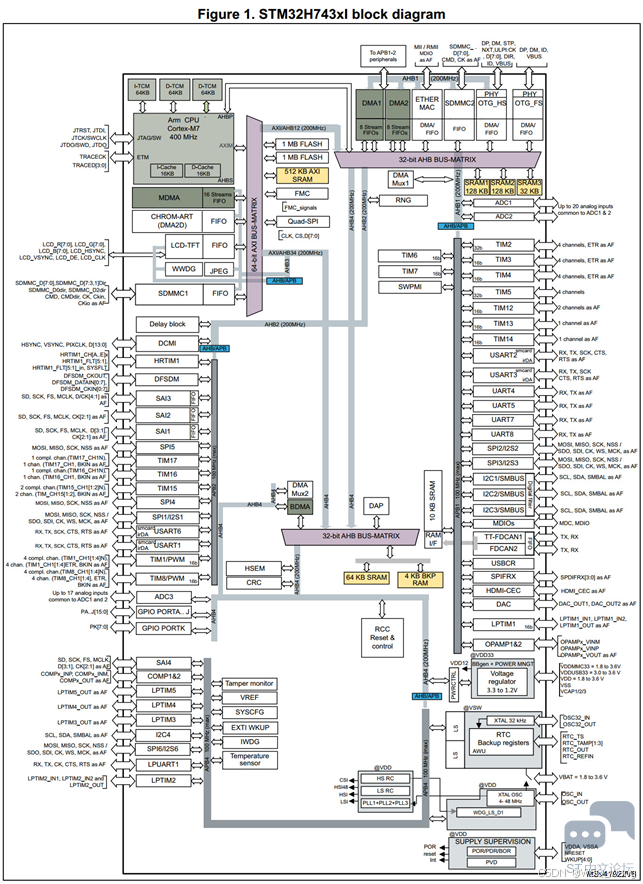

1、STM32H7硬件框图

学习一款芯片,需要优先了解一下它的整体功能设计STM32H743XIH6,直接在官方地址就可以看到对此芯片所做的介绍,页面中有一个如下的框图,对于了解STM32H7整体设计非常方便:

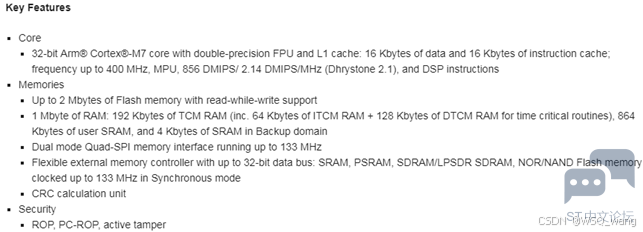

再稍微详细点,就需要大家读页面上的”Key Features”,就是下图所示的内容:

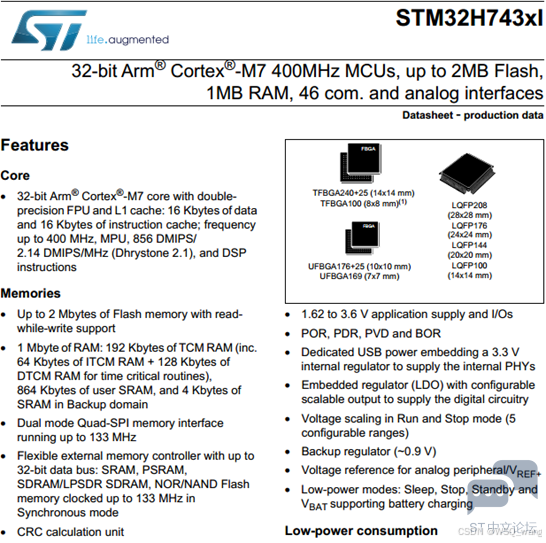

或者直接看数据手册开头的章节即可,也进行了介绍,内容基本都是差不多的,如下图所示(部分截图):

3.3 STM32H7各个型号的区别

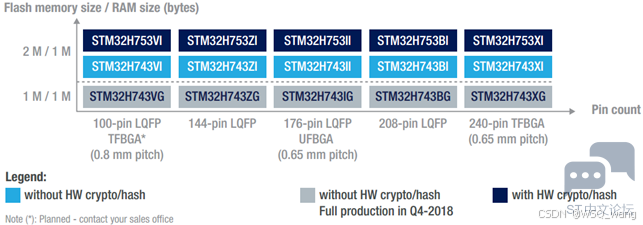

涉及到芯片选型的时候,需要大家了解各个型号的区别。对此ST有一个专门的文件STM32H7x3 MCUs High-performance line,在链接(这是一个超链接)里面可以找到。此文件里面有简单的对比,只是内容比较简单,仅两页,不过也言简意赅。最主要的是下面的这个截图:

通过这个截图可以方便地了解不同型号的引脚数、封装、FLASH大小、RAM大小以及是否带HW CRYPTO硬件加密的区别。

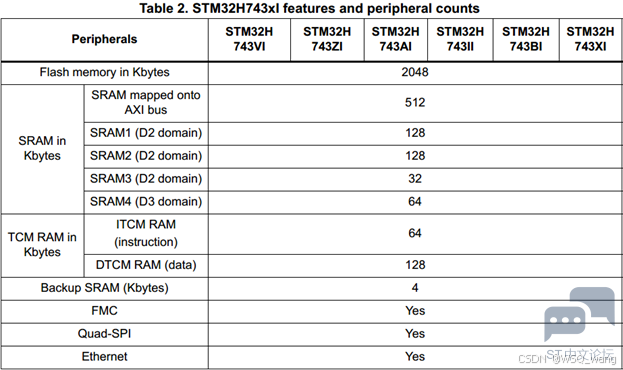

需要了解更详细的对比信息,可以看数据手册。任意下载一个型号的数据手册,在数据手册的的Table 2里面有详细的对比,如下图所示(部分截图):

3.4 STM32H7总线框图和时钟

STM32H7的数据手册里面提供了一张非常棒的框图,大家可以方便地查看每个总线的时钟速度和这个总线所挂的外设。这个在大家配置外设时钟分频的时候还是非常有用的,因为外设的时钟分频就是建立在所挂的总线速度

比如我们想得到不同定时器的主频,通过上面的框图,可以方便地获得如下信息:

SYSCLK(Hz) = 400000000 (CPU Clock)

HCLK(Hz) = 200000000 (AXI and AHBs Clock)

AHB Prescaler =

D1 APB3 Prescaler = 2 (APB3 Clock 100MHz)

D2 APB1 Prescaler = 2 (APB1 Clock 100MHz)

D2 APB2 Prescaler = 2 (APB2 Clock 100MHz)

D3 APB4 Prescaler = 2 (APB4 Clock 100MHz)

因为APB1 prescaler != 1, 所以 APB1上的TIMxCLK = APB1 x 2 = 200MHz;

因为APB2 prescaler != 1, 所以 APB2上的TIMxCLK = APB2 x 2 = 200MHz;

APB4上面的TIMxCLK没有分频,所以就是100MHz;

APB1 定时器有 TIM2, TIM3 ,TIM4, TIM5, TIM6, TIM7, TIM12, TIM13, TIM14,LPTIM1

APB2 定时器有 TIM1, TIM8 , TIM15, TIM16,TIM17)

APB4 定时器有 LPTIM2,LPTIM3,LPTIM4,LPTIM5

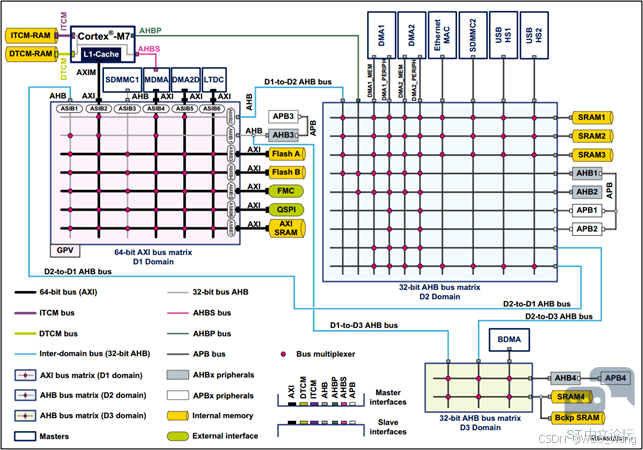

3.5 STM32H7的AXI线

AXI线在STM32H7中有着举足轻重的作用。高并发性全靠这个总线了,先来看下A**线的框架:

3.5.1 总线系统框架

下面这个截图比较有代表性,可以帮助大家理解STM32H7总线系统。

这个图可以方便识别总线所外挂的外设,共分为三个域:D1 Domain,D2 Domain和D3 Domain。

D1 Domain;

D1域中的各个外设是挂在64位A**线组成6*7的矩阵上。

6个从接口端ASIB1到ASIB6

外接的主控是LTDC,DMA2D,MDMA,SDMMC1,AXIM和D2-to-D1 AHB 总线。

7个主接口端AMIB1到AMIB7

外接的从设备是AHB3总线,Flash A,Flash B,FMC总线,QSPI和AXI SRAM。另外AHB3也是由A**线分支出来的,然后再由AHB3分支出APB3总线。

D2 Domain

D2域的各个外设是挂在32位AHB总线组成109的矩阵上。

10个从接口

外接的主控是D1-to-D2 AHB 总线,AHBP总线,DMA1,DMA2,Ethernet MAC,SDMMC2,USB HS1和USB HS2。

9个主接口*

外接的从设备是SRAM1,SRMA2,SRAM3,AHB1,AHB2,APB2,APB3,D2-to-D1 AHB总线和D2-to-D3 AHB总线。

D3 Domain

D3域的各个外设是挂在32位AHB总线组成3*2的矩阵上。

3个从接口

外接的主控D1-to-D3 AHB总线,D2-to-D3 AHB总线和BDMA。

2个主接口

外接的从设备是AHB4,SRAM4和Bckp SRAM。另外AHB4也是这个总线矩阵分支出来的,然后再由AHB4分支出APB4总线,这三个域之间也是有互联的,

D2域到D1域的D2-to-D1 AHB bus

允许D2域中的主接口外设访问D1域里面的从接口外设。比如D2域里面的DMA2访问D1域里面的AXI SRAM。

D1域到D3域的D1-to-D3 AHB bus

允许D1域中的主接口外设访问D3域里面的从接口外设。比如D1域里面的DMA2D访问D3域里面的SRAM4。

D2域到D3域的D2-to-D3 AHB bus。

允许D1域中的主接口外设访问D2域里面的从接口外设。比如D2域里面的DMA2访问D3域里面的SRAM4。

3.5.2 AXI线特色

AXI支持高频率、高性能的系统设计:

支持高带宽,低延迟设计。

提供高频操作,无需复杂的总线桥。

满足各种组件的接口需求。

适用于具有高初始访问延迟的内存控制器。

为互连架构的实现提供了灵活性。

与现有的AHB和APB接口向后兼容。

AXI线的关键特性:

独立的地址、控制和数据线。

支持非字节对齐方式传输。

基于起始地址的突发传输。

分开的读和写数据通道,且提供DMA传输。

支持发起多个地址。

支持无序传输。

允许添加寄存器,以提供时序收敛。

796

796

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?