本文讨论Verilog HDL与综合相关的问题。

一、赋值

本节讨论如何在Verilog中的实现不同的赋值,以及它们在逻辑综合中会推断出什么样的电路。

1.1、当对同一个net,使用多个assign语句,会综合出什么样的逻辑?

在可综合的verilog代码中,为同一个net使用多个assign语句是错误的。综合工具会报出语法错误,即“net is being driven by more than one source”。 例如,以下是错误的:

//only one type of output assignment is legal for synthesis

wire tmp ;

assign tmp = in1 & in2 ;

assign tmp = in1 | in2 ;但是,使用多个assign来驱动三态net 是合法的语句,如下示例所示:

input enable1 , enable2 ;

wire tmp ;

assigm tmp = (enable1 == 1’b1) ? (in1 & in2) : 1’bz ;

assigm tmp = (enable2 == 1’b1) ? (in3 & in3) : 1’bz ;1.2、条件赋值在逻辑综合时会推断出什么电路?

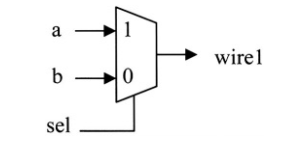

条件赋值通过“?:”实现。条件赋值在逻辑综合时被推断为MUX。 例如,以下示例是一个简单的MUX:

wire wire1 ;

assign wire1 = (sel == 1’b1) ? a : b ;

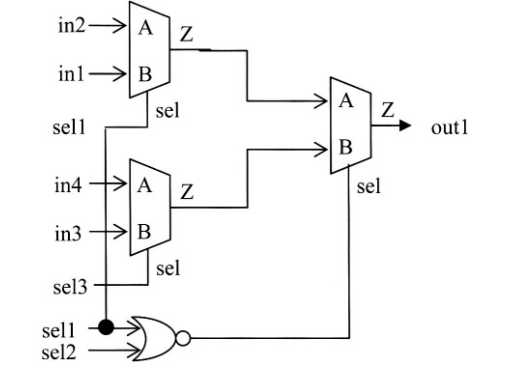

1.3、条件赋值嵌套会综合出什么样的电路?

如下例所示,条件赋值嵌套会被综合成MUX “tree ”:

assign out1 = (sel1 == 1’b1) ? in1 :

(sel2 == 1’b1) ? in2 :

(sel3 == 1’b1) ? in3 :in4 ;

1.4 在同一个always语句块中,对同一个reg变量多次赋值会综合出什么电路 ?

在同一个always语句块中,对同一个reg变量进行多次非阻塞赋值时,逻辑综合时会选择最后一个赋值。 例如:

module lower(clk ,in1 ,in2 ,out2) ;

input clk ,in1 , in2 ;

outout out2 ;

reg tmp ;

always@(posedge clk) begin

tmp <= (in1 ^ in2) ;

tmp <= (in1 & in2) ;

tmp <= (in1 | in2) ;

end

assign out2 = tmp ;

endmodule

在刚刚的示例中,OR逻辑是最后一个赋值。因此,综合出来的逻辑是OR门。 如果最后一个赋值是“&”运算符,它会综合成一个AND逻辑。

对于组合逻辑中always语句块中的阻塞赋值来说,情况也是如此。

always@(in1 , in2) begin

tmp = (in1 & in2) ;

tmp = (in1 ^ in2) ;

tmp = (in1 | in2) ; // The final logic picked up is the OR gate

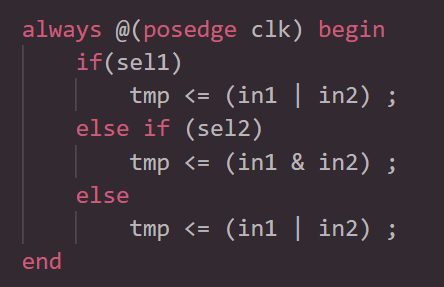

end如果多次赋值存在于if-else或case语句中。 例如,

在这种情况下,在每个时钟周期仅执行一个唯一的赋值。

在上面的例子中,没有关于哪个语句会被执行赋值的歧义,因为分支控制是明确定义的。

1.5 为什么时序逻辑应该用非阻塞赋值,如果用阻塞赋值会发生什么?并且与组合逻辑进行比较。

阻塞赋值和非阻塞赋值之间的主要区别是阻塞赋值中的RHS会被立即赋值到LHS,而非阻塞赋值,LHS的赋值是发生在RHS值被计算之后。

以下说明了在时序逻辑中使用阻塞赋值和非阻塞赋值的不同场景:

1.5.1 在时序逻辑中使用阻塞赋值

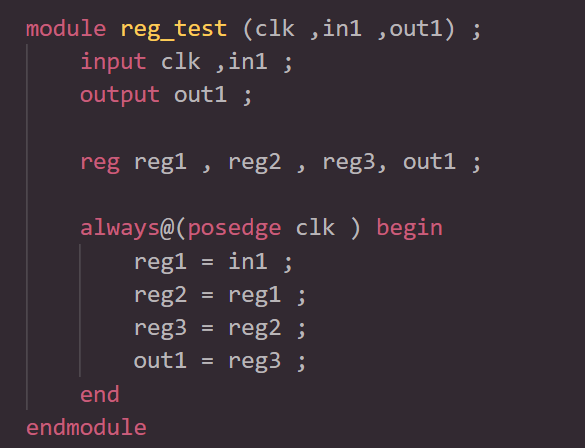

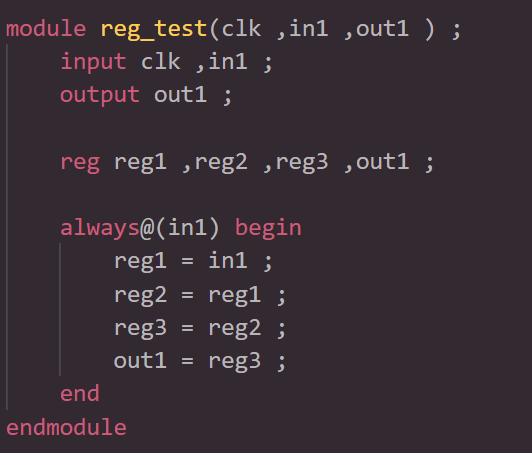

以下是时序逻辑中使用阻塞赋值的Verilog模块示例:

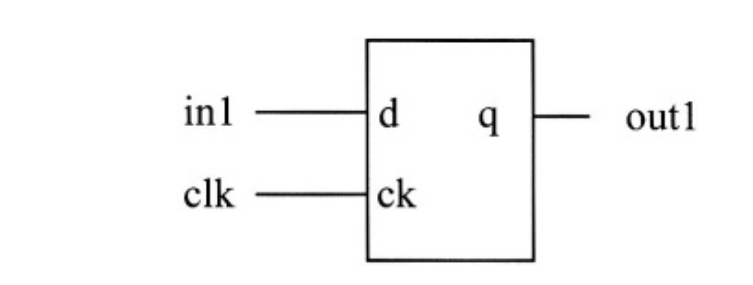

在上面的例子中,reg1,reg2,reg3,out1都是阻塞赋值。 综合结果是单个FF触发器,输入为in1,q输出为out1,如图下图所示:

这是因为in1和out1之间的中间结果是以阻塞赋值形式存储在reg1,reg2和reg3中。 结果,对out1的RHS最终计算会被立即赋值到out1, reg1,reg2和reg3已经通过综合进行了优化。

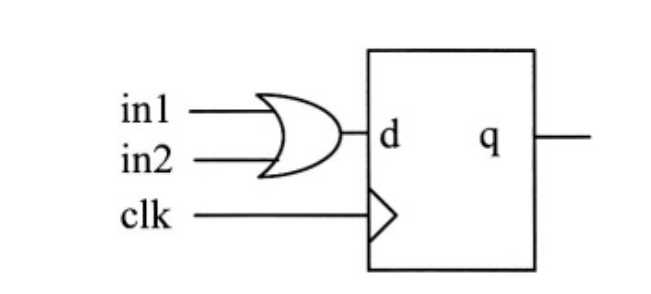

1.5.2 在时序逻辑中使用非阻塞赋值

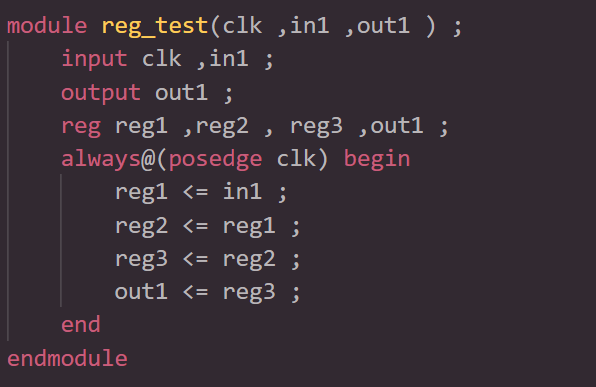

以下代码示例了时序逻辑中使用非阻塞赋值:

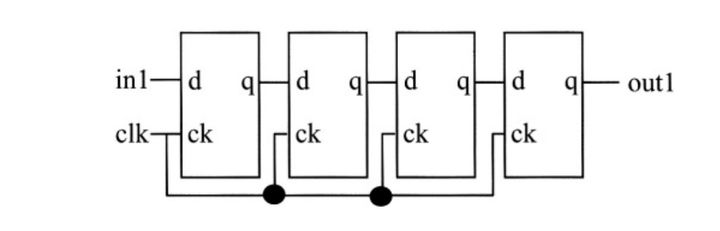

在上面的例子中,reg1,reg2,reg3,out1为非阻塞赋值。 综合结果为4个触发器。

这是因为in1和out1之间的中间结果是以非阻塞赋值存储在reg1,reg2和reg3中。在这种情况下,输出是由clk事件控制的移位寄存器。

1.5.3 在组合逻辑中使用阻塞赋值

以下示例说明了组合逻辑中的阻塞赋值的用法:

在上面的使用阻塞赋值的组合逻辑语句中,没有posedge,并且“<=”被“=”替换。 由此综合的逻辑很简单,是in1到out1之间的连线。

这是因为所有的赋值都是立即执行的,没有需要等待的事件。

2、Tasks 和Functions

Tasks 和 functions主要是有助于代码的可重用性。

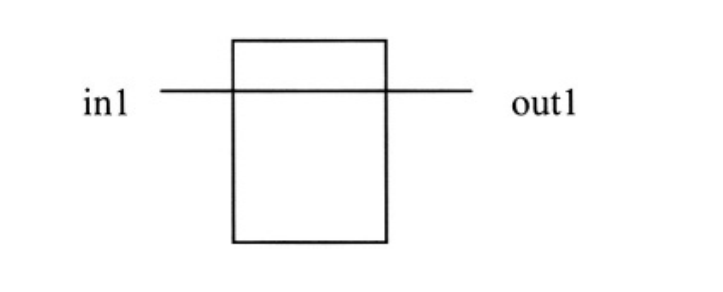

2.1 function中的逻辑被综合成了什么?

由于function中没有任何时序结构,function只能综合出组合逻辑。

例如,以下function有2个输入信号和一个控制信号,输出算术运算结果。

2.2Verilog function有哪些重要的注意事项?

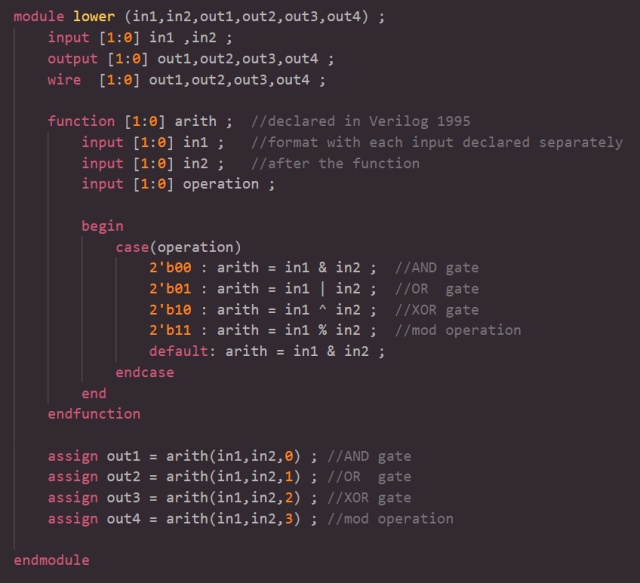

2.2.1 每次调用function时,局部变量和返回值应该是都会被赋值,否则将导致形成锁存器。 例如,以下示例中,if条件语句没有else语句。也就是说,如果sel是false,该function将返回其先前调用的值,就好像结果被锁存住了。

2.2.2 fucntion只用于综合成组合逻辑。但是,fucntion的最终结果可以用作D触发器的输入。

2.2.3 fucntion不应包括延迟(#)或事件控制(@,wait)语句。

2.2.4 fucntion可以调用其他fucntion,但不能调用task。

2.2.5 fucntion在调用时会返回一个值。

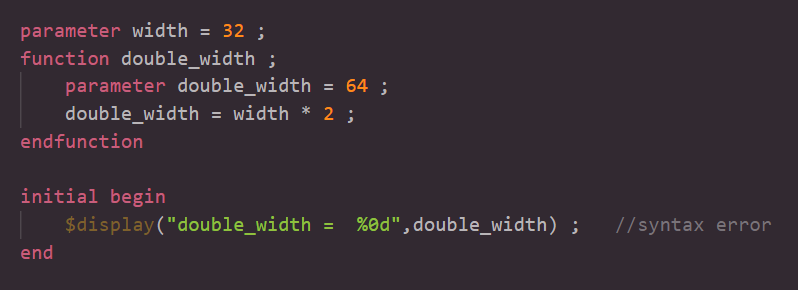

2.2.6 fucntion内声明的parameters,作用范围仅在本地,并且不能在fucntion之外使用。 在以下示例中,width参数在函数之外声明,double_width参数在函数内声明。

2.3 task中的逻辑被综合成了什么?

虽然在task中可以有@等时序控制结构中,它仅适用于仿真。综合工具会忽略所有task中的时序结构。因此,如果task中存在时序控制结构,可能会存在仿真和综合不匹配的现象。

因此,在可综合verilog中一般只会使用task综合基本的组合逻辑,在testbench中调用带有时序控制结构的task具有较好的通用性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1092

1092

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?