注:本文为《可靠性工程师手册(第二版)》的学习笔记。关注公众号,对话框回复“可靠性试验”获取本课程PPT课件。

一、定时截尾试验方案

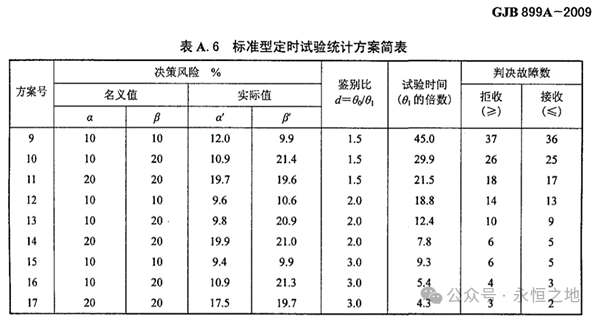

定时截尾统计试验方案是根据使用方风险、生产方风险、θ1及鉴定比确定试验方案时间T和实验中允许的责任故障数。当总试验时间T达到选定方案所对应的试验时间时,若试验中出现的责任故障数≥拒收的判决故障数Re,则做出拒收判决;若试验中所出现的责任故障数≤接收故障数Ac,则做出接收判决。

θ1为所验证产品的可靠性指标中MTBF的最低可接受值。

分为标准型方案和短时高风险两种,标准型试验方案采用正常的生产方风险和使用方风险,为10%-20%。短时高风险生产方和使用方风险为30%

例:某产品已知MTBF最低可接收受值θ1=300h,d=3,α=β=20%, 试设计一个定时截尾可靠性鉴定试验方案

解:查表可知,满足d=3,α=β=20%的试验方案为方案17。可得定时截尾可靠性鉴定试验方案为:(a) 总试验时间T=4.3θ1=4.3×300=1290(台时)。(b) 接收责任故障数r≤2,拒收责任故障数r≥3。

因此该产品的可靠性定时截尾的试验方案为:预定总试验时长为T=1290(台时)。当试验停止时出现的故障数≤2,则认为该产品可靠性合格,接收;当累积时间未达到T,故障数≥3,则停止试验,认为产品的可靠性不合格,拒收。

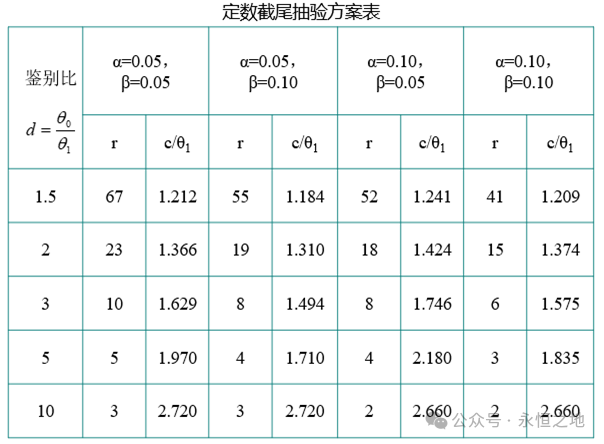

二、定数截尾试验方案

从一批产品中,随机抽取n个样品,当试验到事先规定的截尾故障数r时,停止试验,r个故障的故障时间分别为:t1≤t2≤…≤tr,则抽验规则为:当θ≥c时产品批合格,接收;当 θ<c时产品批不合格,拒收;其中c为合格判定数。

例:某产品生产方风险与使用方风险相同,均取α=β=0.1,并已确定θ1=200h,θ0=1000h,试确定一个定数截尾抽验方案。

解:根据d=θ0/θ1=5,α=β=0.1,查表得:r=3,c/θ1=1.835,则c=1.835×200=367(h)。

由此得方案为:截尾故障数r=3,合格判定数c=367h。即任取n个产品(无替换n>4) ,试验到r=3时,停止试验,

计算θ,判断:若θ≥367h时,接收; θ<367h时,拒收

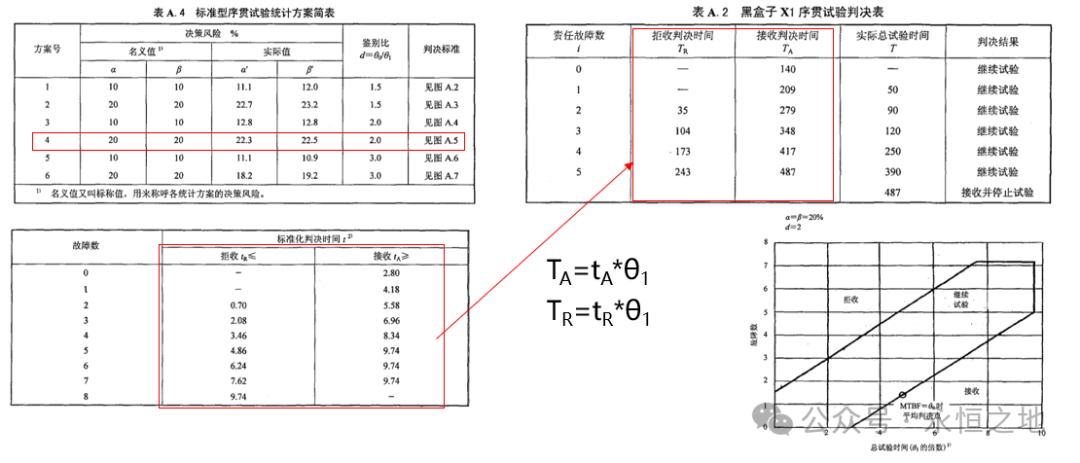

三、序贯截尾统计试验

例:飞机用黑盒子X1的可靠性验收试验。订购方同意的可靠性验收试验条件是若MTBF的真值θ=θ1=50h时,以1- β =80%的概率接收该批黑盒子,若MTBF的真值θ=θ0=100h时,以1- α=80%的概率接收该批黑盒子。采用序贯试验统计方案,要求最少试验3台。

验收条件得知α=β=0.2,鉴别比d=100/50=2,查表A.4知采用方案4。根据图A.5方案4的判决标准将标准化判决时间t乘以θ1(50h),得出接收判决时间TA和拒收判决时间TR,并将其与实际总试验时间T列入下表进行比较。实际试验中在总试验时间T=50、90、120、250、390台时时发生责任故障。每一故障出现时,将T与TA、TR进行比较。由于T均介于TA与TR之间,因此作出继续试验的判决。试验进行到487台时未出现新的责任故障,从而作出接收判决, 停止试验。黑盒子X1序贯试验判决表如表A2所示。

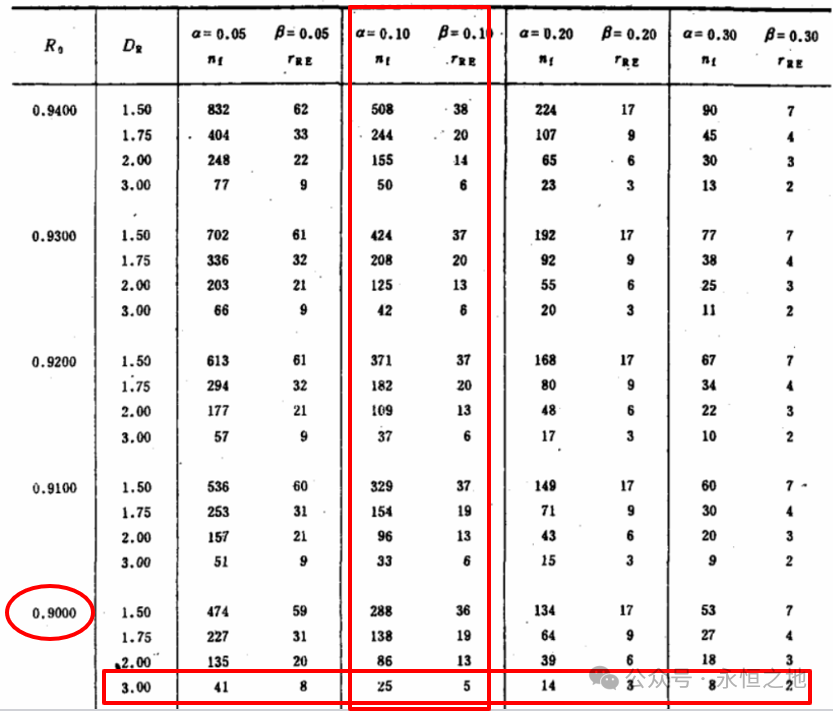

四、二项分布统计试验方案

服从二次分布的产品可靠性试验,称为成败型统计试验方案。一般有两种方案可以选择:定数试验方案和序贯试验方案。见GB5080.5《设备可靠性试验成功率的验证试验方案》

一般来说,典型的成败型试验方案的思路如下 随机抽取一个样本量为n的样本进行试验,其中有r个失败。规定合格判断数Ac和不合格判断数Re如果,r≤Ac,认为批产品可靠性合格,可接收 如果,r≥Re,认为批产品可靠性不合格,拒收。

Ac=Re-1

鉴别比:Dr=(1-R1)/(1-R0)

R0:可接受的可靠度或成功率,R1:不可接受的可靠度或成功率

例:已知某成败型产品的可接受的可靠度R0=0.9,鉴别比DR,取双方风险α=β=10%,试设计一个定数截尾试验。

解:根据R0=0.9,DR=3, α=β=10%,查GB5080.5规定的试验方案表(见下一页)得:样品数25,拒收数Re=5,接收数Ac=Re-1=4

2124

2124

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?