74HC161计数器仿真示例

- Proteus仿真

分别演示十六进制计数和十进制计数。

上面所演示的采用的是MR低电位复位来做

清零动作。

74HC161简介

- 74HS161是异步清零,只要在清零输入端MR输入低电平,立即清零。

74HC161异步复位的高速 CMOS 逻辑 4 位二进制计数器。采用异步二进制计数器在做加法计数时是以从低位到高位逐位进位的方式。因此,其中的各个触发器不是同步翻转的。按照二进制加法计数规则,第i位如果为1,则再加上1时应变为0,同时向高位发出进位信号,使高位翻转。

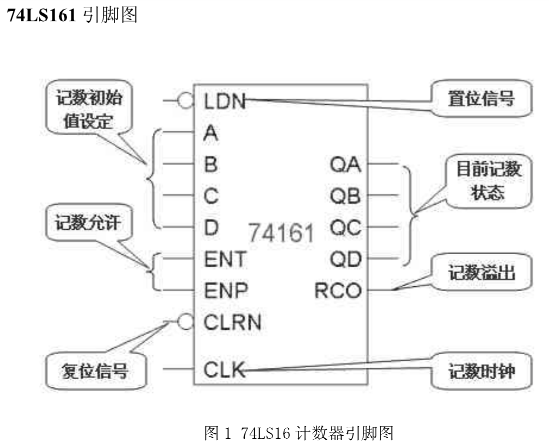

引脚功能介绍

74LS161的各引脚功能介绍如下;

- LDN:置数端,低电平有效,其同步置数,即使该输入为低电平,其输入的状态并不反映到输出端,而是等到CP上升沿时输出才发生变化;

- CLRN:清零端,低电平有效,其为异步清零,即该输入为低电平时,无论当时的时钟状态及其他输入状态如何,其输出端变为零,即QAQBQCQD=0000;

- ENT、ENP:工作状态控制端;

- QA、QB、QC、QD:计数器的输出端,其中QD为最高位,QA为最低位;

- A、B、C、D:计数器预置输入,通过置数端可将其输入状态反映在输入端;

- RCO:进位输出,当计数器满一个周期其输出一个高电平;

- CLK:时钟输入端,其为上升沿有效。

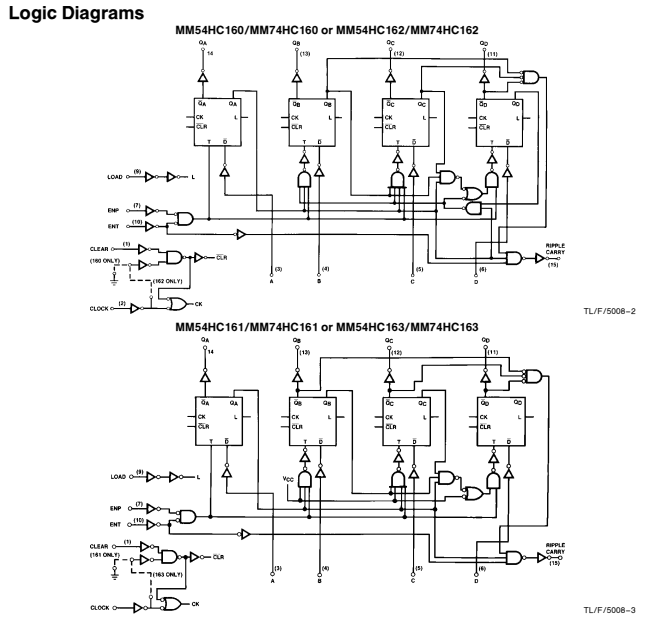

74LS161计数器内部逻辑图

74LS161电路状态转换表

仿真资源和数据手册

链接:https://pan.baidu.com/s/1Zj9JHv4X4C-VXDtrwNQfXw

提取码:wia2

| 与禽兽搏斗的三种结局:1.赢了,比禽兽还禽兽;2.输了,禽兽不如;3.平了,跟禽兽没两样。结论:选择正确的对手最重要! |

|---|

本文详细介绍了74HC161计数器在Proteus软件中的仿真过程,展示了其在十六进制和十进制计数的应用。74HC161是一款异步清零的高速CMOS逻辑4位二进制计数器,具有LDN、CLRN等控制端口,可用于实现不同计数模式。文中还提供了计数器的内部逻辑图和状态转换表,并给出了相关资源链接供读者深入研究。

本文详细介绍了74HC161计数器在Proteus软件中的仿真过程,展示了其在十六进制和十进制计数的应用。74HC161是一款异步清零的高速CMOS逻辑4位二进制计数器,具有LDN、CLRN等控制端口,可用于实现不同计数模式。文中还提供了计数器的内部逻辑图和状态转换表,并给出了相关资源链接供读者深入研究。

2508

2508

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?