MOSFET是一种常见的功率器件,广泛应用于电力电子领域。然而,MOSFET在高电压和高频工作环境中容易遭遇雪崩击穿和dV/dt失效,这些问题如果未能有效应对,可能导致设备的严重损坏。

一、雪崩击穿现象及其失效机制

- 雪崩击穿的原理

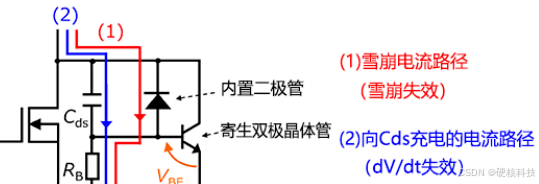

雪崩击穿是指当向MOSFET施加的电压超过其绝对最大额定值BVDSS时,MOSFET内部的电场强度增加,自由电子在高电场下被加速并获得高能量。这些高能量的电子在撞击硅原子时,会产生更多的电子-空穴对,导致电流急剧增加。这种电流激增现象被称为“雪崩击穿”。

在雪崩击穿过程中,流经MOSFET的电流称为“雪崩电流IAS”,该电流的存在可能引发多种失效模式。

- 雪崩失效的类型

短路失效:

当雪崩电流流过MOSFET的基极寄生电阻RB时,可能会在寄生双极型晶体管的基极和发射极之间产生足够大的电位差VBE,从而触发寄生双极晶体管导通。一旦寄生双极晶体管导通,大量的电流将流经MOSFET,导致器件短路并最终失效。

热量失效:

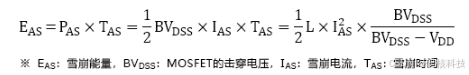

雪崩击穿期间,由于电流的流动与电压的乘积形成了功率损耗(称为“雪崩能量EAS”),这部分能量转化为热量,可能导致MOSFET过热失效。尤其在长时间或频繁的雪崩条件下,热积累将进一步增加MOSFET的失效风险。

!

!

3. 防止雪崩击穿的对策

选择更高耐压的MOSFET:

通过使用BVDSS值更高的MOSFET,可以减少雪崩击穿发生的概率。这种方法适用于电路设计初期的元件选型阶段。

优化电路设计:

在设计电路时,降低反激电压或减少寄生电感可以有效减少雪崩击穿的发生。例如,设计更短引脚的MOSFET封装或者优化PCB布局,能够降低寄生电感,从而减小因浪涌电压导致的雪崩击穿风险。

雪崩测试和评估:

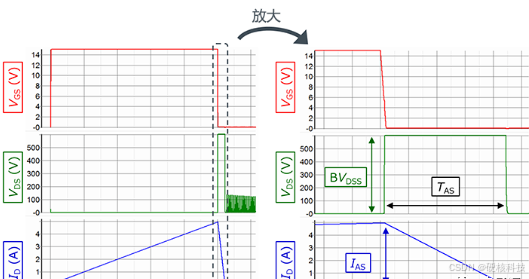

在产品开发过程中,通过雪崩测试评估MOSFET在实际工作条件下的抗雪崩能力,并确保工作条件在规格书规定的IAS和EAS绝对最大额定值范围内。

二、dV/dt失效现象及其机制

- dV/dt失效的原理

dV/dt失效是指在MOSFET关断时,由于漏源极电压VDS的变化速率过快,MOSFET的寄生电容Cds会产生瞬态充电电流。当这一电流通过基极电阻RB时,可能导致寄生双极晶体管的基极-发射极间产生电位差VBE,从而使寄生双极晶体管误导通,引发短路并导致失效。

- dV/dt失效的影响因素

VDS的上升速率:

VDS的上升速率越快,寄生电容Cds的充电电流越大,寄生双极晶体管越容易导通。因此,在高频应用中,VDS的陡峭上升可能显著增加dV/dt失效的风险。

反向恢复特性:

在桥式电路或Totem-Pole PFC等应用中,反向恢复电流Irr对dV/dt的影响不容忽视。反向恢复特性越差,MOSFET的dV/dt失效风险越高。因此,选择反向恢复特性较好的MOSFET可以有效降低失效风险。

- 防止dV/dt失效的对策

优化驱动电路:

使用合适的栅极电阻RG,调节MOSFET开关过程中的电压上升速率,可以有效减少dV/dt失效的发生。较大的栅极电阻通常可以减缓开关速度,从而降低dV/dt。

使用低反向恢复电流的MOSFET:

在设计桥式电路时,应优先选择反向恢复特性优良的MOSFET,以减小反向恢复电流对dV/dt的影响。

进行双脉冲测试:

双脉冲测试是一种常用的评估dV/dt失效风险的方法,通过仿真和实测电路中的VDS和ID波形,可以预测和预防dV/dt失效。

雪崩击穿和dV/dt失效是影响MOSFET可靠性的重要因素。通过理解这些失效机制并采取适当的电路设计和元器件选择措施,可以有效提高MOSFET在高压和高频环境下的工作稳定性。未来,随着电力电子技术的不断发展,对MOSFET性能的要求将进一步提高,因此,深入研究和解决这些失效问题将是保障电力电子系统可靠性的重要途径。

6466

6466

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?