目录

引言

逻辑综合分为三个阶段:

- 转译(Translation):把电路转换为EDA内部数据库,这个数据库跟工艺库是独立无关的;

- 优化(Optimozation):根据工作频率、面积、功耗来对电路优化,来推断出满足设计指标要求的门级网表;

- 映射(Mapping):将门级网表映射到晶圆厂给定的工艺库上,最终形成该工艺库对应的门级网表。

在综合的时候,首先 DC 的 HDL compiler 把 HDL 代码转化成 DC 自带的 GTECH 格式,然后 DC 的library compiler 根据标准设计约束(SDC)文件、IP-DW 库、工艺库、图形库、(使用拓扑模式时,还要加入 ICC 生成的 DEF 模式,加载物理布局信息)进行时序优化、数据通路优化、功耗优化(DC 的 power compiler 进行)、测试的综合优化(DC 的 DFT compiler),最后得到优化后的网表。

关键词:DC综合 综合约束 时序报告

概述

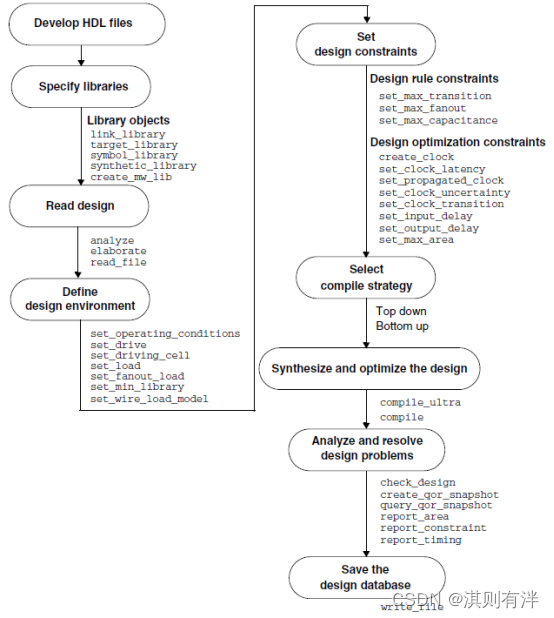

使用DC逻辑综合的流程大致可以分为以下几个部分:

- 预综合过程(Pre-Synthesis Processes):在综合过程之前的一些为综合做准备的步骤:

- DC启动;

- 设置各种库文件:

• link_library;

• target_library;

• symbol_library; - 创建启动脚本文件;

- 读入设计文件;

• analyze;

• elaborate;

• read_file; - DC中的设计对象;

- 各种模块划分;

- Verilog的编码。

- 施加设计约束:

- 设置环境约束:

• set_operating_coditions;

• set_wire_load;

• set_drive;

• set_driving_cell;

• set_load;

• set_fanout_load; - 设置时序约束:

- 设计规则的约束:

• set_max_transition;

• set_max_fanout;

• set_max_capacitance; - 优化的约束:

• create_clock;

• set_clock_skew;

• set_input_delay;

• set_output_delay;

• set_max_area;

- 设计规则的约束:

- 设置环境约束:

- 选择编译策略:

- top down;

- bottom up;

- 设计综合;

- 查看报告;

- 存储设计数据。

读入设计文件

DC提供了两种命令来读入设计:read 命令和 analyze/elaborate 命令。Synopsys 最初引进了read 命令,随后又有了 analyze/elaborate 命令。较之 read 命令,analyze/elaborate 命令为设计输入提供了一种快速而强有力的方法,因此,推荐 RTL 设计输入使用。

DC 的 read 指令支持多种硬件描述格式,不同模式下读取不同格式文件有以下区别:

- dc_shell工作模式:读取不同的文件格式只需要带上不同的参数:

shell read -format verilog[db、vhdl etc.] file - tcl工作模式:读取不同的文件格式需要使用不同的命令:

shell read_db file.db read_verilog file.v read_vhdl file.vhd

同时使用 analyze 和 elaborate 指令:

- analyze:分析 HDL 的源程序并将分析产生的中间文件存于 work(或用户指定)的目录下;

shell analyze -format sverilog {a.sv b.sv chip_top.sv} - elaborate:在产生的中间文件中生成 verilog 的模块或 VHDL 的实体,缺省状态下读取的是 work 目录中的文件。

shell elaborate chip_top

analyze 和 elaborate 命令是两种不同的命令,它使得设计人员可以在建立设计通用逻辑之前先对设计进行语法错误和 RTL 转换分析。通用逻辑或 GTECH 元件是 Synopsys 通用工艺无关库的一部分,它们是布尔函数的末映射表示并且作为工艺相关库的占位符。analyze&elaborate 允许设计者在设计的 GTECH建立之前,首先分析设计的语法错误和进行 HDL 代码转换。analyze 做语法检查,产生 “.syn” 文件存储在 work 路径下的定义设计库内,可供 elaborate 使用,不必重复分析;read不行。

analyze&elaborate 之后没必要设置顶层文件,也没必要进行 link 操作(Link 设计,查看当前要综合的设计是否缺少子模块,返回值是1,说明子模块完整)。

另外只有 elaborate 可以设定顶层文件的 parameter:

elaborate chip_top -parameter "DATA_WIDTH = 8,ADDR_WIDTH = 8"

为了在详细描达设计的过程中传递所需参数,参数化设计(如 VHDL 中使用的 generic 语句)必须使用 analyze 和 elaborate 命令。read 命令用于将编译前设计或网表输入到 DC 中。

| analyze/elaborate | read | |

|---|---|---|

| 输入格式 | Verilog 或 VHDL | 所有格式:Verilog、VHDL、EDIF、db等 |

| 推荐用法 | 综合使用 Verilog 或 VHDL 格式的 RTL | 读网表、预编译设计等 |

| 设计库 | 使用 -library 选项来指定设计库,而不是调用 dc_shell 的目录 | 不保存分析结果 |

| 类属(在VHDL中使用) | 在详细描述设计的过程中类属中的参数可以被设置 | 不能用来传递参数 |

| 结构(在VHDL中使用) | 能指定在 VHDL 中的结构被详细描述 | 不能指 |

本文详细介绍了DC逻辑综合的过程,包括预综合过程、设计约束设置、读入设计文件、综合结果输出和时序报告的生成。重点讲解了如何设置环境约束如操作条件、驱动强度、线载模型和时序约束,以及如何查看时序报告和设计违规检查。通过对DC工具的使用,实现对硬件设计的逻辑综合和优化。

本文详细介绍了DC逻辑综合的过程,包括预综合过程、设计约束设置、读入设计文件、综合结果输出和时序报告的生成。重点讲解了如何设置环境约束如操作条件、驱动强度、线载模型和时序约束,以及如何查看时序报告和设计违规检查。通过对DC工具的使用,实现对硬件设计的逻辑综合和优化。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

213

213

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?