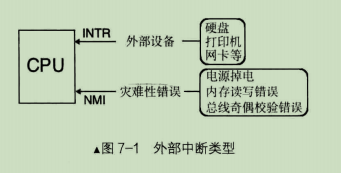

外部中断

外部硬件的中断是通过两根信号线通知CPU的,即INTR(INTeRrupt,可屏蔽中断)线和NMI(NonMaskableInterrupt,不可屏蔽中断)线

二者的区别是:从INTR引脚收到的中断都是不影响系统运行的,而从NMI引脚收到的中断都是极其重大的。

内部中断

内部中断是指由软中断指令本身(如使用int 8位立即数进行系统调用)或在指令执行过程中引起的中断(如除0异常)。

中断描述符表基础

CPU收到中断信号后,需要具体地知道是哪一种情况导致的中断才能进行相应的中断处理,这在保护模式下是借助中断描述符表实现的。

每一种可屏蔽中断都有一个中断向量号,而不可屏蔽中断不在操作系统能解决的范围内,所以只需共用一个中断向量号2即可。

异常和不可屏蔽中断的中断向量号是由CPU自动提供的,来自外部设备的可屏蔽中断号是由中断代理提供的(常见的代理为8259A),软中断的中断向量号是由软件提供的。

中断向量号即为此种中断在中断描述符表中的下标,CPU可根据中断向量号在中断描述符表中检索对应的中断处理程序并执行。

中断描述符表

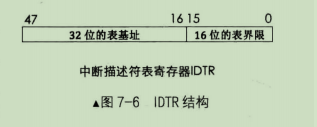

寻址时,IDT与GDT类似,在CPU内部有一个48b的中断描述符表寄存器IDTR,其内存储着IDT的大小(16b)和地址(32b),CPU在必要时通过此寄存器获取IDT的地址。

IDTR的位数限制了IDT的大小最多为64KB,即8192个描述符,与GDT不同的是,IDT的0号描述符也是可用的,不过处理器最多只支持0到254号共255个中断。

同样地,也有一条专门的指令用于将数据加载到IDTR中:lidt 48位内存数据

中断产生

中断处理

-

CPU接收到中断向量号后定位中断门描述符(每个8B)。定位过程为:中断向量号 * 8 + IDTR中的IDT地址。

-

处理器进行特权级检查。主要是检查CPL与门的DPL,特权级的变化有两种情况,一是低到高切换,二是平级切换。

-

低到高切换时的压栈:CPU需要把CS、EIP、EFLAGS、SS和ESP等寄存器压栈以实现中断返回。具体来说,CPU先临时保存旧的SS和ESP的值,然后从当前任务的TSS中找到与目标代码段DPL级别相同的栈(如0级栈)的段选择子和偏移量,分别将其加载到SS和ESP寄存器,实现了栈的切换,然后将旧的SS值和ESP值压入新栈,再依次压入EFLAGS、CS、EIP、错误码。

-

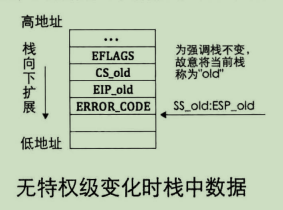

平级切换时的压栈:无需修改SS和ESP,只需将当前任务的EFLAGS、CS、EIP、错误码压栈即可。

-

执行中断处理程序。将特定的中断门描述符所指的中断处理程序的代码段选择子加载到CS中,把其段内偏移地址加载到EIP中,开始执行。

2601

2601

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?