一颗CUP的诞生

读书笔记《嵌入式C语言自我修养》

1.1CPU的构成

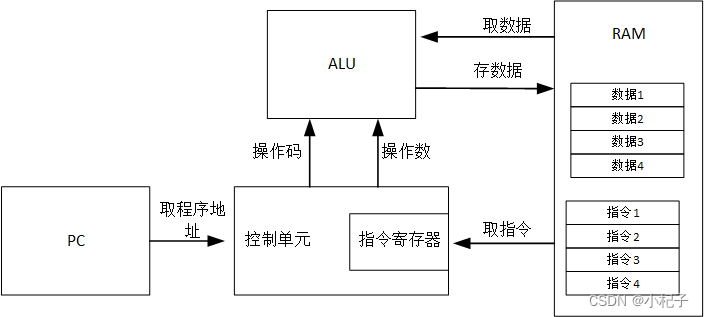

CPU的构成,主要由算数逻辑单元、控制单元、程序计数器、RAM内存组成。

| 构成 | 功能 |

|---|---|

| 算数逻辑单元(ALU) | 执行运算的单元,执行算数或逻辑运算的装置 |

| 控制单元 | 根据PC中的地址,从RAM中获取指令 |

| 程序计数器(PC) | 存放地址,改地址对应RAM中的指令 |

| RAM内存 | 存放程序指令和数据 |

CPU工作流程如下:

ALU要执行运算,就要知道谁和谁,即将进行怎样的运算。其中“谁和谁”被称作操作数,“进行怎样的运算”被称操作码。CPU整个的执行任务列表都存在RAM中,执行到哪一项任务就记录在程序计数器PC中。控制单元就是通过RAM和PC的信息,整理出这个周期需要执行的任务。控制单元从PC中读取到指令的地址,然后去RAM中读取程序指令,在通过指令寄存器将指令转化为操作数和操作码送给ALU。执行完程序后,ALU将结果存到RAM中,然后PC的指令地址+1(或者进行跳转)

1.2 CPU的设计流程

集成芯片的的设计流程

1.3 计算机体系结构

易失性存储器:随机访问任意地址读写数据,断电后数据消失,读写速度快。

非易失性存储器:不支持随机地址访问,断电后数据不消失,读写速度慢。

计算机混合1使用这两种存储器,易失性存储器作为内存,非易失性存储器作为外存。

计算机运行是,现将外存的程序加载到内存中,进行指令的执行和数据的处理。

1.3.1 架构

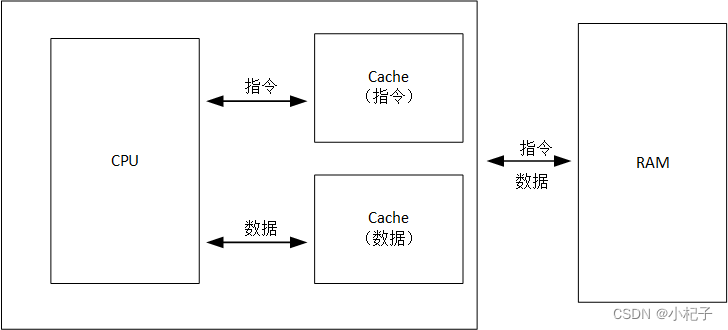

存储器中存在数据和指令。根据保存方式不同,计算机分为两个不同的架构。

冯.诺依曼架构:将指令和数据混合存储,放在不同的地址,放到外部存储器中。计算器运行是先加载到内部存储器中,再内部存储器中进行读取,优点,简单,易实现。

哈佛架构:指令数据分开放,独立地址,独立读取,一个周期可以并行操作。效率高,但结构复杂。

又两个优缺点分明的结构,取长补短,中西结合,经典的混合结构出世了。

外部存储器采用冯.诺依曼架构,内部存储器采用哈佛架构。

其中:Cache为静态随机访问存储器,功能提前缓存一部分数据和指令,来减少CPU方位外部RAM的次数,提高性能。CPU的运行速度很快,RAM的运行速度相对CPU很慢,所以CPU等待RAM的回应是很浪费CPU的时间的,所以CPU不能总访问RAM,会降低性能。需要一个缓冲的模块来提前把数据取来等着CPU来要,这个就是Cache的缓存机制。

但是Cache的内存相比RAM来说较小,Cache取来的数据可能不是CPU即将需要的数据,那么就需要CPU相RAM要,缓存机制没有起作用。

增大Cache的内存可以解决,但是明显没那么简单,增大Cache内存会增大芯片面积,芯片温度上升。就又加了一级缓存,叫二级Cache。一级Cache和二级Cache配合工作。保证计算器高效运行。

有的处理器没有Cache机制,是因为CPU程序没那么高端,运行速度,没那么快,与RAM之间不存在速度差,这些芯片主打一个低功耗。如C51系列单片机,cortex-M1,cortex-M2,cortex-M3,cortex-M4系列的ARM处理器。

两种存储器优缺点明显,最好的方法就是,取长补短,中西结合。 ↩︎

2730

2730

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?