1.级联

module add_jl(sum,cout,a,b,cin);

output[7:0] sum;

output cout;

input[7:0] a,b;

input cin;

full_add1 f0(a[0],b[0],cin,sum[0],cin1); //级连描述

full_add1 f1(a[1],b[1],cin1,sum[1],cin2);

full_add1 f2(a[2],b[2],cin2,sum[2],cin3);

full_add1 f3(a[3],b[3],cin3,sum[3],cin4);

full_add1 f4(a[4],b[4],cin4,sum[4],cin5);

full_add1 f5(a[5],b[5],cin5,sum[5],cin6);

full_add1 f6(a[6],b[6],cin6,sum[6],cin7);

full_add1 f7(a[7],b[7],cin7,sum[7],cout);

endmodule

module full_add1(a,b,cin,sum,cout); //1λȫ¼ÓÆ÷

input a,b,cin;

output sum,cout;

assign sum=a^b^cin;

assign cout=(a&b)|(a&cin)|(b&cin);

endmodule

`timescale 1ns/1ns

module tb_add_jl();

wire [7:0]sum;

wire cout;

reg [7:0]a;

reg [7:0]b;

reg cin;

add_jl u1(.a(a),.b(b),.cin(cin),.cout(cout),.sum(sum));

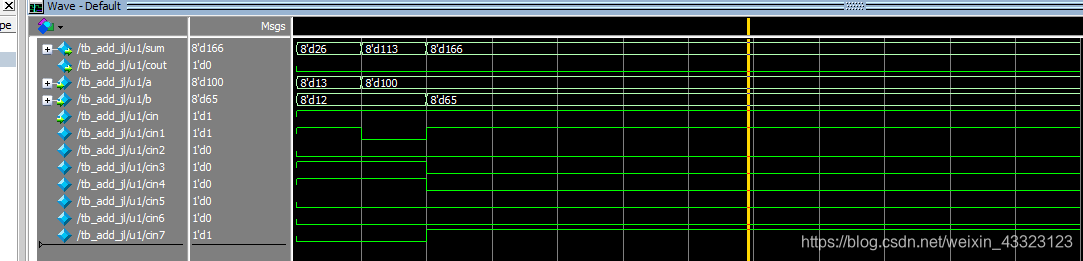

initial begin

cin=1'b1;

a=8'd13;

b=8'd12;

#50 a=8'd100;

#50 b=8'd65;

end

endmodule

2.并行

module add_bx(cout,sum,a,b,cin);

output[7:0] sum;

output cout;

input[7:0] a,b;

input cin;

assign {cout,sum}=a+b+cin;

endmodule

本文详细介绍了两种不同的加法器设计方法:级联加法器和并行加法器。通过具体的Verilog代码示例,展示了如何使用全加器模块实现多位数的加法运算,级联加法器通过串行连接多个全加器实现,而并行加法器则采用更高效的一次性计算方式。

本文详细介绍了两种不同的加法器设计方法:级联加法器和并行加法器。通过具体的Verilog代码示例,展示了如何使用全加器模块实现多位数的加法运算,级联加法器通过串行连接多个全加器实现,而并行加法器则采用更高效的一次性计算方式。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?