特性

- 12bit精度

- 2Msps采样率

- 可选差分和单端输入

- 4个内部输入

- 内部温度传感器

- DAC输出

- V C C / 10 V_{CC}/10 VCC/10

- 1.1V 带隙基准电压

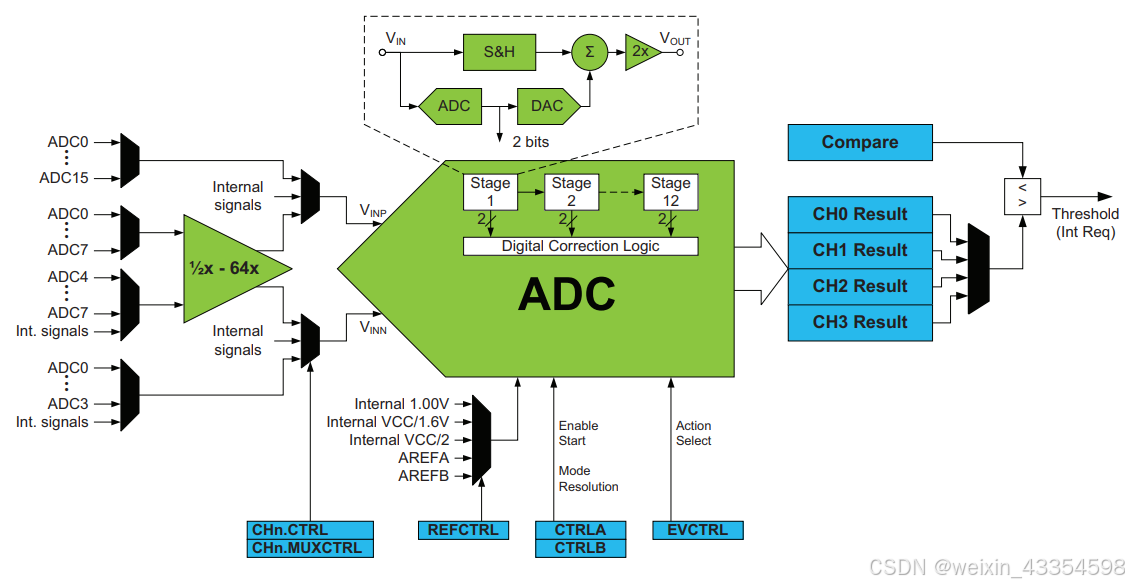

框图

输入

可选择四种类型的输入:

- 差分输入

- 带增益的差分输入

- 单端输入

- 内部输入

对于仅有一个 ADC 的 AVR XMEGA 器件,PORTA 和 PORTB 上的引脚可能都可用作 ADCA 的输入。

该 ADC 是差分型,因此在单端测量时,负输入端连接到一个固定的内部值。

差分输入

当启用差分输入时,所有输入引脚都可以选择为正输入,而引脚 0 到 3 可以选择为负输入。使用差分输入时,ADC 必须设置为带符号模式。

带增益的差分输入

当启用带增益的差分输入时,所有输入引脚都可以选择为正输入,而引脚 4 到 7 可以选择为负输入。使用增益级时,差分输入会先通过增益级采样并放大,之后再输入到 ADC。使用带增益的差分输入时,ADC 必须设置为带符号模式。

增益可选择为 1/2x、1x、2x、4x、8x、16x、32x 和 64x。

单端输入

对于单端测量,所有输入引脚都可以用作输入。单端测量可以在带符号模式和无符号模式下进行。

单端信号的输入范围为0-VREF。

在带符号模式下,负输入端连接到内部接地。

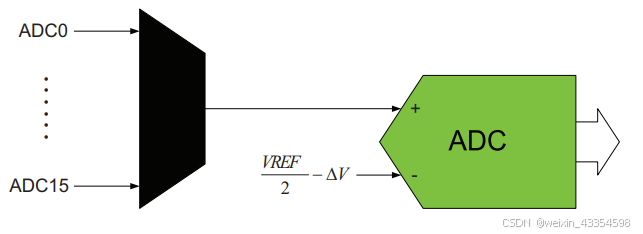

无符号模式下的单端输入

在无符号模式下,负输入端连接到参考电压(VREF)的一半减去一个固定偏移量。该偏移量的标称值为:

Δ

V

=

V

R

E

F

×

0.05

\Delta V=VREF \times 0.05

ΔV=VREF×0.05

由于该 ADC 是差分型的,因此正单端输入的输入范围为 VREF 到 0。此偏移量允许 ADC 在无符号模式下测量零交叉点,并允许对当器件内部接地高于外部接地时的正偏移进行校准。

内部输入

这些内部信号可以被 ADC 测量或使用:

- 温度传感器

- Bandgap 电压

- 缩放后的 VCC

- DAC 输出

- Pad 接地和内部接地

温度传感器提供一个随器件内部温度线性增加的输出电压。需要一个或多个校准点,通过温度传感器的测量值来计算温度。温度传感器在生产测试中校准一次,结果存储在生产签名行的 TEMPESENSE0 和 TEMPSENSE1 中。

Bandgap 电压是一个精确的内部电压参考。

VCC 可以直接测量,在进入 ADC 输入前先将其缩小 10 倍。例如,1.8V 的 VCC 将被测量为 0.18V,3.6V 的 VCC 将被测量为 0.36V,这便于测量 VCC 电压。

在测量前需要启用内部信号。启用 Bandgap 和 DAC。

对于差分测量,可以选择 Pad 接地 (Gnd) 和内部接地 (Internal Gnd) 作为负输入。Pad Gnd 是引脚上的接地电平,与外部接地相同或非常接近。内部接地是器件内部的接地电平。

当在单端带符号模式下测量其他内部信号时,内部接地用作负输入。在无符号模式下测量内部信号时,负输入连接到以下公式给定的固定值,即参考电压 (VREF) 的一半减去固定偏移量,与单端无符号输入相同。

V

INN

=

V

REF

2

−

Δ

V

V_{\text{INN}} = \frac{V_{\text{REF}}}{2} - \Delta V

VINN=2VREF−ΔV

ADC 通道

为了充分利用 ADC,其设计包含四对独立的多路复用器(MUX)控制寄存器及相应的结果寄存器。每对寄存器构成一个 ADC 通道。

所有 ADC 通道共用同一个 ADC 流水线进行转换。流水线允许每个 ADC 时钟周期启动一个新的转换,这意味着来自不同通道的多个 ADC 测量可以同时且独立地进行。各通道的结果寄存器独立更新,不受其他通道转换的影响。

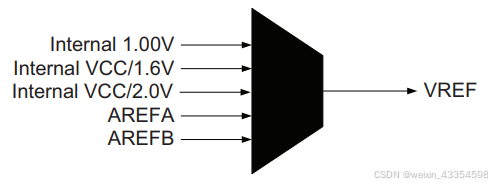

电压参考选择

以下电压可以用作 ADC 的参考电压(VREF):

- 来自 bandgap 的精确内部 1.00V 电压

- 内部 VCC / 1.6 \text{VCC}/1.6 VCC/1.6 电压

- 内部 VCC / 2 \text{VCC}/2 VCC/2电压

- 应用于 PORTA 上 AREF 引脚的外部电压

- 应用于 PORTB 上 AREF 引脚的外部电压

转换结果

ADC 转换的结果会写入相应通道的结果寄存器。ADC 可以设置为带符号或无符号模式,该设置对整个 ADC 和所有 ADC 通道全局生效。

在带符号模式下,生成正负结果。当任何 ADC 通道设置为差分测量时,必须使用带符号模式。在 12 位分辨率下,带符号结果的最大值TOP为 2047,结果范围为 -2048 至 +2047(0xF800 - 0x07FF)。

ADC 的传输函数可以表示为:

RES

=

(

VINP

−

VINN

VREF

)

×

GAIN

×

(

TOP

+

1

)

\text{RES} = \left( \frac{\text{VINP} - \text{VINN}}{\text{VREF}} \right) \times \text{GAIN} \times (\text{TOP} + 1)

RES=(VREFVINP−VINN)×GAIN×(TOP+1)

其中,VINP 和 VINN 分别为 ADC 的正输入和负输入。

对于差分测量,GAIN 取值范围为 1/2 至 64;对于单端和内部测量,GAIN 始终为 1,VINN 为内部接地。

在无符号模式下,仅生成正结果。无符号结果的最大值TOP为 4095,结果范围为 0 至 +4095(0x0 - 0x0FFF)。

在无符号模式下,传输函数为:

RES

=

(

VINP

+

Δ

V

VREF

)

×

(

TOP

+

1

)

\text{RES} = \left( \frac{\text{VINP}+\Delta V}{\text{VREF}} \right) \times (\text{TOP} + 1)

RES=(VREFVINP+ΔV)×(TOP+1)

其中 VINP 是单端或内部输入。

ADC 可配置生成 8 位或 12 位结果。分辨率越低,转换时间越快。

结果寄存器宽度为 16 位,数据以右对齐的 16 位值存储。右对齐表示最低有效字节 (lsb) 位于低字节中。12 位结果可以采用左对齐或右对齐存储。左对齐表示最高有效字节 (msb) 位于高字节。

当 ADC 处于带符号模式时,msb 代表符号位。在 12 位右对齐模式下,符号位(位 11)扩展到位 12-15,以直接创建一个带符号的 16 位数。在 8 位模式下,符号位(位 7)填充至整个高字节。

比较功能

ADC 内置了一个 12 位比较功能。ADC 比较寄存器可以保存一个 12 位值,表示一个阈值电压。每个 ADC 通道都可以配置为自动将其结果与该比较值进行比较,并在结果高于或低于阈值时触发中断或事件。

需要注意的是,所有四个 ADC 通道共享同一个比较寄存器。

开始转换

在启动转换之前,必须为一个或多个 ADC 通道选择输入源。可以通过以下方式启动通道的 ADC 转换:

- 软件触发:通过应用软件将转换启动位写入通道。

- 事件触发:通过事件系统中的任意事件触发转换。

可以同时对多个通道写入启动转换位,也可以使用单个事件触发多个通道的转换。这使得可以通过一个事件扫描多个或所有通道。扫描将从最低的通道编号开始。

输入源扫描

对于 ADC 通道 0,可以选择一系列连续的输入源,在启动转换时自动扫描并测量。这可以通过 MUX 控制寄存器设置第一个(最低)正 ADC 通道输入,并指定连续的正输入源的数量来实现。当启动转换时,首先测量并转换所选的第一个输入源,然后在每次转换后递增正输入源选择,直到达到指定的扫描输入源数量。

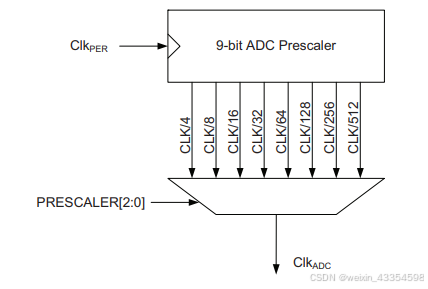

ADC时钟

ADC 的时钟源来自外设时钟。ADC 可以对外设时钟进行预分频,以提供一个符合应用需求并在 ADC 工作范围内的 ADC 时钟(

c

l

k

A

D

C

clk_{ADC}

clkADC)。

ADC 的传播延迟公式为:

传播延迟 = 1 + RESOLUTION 2 + GAIN f ADC \text{传播延迟} = \frac{1+\frac{\text{RESOLUTION}}{2}+\text{GAIN}}{f_{\text{ADC}}} 传播延迟=fADC1+2RESOLUTION+GAIN

其中:

- 分辨率 是 ADC 的分辨率(例如,12位分辨率)。

- 增益 是在转换过程中的增益等级(例如,1、2、4 等)。

- f_ADC 是 ADC 时钟频率。

这个公式表示了 ADC 转换过程中的时间延迟,它受到分辨率、增益和时钟频率的影响。

传播延迟长于一个 ADC 时钟周期,但由于采用了流水线设计,采样率并不是由传播延迟限制的,而是由 ADC 时钟频率限制的。

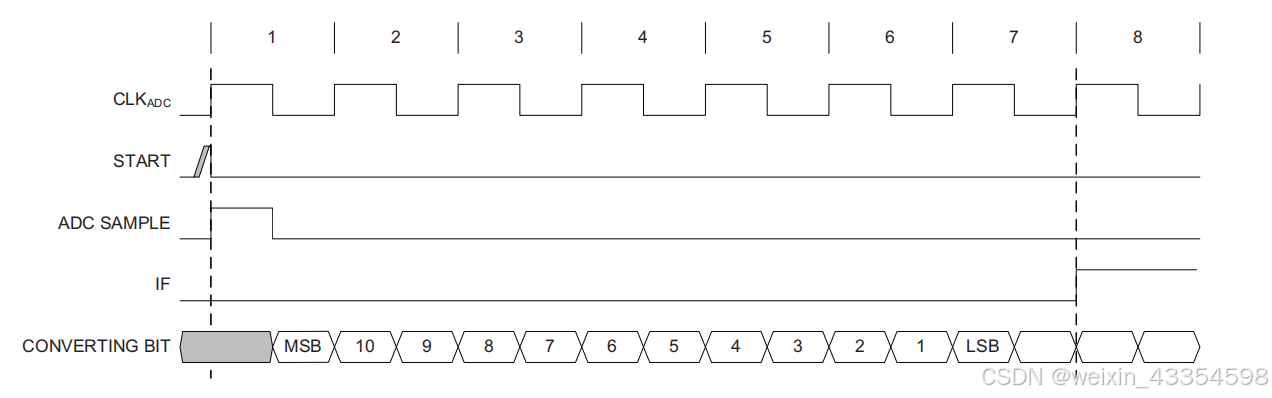

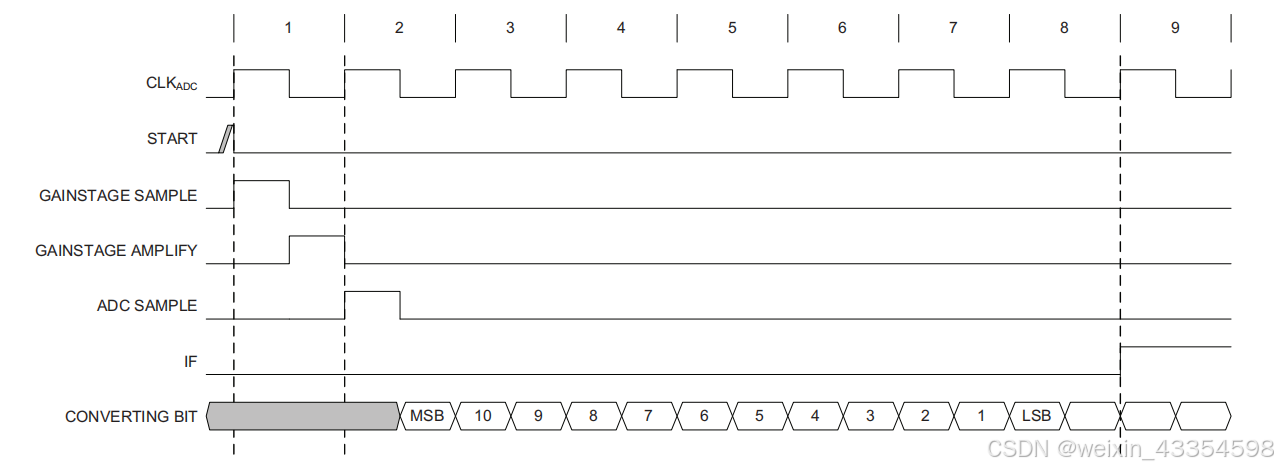

结果的最高有效位(msb)首先被转换,剩余的位将在接下来的三个(对于 8 位结果)或五个(对于 12 位结果) ADC 时钟周期中转换。每转换一位需要半个 ADC 时钟周期。在最后一个周期中,结果被准备好,然后设置中断标志,结果可以在结果寄存器中读取。

ADC输入模式

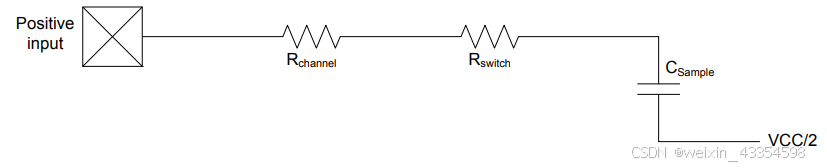

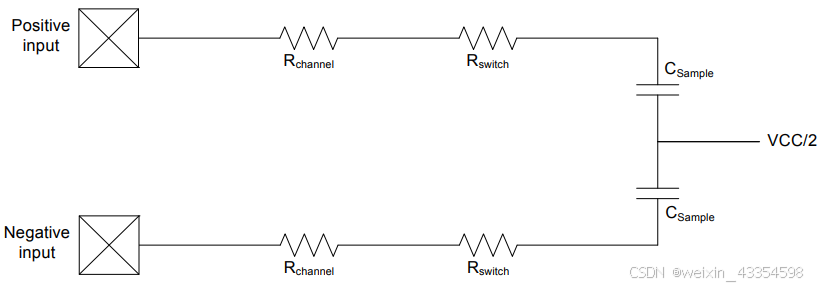

为了达到最大精度,电压输入必须充电给 ADC 中的采样保持(S/H)电容。外部来看,ADC 输入由输入电阻(Rin = Rchannel + Rswitch)和 S/H 电容(Csample)组成。

输入源的输出阻抗

输入源的输出阻抗需要满足以下条件,以实现最大的精度。

R

s

o

u

r

c

e

≤

T

s

C

s

a

m

p

l

e

⋅

ln

(

2

n

+

1

)

−

R

c

h

a

n

n

e

l

−

R

s

w

i

t

c

h

R_{source} \leq \frac{T_s}{C_{sample} \cdot \ln(2^{n+1})} - R_{channel} - R_{switch}

Rsource≤Csample⋅ln(2n+1)Ts−Rchannel−Rswitch

要推导出

R

s

o

u

r

c

e

R_{source}

Rsource 的约束条件公式:

R s o u r c e ≤ T s C s a m p l e ⋅ ln ( 2 n + 1 ) − R c h a n n e l − R s w i t c h R_{source} \leq \frac{T_s}{C_{sample} \cdot \ln(2^{n+1})} - R_{channel} - R_{switch} Rsource≤Csample⋅ln(2n+1)Ts−Rchannel−Rswitch

我们可以从 ADC 的采样和保持电路模型出发,分析电路在采样周期内的充电过程,以确保在指定的采样时间 T s T_s Ts 内达到期望的精度。以下是具体的推导过程。

1. ADC 输入模型与采样电容充电

在 ADC 输入端,有一个等效电路包括:

- 输入电阻 R i n = R c h a n n e l + R s w i t c h R_{in} = R_{channel} + R_{switch} Rin=Rchannel+Rswitch;

- 采样电容 C s a m p l e C_{sample} Csample;

- 源电阻 R s o u r c e R_{source} Rsource。

当 ADC 采样保持电路开始采样时,采样电容 C s a m p l e C_{sample} Csample 需要在采样周期 T s T_s Ts 内通过输入网络充电到接近输入电压的值,以实现期望的精度。这个充电过程符合 RC 电路的充电特性。

2. RC 电路的充电特性

对于一个 RC 电路,充电电压 V ( t ) V(t) V(t) 随时间 t t t 的变化为:

V ( t ) = V i n ( 1 − e − t R C ) V(t) = V_{in} \left(1 - e^{-\frac{t}{RC}}\right) V(t)=Vin(1−e−RCt)

在这里:

- V i n V_{in} Vin 是输入电压;

- R = R s o u r c e + R i n = R s o u r c e + R c h a n n e l + R s w i t c h R = R_{source} + R_{in} = R_{source} + R_{channel} + R_{switch} R=Rsource+Rin=Rsource+Rchannel+Rswitch 是总电阻;

- C = C s a m p l e C = C_{sample} C=Csample 是采样电容。

在采样时间 T s T_s Ts 内,我们希望电压 V ( T s ) V(T_s) V(Ts) 尽可能接近 V i n V_{in} Vin,并且达到特定精度 n n n 位。

3. 精度要求与电压误差

要达到 n n n 位的精度,采样电容上的电压 V ( T s ) V(T_s) V(Ts) 与输入电压 V i n V_{in} Vin 的误差必须小于或等于量化误差的半个 LSB(最低有效位):

V e r r o r ≤ V i n 2 n + 1 V_{error} \leq \frac{V_{in}}{2^{n+1}} Verror≤2n+1Vin

因此,充电电压在时间 T s T_s Ts 时的条件可以写为:

V i n ( 1 − e − T s ( R s o u r c e + R c h a n n e l + R s w i t c h ) C s a m p l e ) ≥ V i n ( 1 − 1 2 n + 1 ) V_{in} \left(1 - e^{-\frac{T_s}{(R_{source} + R_{channel} + R_{switch}) C_{sample}}}\right) \geq V_{in} \left(1 - \frac{1}{2^{n+1}}\right) Vin(1−e−(Rsource+Rchannel+Rswitch)CsampleTs)≥Vin(1−2n+11)

4. 消去 V i n V_{in} Vin 并整理

两边除以 V i n V_{in} Vin 后,得到:

1 − e − T s ( R s o u r c e + R c h a n n e l + R s w i t c h ) C s a m p l e ≥ 1 − 1 2 n + 1 1 - e^{-\frac{T_s}{(R_{source} + R_{channel} + R_{switch}) C_{sample}}} \geq 1 - \frac{1}{2^{n+1}} 1−e−(Rsource+Rchannel+Rswitch)CsampleTs≥1−2n+11

整理后为:

e − T s ( R s o u r c e + R c h a n n e l + R s w i t c h ) C s a m p l e ≤ 1 2 n + 1 e^{-\frac{T_s}{(R_{source} + R_{channel} + R_{switch}) C_{sample}}} \leq \frac{1}{2^{n+1}} e−(Rsource+Rchannel+Rswitch)CsampleTs≤2n+11

5. 对数变换

取自然对数以解出 R s o u r c e R_{source} Rsource 的条件:

− T s ( R s o u r c e + R c h a n n e l + R s w i t c h ) C s a m p l e ≤ ln ( 1 2 n + 1 ) -\frac{T_s}{(R_{source} + R_{channel} + R_{switch}) C_{sample}} \leq \ln\left(\frac{1}{2^{n+1}}\right) −(Rsource+Rchannel+Rswitch)CsampleTs≤ln(2n+11)

利用 ln ( 1 2 n + 1 ) = − ( n + 1 ) ln ( 2 ) \ln\left(\frac{1}{2^{n+1}}\right) = -(n+1) \ln(2) ln(2n+11)=−(n+1)ln(2),公式变为:

T s ( R s o u r c e + R c h a n n e l + R s w i t c h ) C s a m p l e ≥ ( n + 1 ) ln ( 2 ) \frac{T_s}{(R_{source} + R_{channel} + R_{switch}) C_{sample}} \geq (n+1) \ln(2) (Rsource+Rchannel+Rswitch)CsampleTs≥(n+1)ln(2)

6. 解出 R s o u r c e R_{source} Rsource 的表达式

将 R s o u r c e R_{source} Rsource 提出来:

R s o u r c e + R c h a n n e l + R s w i t c h ≤ T s C s a m p l e ⋅ ln ( 2 n + 1 ) R_{source} + R_{channel} + R_{switch} \leq \frac{T_s}{C_{sample} \cdot \ln(2^{n+1})} Rsource+Rchannel+Rswitch≤Csample⋅ln(2n+1)Ts

最后,我们得到 R s o u r c e R_{source} Rsource 的约束条件:

R s o u r c e ≤ T s C s a m p l e ⋅ ln ( 2 n + 1 ) − R c h a n n e l − R s w i t c h R_{source} \leq \frac{T_s}{C_{sample} \cdot \ln(2^{n+1})} - R_{channel} - R_{switch} Rsource≤Csample⋅ln(2n+1)Ts−Rchannel−Rswitch

该公式描述了要实现 n n n 位精度的 ADC 采样输入电阻的最大值。这个公式确保了在给定的采样时间内,采样电容上的电压能够充电到足够精确的电平。

ADC的采样时间为ADC时钟的一半。

增益级阻抗模式

为了支持具有非常高源输出电阻的应用,增益级提供了高阻抗模式。在此模式下,每次采样后,采样保持(S/H)电容上的电荷会保留不变。通过对同一输入通道进行多次采样,S/H 电容可以被完全充电。

而当使用低阻抗模式时,每次采样后,S/H 电容上的电荷会被清空。

DMA 传输

DMA 控制器可用于将 ADC 转换结果传输到内存或其他外设。任何 ADC 通道生成的新转换结果都可以触发一个或多个 ADC 通道的 DMA 事务。

中断与事件

ADC 可以生成中断请求和事件。每个 ADC 通道都具有独立的中断设置和中断向量。当 ADC 转换完成或 ADC 测量值高于或低于 ADC 比较寄存器的值时,可以生成中断请求和事件。

校准

ADC 内置线性校准功能。为了达到指定的精度,必须通过软件将生产测试校准值从签名行加载到 ADC 校准寄存器中。用户无需进行线性校准,因此也无法进行此操作。不过,偏移和增益校准需要通过软件完成。

通道优先级

由于外设时钟比 ADC 时钟更快,可以在同一个 ADC 时钟周期内为多个 ADC 通道设置开始转换位。同样,事件也可能触发多个 ADC 通道的转换,从而导致相同的情况。在这种情况下,优先级将分配给编号最低的 ADC 通道。此优先级机制可参考“ADC时序”。

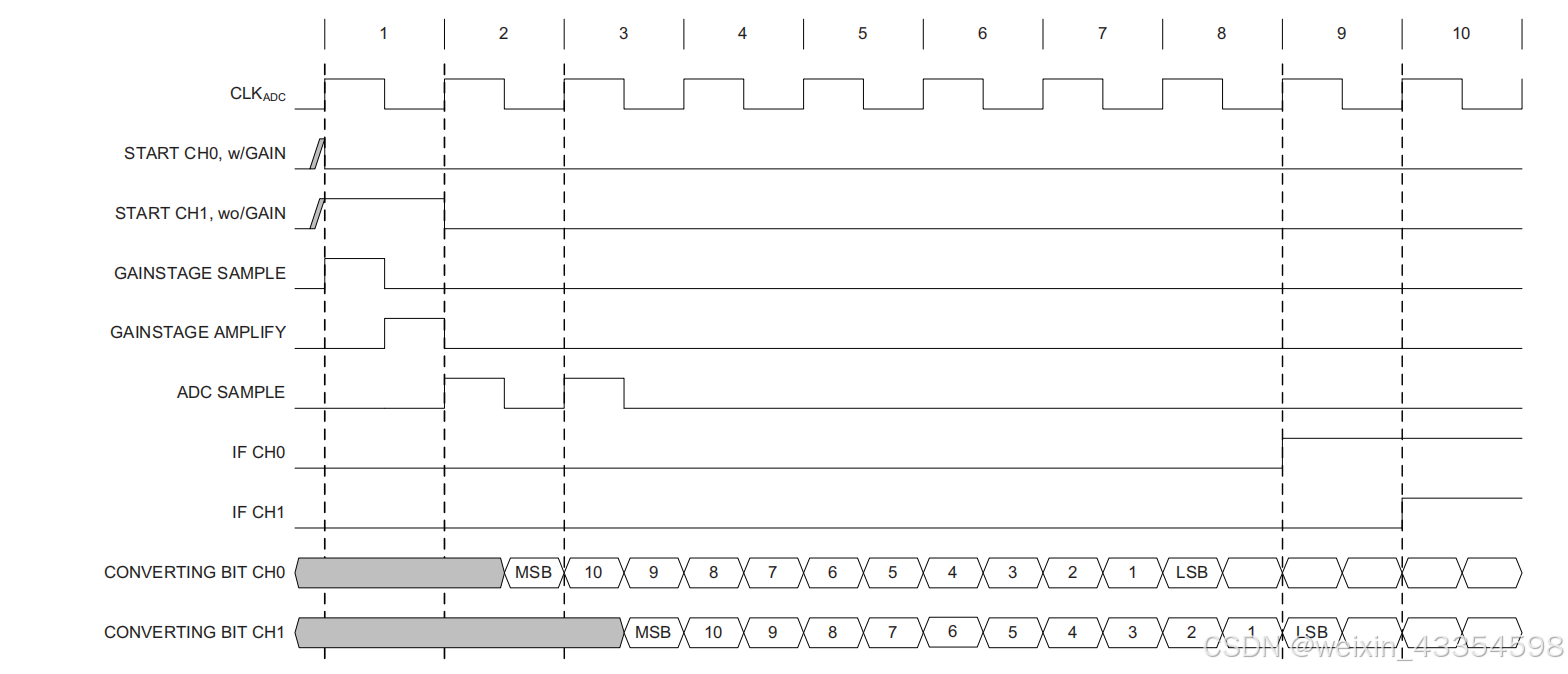

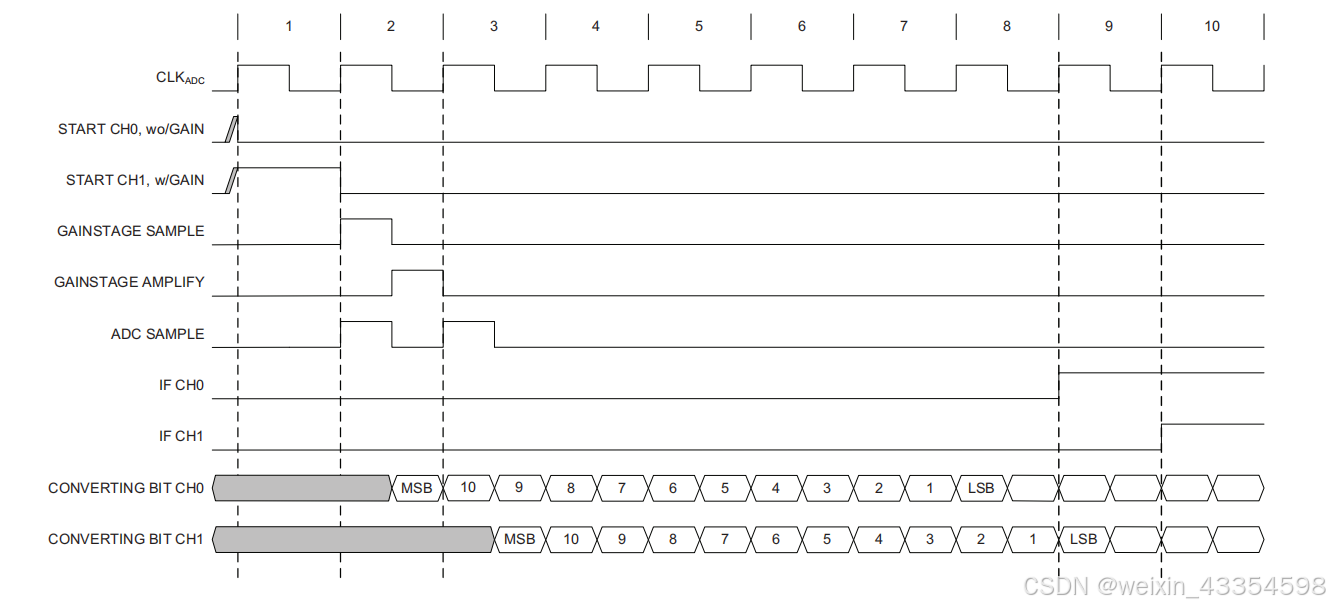

两个 ADC 输入的同步采样

ADC 支持同时采样两个输入通道。这可以通过以下设置实现:将通道 n 设置为不使用增益,将通道 n+1 设置为使用 1 倍增益。使用增益的通道的转换结果将在另一个通道之后的一个 ADC 时钟周期内准备好。详细的时序图可参见“具有增益的两个 ADC 通道的单次转换”。

基于事件的同步采样

在启动 ADC 转换时,从启动触发或事件到实际开始转换可能存在未知的延迟。这可能是由于以下原因:具有更高优先级的 ADC 通道仍在进行转换,或者外设时钟快于 ADC 时钟。为了在接收到事件时立即启动 ADC 转换,可以通过以下步骤实现:清除 ADC 所有测量数据、重置 ADC 时钟,并在下一个外设时钟周期(即下一个 ADC 时钟周期)开始转换。然而,这样操作会导致 ADC 管线中所有正在进行的转换数据丢失。

ADC 可以通过软件清空,或者由传入的事件自动清空。当使用此功能时,每次转换启动触发之间的时间必须长于 ADC 的传播延迟,以确保一个转换完成后再清空管线并启动下一次转换。

此外,在执行清空操作之前,必须清除未完成的事件或启动 ADC 转换的命令。如果未清除,这些未完成的转换将在清空操作后立即开始。

ADC时序

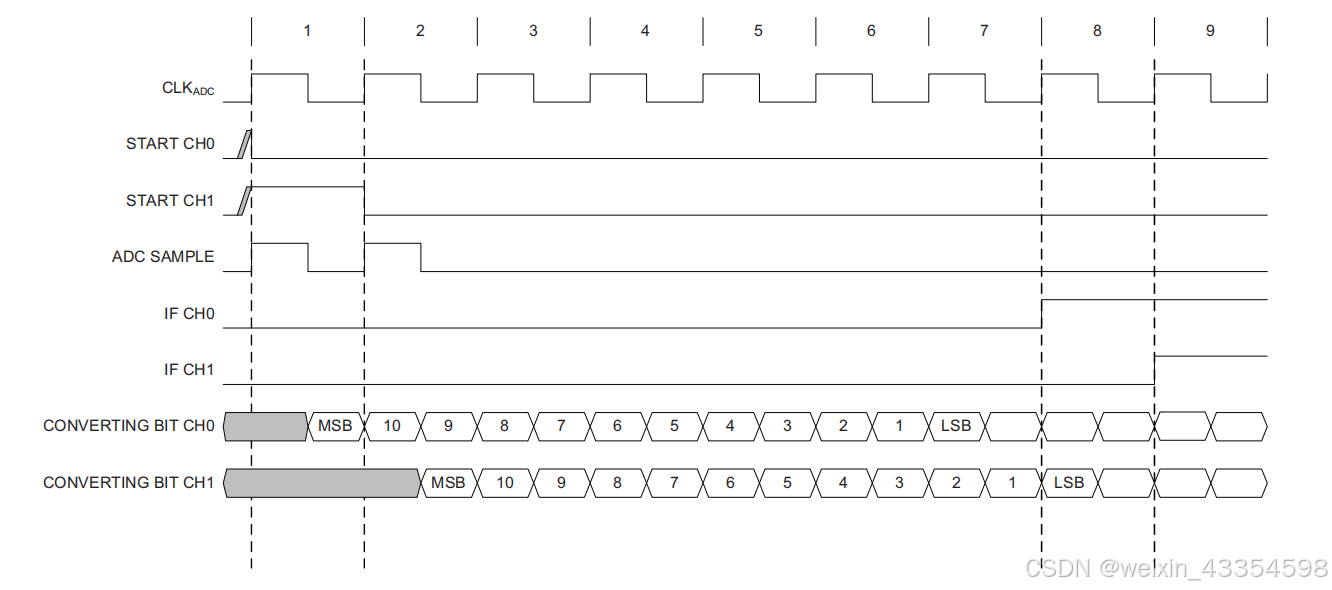

无增益单次转换

带增益的单次转换

两个ADC通道的单次转换

两个ADC通道,ch0带增益

两个ADC通道,CH1带增益

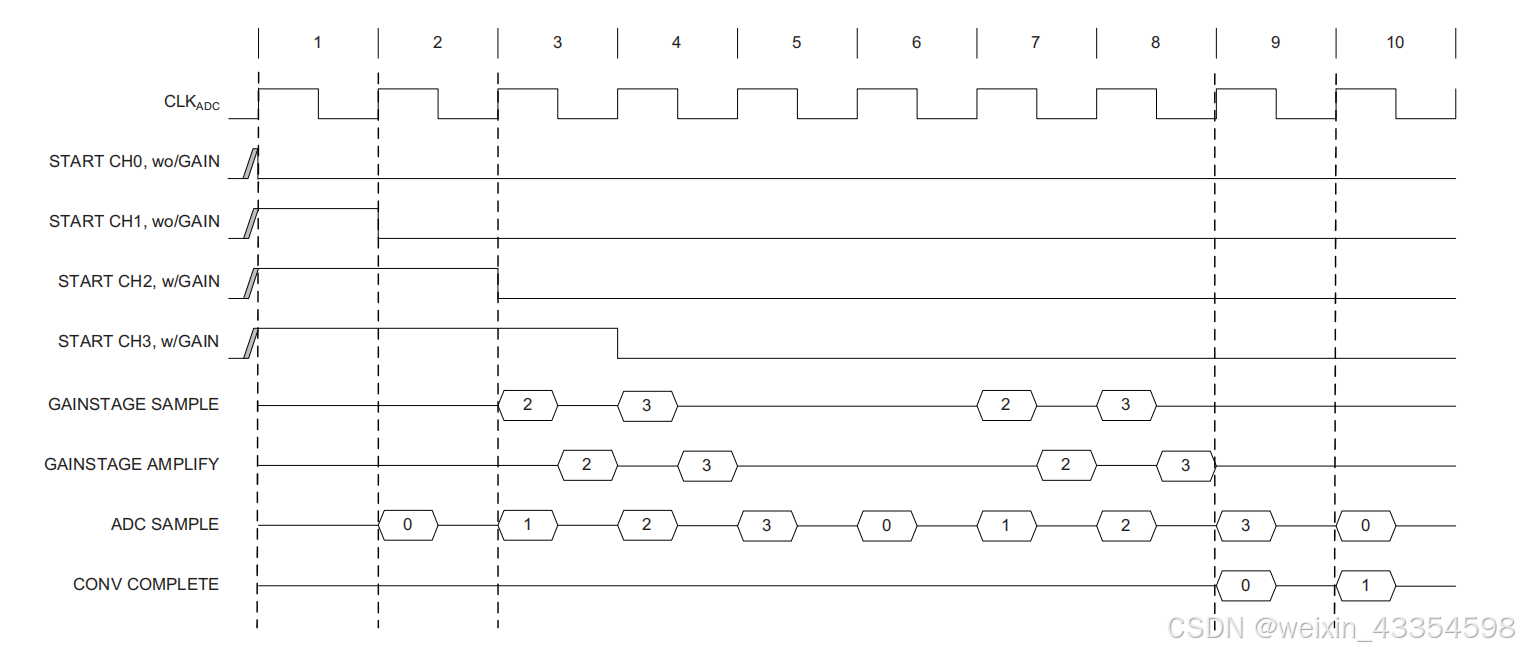

Free Run模式

ADC寄存器

以下每个寄存器按照从高位到低位(即bit7到bit0)描述。

0x00 CTRLA – Control register A

位 7:6 – DMASEL[1:0]: DMA 请求选择

DMASEL[1:0] 组配置说明

| DMASEL[1:0] | 组配置 | 描述 |

|---|---|---|

| 00 | OFF | 无组合 DMA 请求(各通道独立请求)。 |

| 01 | CH01 | ADC 通道 0 和 1 的共用 DMA 请求。 |

| 10 | CH012 | ADC 通道 0、1 和 2 的共用 DMA 请求。 |

| 11 | CH0123 | ADC 通道 0、1、2 和 3 的共用 DMA 请求。 |

位 5:2 – CHSTART[3:0]: 通道开始单次转换

设置这些位中的任意一个将启动对应 ADC 通道的转换。

同时设置多个位将启动所选 ADC 通道的转换,转换从编号最低的通道开始。

当转换启动后,这些位会被硬件清零。

位 1 – FLUSH: 管道刷新

设置此位将刷新 ADC 管道。

刷新完成后,ADC 时钟将在下一个外设时钟边沿重新启动,所有正在进行的转换将被中止并丢失。

在刷新和 ADC 时钟重启后,ADC 会从其中断的地方继续运行;

例如,如果通道扫描正在进行或有待处理的转换,这些转换将进入 ADC 管道并完成。

位 0 – ENABLE: 启用

设置此位以启用 ADC。

0x01 CTRLB – ADC Control register B

IMPMODE 组配置描述

| 值 | 配置 | 描述 |

|---|---|---|

| 0 | HIGHIMP | 用于高阻抗源;输入端的电荷将被保留。 |

| 1 | LOWIMP | 用于低阻抗源。 |

CURRLIMIT[1:0] 组配置描述

| 值 | 配置 | 描述 |

|---|---|---|

| 00 | NO | 无限制。 |

| 01 | LOW | 低电流限制,最大采样率为 1.5MSPS。 |

| 10 | MED | 中等电流限制,最大采样率为 1MSPS。 |

| 11 | HIGH | 高电流限制,最大采样率为 0.5MSPS。 |

这些位可以通过降低ADC的最大采样速率来限制ADC的电流消耗。

位4 – CONVMODE: 转换模式

此位控制ADC工作在有符号模式还是无符号模式。默认情况下,此位清零,ADC配置为无符号模式。当此位被置位时,ADC配置为有符号模式。

位3 – FREERUN: 自由运行模式

当此位被置为1时,ADC进入自由运行模式,EVCTRL寄存器中定义的ADC通道将被反复扫描。

RESOLUTION[1:0] 配置与描述

| 值 | 组配置 | 描述 |

|---|---|---|

| 00 | 12BIT | 12位结果,右对齐 |

| 01 | Reserved | 保留 |

| 10 | 8BIT | 8位结果,右对齐 |

| 11 | LEFT12BIT | 12位结果,左对齐 |

0x02 REFCTRL – Reference Control register

Bits 6:4 – REFSEL[2:0]: 参考电压选择

REFSEL[2:0] | 配置组 | 描述 |

|---|---|---|

| 000 | INT1V | 带隙电压的 10/11(1.0V) |

| 001 | INTVCC | VCC/1.6 |

| 010 | AREFA | 来自 PORT A 的 AREF 引脚的外部参考 |

| 011 | AREFB | 来自 PORT B 的 AREF 引脚的外部参考 |

| 100 | INTVCC2 | VCC/2 |

| 101-111 | 保留 | 为未来使用或未分配的配置 |

| 以下是翻译内容: |

位 3:2 – 保留

这些位未使用,保留用于将来使用。为了与未来的设备兼容,写入该寄存器时应将这些位设置为零。

位 1 – BANDGAP:带隙电压启用

设置此位启用带隙电压用于 ADC 测量。请注意,如果其他功能已在使用带隙电压,则在内部 1.00V 参考电压用于另一个 ADC、DAC 或启用欠压检测时,无需设置此位。

位 0 – TEMPREF:温度参考启用

设置此位启用温度传感器用于 ADC 测量。

0x03 Event Control register

SWEEP[1:0] | 配置组 | 描述 |

|---|---|---|

| 00 | 0 | 仅激活 ADC 通道 0 |

| 01 | 01 | 激活 ADC 通道 0 和 1 |

| 10 | 012 | 激活 ADC 通道 0、1 和 2 |

| 11 | 0123 | 激活 ADC 通道 0、1、2 和 3 |

此配置组指定了进行通道扫描时激活的 ADC 通道。

EVSEL[2:0] | 配置组 | 描述 |

|---|---|---|

| 000 | 0123 | 选择事件通道 0、1、2 和 3 作为输入 |

| 001 | 1234 | 选择事件通道 1、2、3 和 4 作为输入 |

| 010 | 2345 | 选择事件通道 2、3、4 和 5 作为输入 |

| 011 | 3456 | 选择事件通道 3、4、5 和 6 作为输入 |

| 100 | 4567 | 选择事件通道 4、5、6 和 7 作为输入 |

| 101 | 567 | 选择事件通道 5、6 和 7 作为输入 |

| 110 | 67 | 选择事件通道 6 和 7 作为输入 |

| 111 | 7 | 选择事件通道 7 作为输入 |

此配置组指定了选定的事件通道作为输入来源。

EVACT[2:0] | 配置组 | 描述 |

|---|---|---|

| 000 | NONE | 无事件输入 |

| 001 | CH0 | 由 EVSEL 定义的编号最低的事件通道触发 ADC 通道 0 的转换 |

| 010 | CH01 | 由 EVSEL 定义的两个编号最低的事件通道分别触发 ADC 通道 0 和 1 的转换 |

| 011 | CH012 | 由 EVSEL 定义的三个编号最低的事件通道分别触发 ADC 通道 0、1 和 2 的转换 |

| 100 | CH0123 | 由 EVSEL 定义的事件通道触发 ADC 通道 0、1、2 和 3 的转换 |

| 101 | SWEEP | 由 EVSEL 定义的编号最低的事件通道触发所有由 SWEEP 定义的 ADC 通道的一次扫描 |

| 110 | SYNCSWEEP | 由 EVSEL 定义的编号最低的事件通道触发所有活动的 ADC 通道(由 SWEEP 定义)的一次扫描,同时 ADC 会被刷新并重新启动以确保精确计时 |

| 111 | Reserved | 保留 |

此配置组定义了选定事件输入的操作模式以及如何触发 ADC 通道的转换或扫描。

0x04 Clock Prescaler register

Bit 2:0 – PRESCALER[2:0]: Prescaler Configuration

PRESCALER[2:0] | 配置组 | 外设时钟分频因子 |

|---|---|---|

| 000 | DIV4 | 4 |

| 001 | DIV8 | 8 |

| 010 | DIV16 | 16 |

| 011 | DIV32 | 32 |

| 100 | DIV64 | 64 |

| 101 | DIV128 | 128 |

| 110 | DIV256 | 256 |

| 111 | DIV512 | 512 |

此配置组指定外设时钟的分频因子,用于调节时钟频率以适应具体的外围设备需求。

0x06 Interrupt Flag register

位 3:0 – CH[3:0]IF:中断标志位

当相应的 ADC 通道转换完成时,这些标志位会被设置。如果某个 ADC 通道被配置为比较模式,则当满足比较条件时,相应的标志位也会被设置。

- 当执行 ADC 通道

n的中断向量时,CHnIF会自动清除。 - 也可以通过向相应位位置写入“1”来手动清除该标志位。

0x07 Temporary register

该寄存器用于在ADC控制器中读取16位寄存器。当CPU读取16位寄存器的低字节时,高字节会存储在此寄存器中。此寄存器也可通过用户软件进行读写操作。

0xc Calibration Value register

CALL和CALH寄存器对存储12位校准值。

在生产编程过程中,会对ADC流水线进行校准,该校准值需要从签名区读取,并通过软件写入到CAL寄存器中。

位7:0 – CAL[7:0]:ADC校准值

这是12位CAL值的最低有效8位(LSBs)。

0x0d Calibration Value register

位3:0 – CAL[11:8]:校准值

这是12位CAL值的最高有效4位(MSBs)。

0x11/ 0x13/0x15/0x17 Channel n Result register High

以下是将上述内容格式化为表格的形式:

| 位 (Bit) | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| 12位,左对齐 | CHRES[11] | CHRES[10] | CHRES[9] | CHRES[8] | CHRES[7] | CHRES[6] | CHRES[5] | CHRES[4] |

| 12位,右对齐 | – | – | – | – | CHRES[11] | CHRES[10] | CHRES[9] | CHRES[8] |

| 8位 | – | – | – | – | – | – | – | – |

| 读/写 (R/W) | R | R | R | R | R | R | R | R |

| 初始值 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

0x10/ 0x12/0x14/0x16 Channel n Result register Low

以下是将内容格式化为表格的形式:

| 位 (Bit) | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| 12位/8位,右对齐 | CHRES[7] | CHRES[6] | CHRES[5] | CHRES[4] | CHRES[3] | CHRES[2] | CHRES[1] | CHRES[0] |

| 12位,左对齐 | CHRES[3] | CHRES[2] | CHRES[1] | CHRES[0] | – | – | – | – |

| 读/写 (R/W) | R | R | R | R | R | R | R | R |

| 初始值 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

0x19 Compare register High

位7:0 – CMP[15:0]:比较值高位

这是16位ADC比较值的高8位(MSBs)。在有符号模式下,数字采用二进制补码(2’s complement)表示,最高有效位(MSB)为符号位。

0x18 Compare register Low

位7:0 – CMP[7:0]:比较值低位

这是16位ADC比较值的低8位(LSBs)。在有符号模式下,数字采用二进制补码(2’s complement)表示。

ADC Channel寄存器

0x00 Channel Control register

位7 – START:启动通道转换

设置此位将启动该通道的转换。当转换开始时,硬件会清除此位。如果此位已经被设置,再次设置此位将没有任何效果。写入或读取此位相当于写入“CTRLA – 控制寄存器A”中的CH[3:0]START位。

位4:2 – GAIN[2:0]:增益因子

这些位定义了ADC增益阶段的增益因子。

| GAIN[2:0] | 组配置 | 增益因子 |

|---|---|---|

| 000 | 1X | 1x |

| 001 | 2X | 2x |

| 010 | 4X | 4x |

| 011 | 8X | 8x |

| 100 | 16X | 16x |

| 101 | 32X | 32x |

| 110 | 64X | 64x |

| 111 | DIV2 | ½x |

位1:0 – INPUTMODE[1:0]:通道输入模式

这些位定义了通道模式。改变输入模式将会破坏流水线中的任何数据。

当CONVMODE=0时(unsigned mode),定义如下:

| INPUTMODE[1:0] | 组配置 | 描述 |

|---|---|---|

| 00 | INTERNAL | 内部正输入信号 |

| 01 | SINGLEENDED | 单端正输入信号 |

| 10 | Reserved | 保留 |

| 11 | Reserved | 保留 |

当CONVMODE=1时(signed mode),定义如下:

| INPUTMODE[1:0] | 组配置 | 描述 |

|---|---|---|

| 00 | INTERNAL | 内部正输入信号 |

| 01 | SINGLEENDED | 单端正输入信号 |

| 10 | DIFF | 差分输入信号 |

| 11 | DIFFWGAIN | 带增益的差分输入信号 |

0x01 ADC Channel MUX Control registers

位6:3 – MUXPOS[3:0]:正ADC输入的多路复用选择

这些位定义了正ADC输入的多路复用选择。

当INPUTMODE[1:0]=00,内部输入时:

| MUXPOS[3:0] | 组配置 | 描述 |

|---|---|---|

| 0000 | TEMP | 温度参考 |

| 0001 | BANDGAP | 带隙电压 |

| 0010 | SCALEDVCC | 1/10比例缩小的VCC |

| 0011 | DAC | DAC输出 |

| 0100-1111 | Reserved | 保留 |

当INPUTMODE[1:0]=01/10,单端或差分输入时:

| MUXPOS[3:0] | 组配置 | 描述 |

|---|---|---|

| 0000 | PIN0 | ADC0 引脚 |

| 0001 | PIN1 | ADC1 引脚 |

| 0010 | PIN2 | ADC2 引脚 |

| 0011 | PIN3 | ADC3 引脚 |

| 0100 | PIN4 | ADC4 引脚 |

| 0101 | PIN5 | ADC5 引脚 |

| 0110 | PIN6 | ADC6 引脚 |

| 0111 | PIN7 | ADC7 引脚 |

| 1000 | PIN8 | ADC8 引脚 |

| 1001 | PIN9 | ADC9 引脚 |

| 1010 | PIN10 | ADC10 引脚 |

| 1011 | PIN11 | ADC11 引脚 |

| 1100 | PIN12 | ADC12 引脚 |

| 1101 | PIN13 | ADC13 引脚 |

| 1110 | PIN14 | ADC14 引脚 |

| 1111 | PIN15 | ADC15 引脚 |

当INPUTMODE[1:0] = 11 (差分带增益)时:

| MUXPOS[3:0] | 组配置 | 描述 |

|---|---|---|

| 0000 | PIN0 | ADC0 引脚 |

| 0001 | PIN1 | ADC1 引脚 |

| 0010 | PIN2 | ADC2 引脚 |

| 0011 | PIN3 | ADC3 引脚 |

| 0100 | PIN4 | ADC4 引脚 |

| 0101 | PIN5 | ADC5 引脚 |

| 0110 | PIN6 | ADC6 引脚 |

| 0111 | PIN7 | ADC7 引脚 |

| 1XXX | Reserved | 保留 |

位2:0 – MUXNEG[2:0]:负ADC输入的多路复用选择

当进行差分测量时,这些位定义了负ADC输入的多路复用选择。对于内部或单端测量,这些位不使用。

差分输入时:

| MUXNEG[2:0] | 组配置 | 模拟输入 |

|---|---|---|

| 000 | PIN0 | ADC0 引脚 |

| 001 | PIN1 | ADC1 引脚 |

| 010 | PIN2 | ADC2 引脚 |

| 011 | PIN3 | ADC3 引脚 |

| 100 | - | 保留 |

| 101 | GND | PAD 接地 |

| 110 | - | 保留 |

| 111 | INTGND | 内部接地 |

差分输入带增益时:

| MUXNEG[2:0] | 组配置 | 模拟输入 |

|---|---|---|

| 000 | PIN4 | ADC4 引脚 |

| 001 | PIN5 | ADC5 引脚 |

| 010 | PIN6 | ADC6 引脚 |

| 011 | PIN7 | ADC7 引脚 |

| 100 | INTGND | 内部接地 |

| 101 | - | 保留 |

| 110 | - | 保留 |

| 111 | GND | PAD 接地 |

0x02 Channel Interrupt Control registers

Bit 3:2 – INTMODE: 中断模式

| INTMODE[1:0] | 组配置 | 中断模式 |

|---|---|---|

| 00 | COMPLETE | 转换完成 |

| 01 | BELOW | 比较结果低于阈值 |

| 10 | Reserved | 保留 |

| 11 | ABOVE | 比较结果高于阈值 |

位1:0 – INTLVL[1:0]:中断优先级级别和使能

这些位使能ADC通道中断并选择中断级别。

0x03 ADC Channel Interrupt Flag registers

位0 – IF:通道中断标志

当ADC转换完成时,中断标志将被设置。如果通道配置为比较模式,当比较条件满足时,标志也会被设置。执行ADC通道中断向量时,IF位会被自动清除。该位也可以通过向该位写入1来手动清除。

0x05 – Channel n Result register High

| 位 (Bit) | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| 12-bit, left | RES[11] | RES[10] | RES[9] | RES[8] | RES[7] | RES[6] | RES[5] | RES[4] |

| 12-bit, right | – | – | – | – | RES[11] | RES[10] | RES[9] | RES[8] |

| 8-bit | – | – | – | – | – | – | – | – |

说明:

- RES[11:4]:这是12位ADC分辨率的左半部分。

- RES[11:8]:这是12位ADC分辨率的右半部分。

- 读取/写入:该寄存器的值为只读(R),具体定义的位的访问方式由硬件设定。

0x04 Channel n Result register Low

12-/8-bit模式

- 位7:0 – RES[7:0]:通道结果低位

这些是ADC结果的最低8位(LSBs)。

12-bit模式,左对齐

- 位7:4 – RES[3:0]:通道结果低位

这些是12位ADC结果的最低4位(LSBs)。

0x06 Channel Scan register

-

位7:4 – OFFSET[3:0]:正MUX设置偏移

当 COUNT 不等于0时,通道扫描被启用。此寄存器包含下一输入源的偏移,该输入源将在ADC通道0(CH0)上进行转换。正输入的实际MUX设置为 MUXPOS + OFFSET。该值会在每次转换后递增,直到达到 COUNT 给定的最大值。当 OFFSET 等于 COUNT 时,OFFSET 会在下一次转换时清除。 -

位3:0 – COUNT[3:0]:扫描中包含的输入通道数量

此寄存器表示扫描中包含的输入源数量。包含的输入源数量为 COUNT + 1。包含的输入通道范围为 MUXPOS 到 MUXPOS + COUNT。

862

862

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?