文章目录

前言

早期,提出虚拟内存的主要动机有两个:允许在多个程序之间高效地共享内存;消除小而受限的主存容量对程序设计造成的影响(即用户程序可能会超出内存容量的内存)。现在,第一条变成主要设计动机。为了更加高效地管理内存并且减少出错,现代系统提供了一种对主存的抽象概念,叫做虚拟内存(VM)。虚拟内存是硬件异常、硬件地址翻译、主存、磁盘文件和内核软件的完美交互,它为每个进程提供了一个大的、一致的和私有的地址空间。

一、虚拟内存三个重要功能?

-

它将主存看成是一个存储在磁盘上的地址空间的高速缓存,在主存中只保存活动区域,并根据需要在磁盘和主存之间来回传送数据,通过这种方式,高效的使用了主存。(主存也可以为通常由磁盘实现的辅助存储器充当"cache")

-

它为每个进程提供了一致的地址空间,从而简化了内存管理。

-

它保护了每个进程的地址空间不被其他进程破坏。

二、物理和虚拟寻址

1.物理寻址

计算机系统的主存被组织成一个由M个连续的字节大小的单元组成的数组。每个字节都有一个唯一的物理地址(physical address, PA)。第一个字节的地址为0,接下来的字节地址为1,依此类推。CPU访问内存的最自然的方式就是使用物理地址。称这种方式为物理寻址。

2.虚拟寻址

使用虚拟寻址,cpu通过生成一个虚拟地址(Virtual Address, VA)来访问主存,这个虚拟地址在被送到内存之前先转换成适当的物理地址。将一个虚拟地址转换为物理地址的任务叫做地址翻译(address translation)。就像异常处理一样,地址翻译需要cpu硬件和操作系统之间的紧密合作。cpu芯片上叫做内存管理单元(Memory Management Unit, MMU)的专用硬件,利用存放在主存中的查询表来动态翻译虚拟地址,该表的内容由操作系统管理。

3.虚拟内存作为缓存的工具

虚拟内存被组织为一个由存放在磁盘上的N个连续的字节大小的单元组成的数组。每字节都有一个唯一的虚拟地址,作为到数组的索引。磁盘上数组的内容被缓存在主存中。和存储器层次结构中其它缓存一样,磁盘(较低层)上的数据被分割成块,这写块作为磁盘和主存(较高层)之间的传输单元。VM系统通过将虚拟内存分割为虚拟页的大小固定的块来处理这个问题。

在任意时刻,虚拟页面的集合都分为三个不相交的子集:

- 未分配的,VM系统还未分配的页,未分配的块没有任何数据和它们相关联,因此也就不占任何磁盘空间。

- 缓存的,当前已缓存在物理内存中的已分配页。

- 未缓存的,未缓存在物理内存中的已分配页。

三、基于页面的虚拟内存

S模式提供了一种传统的虚拟内存,它将内存划分为固定大小的页来进行地址转换和对内存内容的保护。启用分页的时候,大多数地址(包括load和store的有效地址和PC中的地址)都是虚拟地址,要访问物理内存,它们必须被转换为真正的物理地址,通过遍历页表的高基数树实现。页表中的叶节点指示是否已经被映射到了真正的物理页面,如果是,则指示了那些权限模式和通过哪种类型的访问可以操作这个页。访问未被映射的页或访问权限不足会导致页错误异常(page fault exception)。

1.页表

同任何缓存一样,虚拟内存系统必须有某种方法判定一个虚拟页是否缓存在DRAM中的某个地方。如果是,系统还必须确定这个虚拟页存放在那个物理页中。如果不命中,系统必须判断这个虚拟页存放在磁盘的那个位置,在物理内存中选择一个牺牲页,并将虚拟页从磁盘复制到DRAM中,替换这个牺牲页。这些功能由软硬件联合提供,包括操作系统软件、MMU中的地址翻译硬件和一个存放在物理内存中的页表(page table)结构,页表将虚拟页映射到物理页。每次地址翻译硬件将一个虚拟地址转换为物理地址时,都会读取页表。操作系统负责维护页表的内容,以及在磁盘与DRAM之间来回传送页。

页表就是一个页表项(page table entry, PTE)的数组。虚拟地址空间中的每个页在页表中一个固定偏移量处都有一个PTE。根据PTE中的有效位判断,表明该虚拟页当前是否被缓存在DRAM中。如果设置了有效位,那么地址字段就表示DRAM中相应的物理页的起始位置,这个物理页中缓存了该虚拟页。如果没有设置效位,那么一个空地址表示这个虚拟页还未被分配。否则,这个地址就指向该虚拟页磁盘上的起始位置。

2.RISC-V分页方案

RISC-V的分页方案以SvX的模式命名,X是以位为单位的虚拟地址的长度。

-

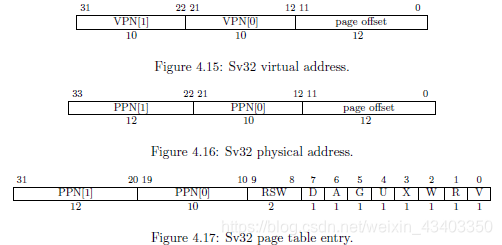

RV32的分页方案Sv32支持4GiB的虚址空间,这些空间被划分为2^10 个4KiB大小的基页(分页的基本单位)。因此,Sv32的页表是基数为2 ^10的两级树结构(两级页表查找)。页表中每个项的大小是四个字节,因此页表本身的大小是4KiB。页表的大小和每个页的大小完全相同,这样的设计简化了操作系统的内存分配。

-

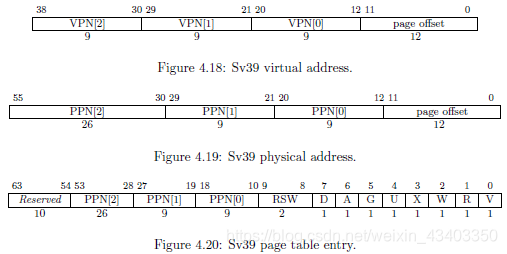

RV64支持多种分页方案,Sv39使用和Sv32相同的4KiB大的基页。页表项的大小变成8个字节,所以它们可以容纳更大的物理地址。为了保证页表大小和页面大小一致,树的基数相应地降到2 ^9,树也变为三层(三级页表查找)。Sv39的512GiB地址空间划分为2 ^9个1GiB大小的吉页。每个吉页被进一步划分为2 ^9个巨页。在Sv39中这些巨页大小为2MiB,比Sv32中略小。每个巨页再进一步分为2 ^9个4KiB大小的基页。

-

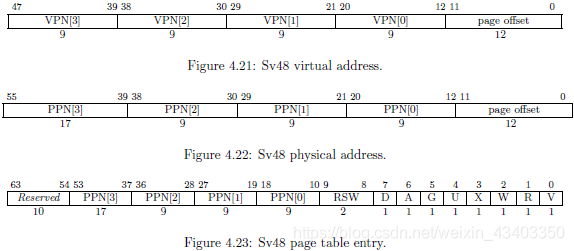

其他RV64分页方案只是向页表添加更多级别。Sv48与Sv39几乎相同,但其虚拟地址空间大2 ^9倍,页表更深一层(四级页表查找)。

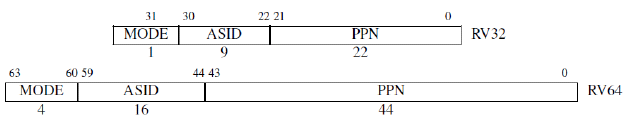

3.分页系统控制

S模式控制状态寄存器satp(Supervisor Address Translation and protection, 监管者地址转换和保护)控制了分页系统。satp有三个域。MODE域可以开启分页并选择页表级数,ASID(Address Space Identifier, 地址空间标识符)域是可选的,它可以用来降低上下文切换的开销。最后,PPN字段保存了根页表的物理地址,它以4KiB的页面大小为单位。通常M模式的程序在第一次进入S模式之前会把零写入satp以禁用分页,然后S模式的程序在初始化页表以后再次进行satp寄存器的写操作。

当在satp寄存器中启用了分页时,S模式和U模式中的虚拟地址会以从根部遍历页表的方式转换为物理地址。satp.PPN给出了一级页表的基址,最终计算出实际访问的物理地址。随后处理器会进行物理内存的访问。

如果所有取指,load和store操作都导致多次页表访问,那么分页会大大降低性能,所有现代的处理器都用地址转换缓存(TLB,Translation Lookaside Buffer)来减少这种开销。为了降低这个缓存本身的开销,大多数处理器不会让它时刻与页表保持一致。这意味着如果操作系统修改了页表,那么这个缓存会变得陈旧而不可用。S模式添加了一条指令来解决这个问题。sfence.vma会通知处理器,软件可能已经修改了页表,于是处理器可以相应地刷新转换缓存。它需要两个可选的参数,这样可以缩小缓存刷新的范围。一个位于rs1,它指示了页表哪个虚址对应的转换被修改了;另一个位于rs2,它给出了被修改页表的进程的地址空间标识符(ASID)。如果两者都是X0,便会刷新整个转换缓存。

4.虚址到物理地址的转换算法

- Sv32:1.satp.PPN给出了一级页表的基址,VA[31:22]给出了一级页号,因此处理器会读取位于地址(satp.PPN*4096+VA[31:22]4)的页表项。

2. 该PTE包含二级页表的基址,VA[21:12]给出了二级页号,因此处理器读取位于地址(PTE.PPN4096+VA[21:12]4)的页节点页表项。

3. 叶节点页表项的PPN字段和页内偏移(原始虚址的最低12个有效位)组成了最终结果:物理地址就是(leafPTE.PPN4096+VA[11:0])。

- Sv39:27bitVPN通过三级页表转换为44bit的PPN,12bit页偏移量不需要翻译。Sv39页表包含512个PTE,每个PTE8个字节。

- Sv48:36bit VPN通过四级页表转换为44bit的PPN,12bit的偏移量不需要翻译。

本文深入探讨了虚拟内存的重要功能,包括作为缓存、提供一致的地址空间和保护进程的地址空间。介绍了物理寻址与虚拟寻址的概念,并详细阐述了基于页面的虚拟内存,特别是RISC-V架构下的分页方案。通过页表和地址转换算法,解释了如何将虚拟地址映射到物理地址。此外,还讨论了分页系统控制,如SATP寄存器和TLB刷新。

本文深入探讨了虚拟内存的重要功能,包括作为缓存、提供一致的地址空间和保护进程的地址空间。介绍了物理寻址与虚拟寻址的概念,并详细阐述了基于页面的虚拟内存,特别是RISC-V架构下的分页方案。通过页表和地址转换算法,解释了如何将虚拟地址映射到物理地址。此外,还讨论了分页系统控制,如SATP寄存器和TLB刷新。

3399

3399

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?