1、物理内存属性(PMA:Physical Memory Attributes)

(1)系统内存映射包含各种不同属性的地址空间范围,每个地址空间范围支持的操作不一样;

(2)物理内存属性一般是在芯片设计阶段就固定下来(大部分芯片不支持软件修改),芯片内存有PAM检测器,PMA检测器会对物理地址权限和属性做检查;

2、物理内存保护

2.1、物理内存保护的作用(PMP:Physical Memory Protection)

(1)在RISC-V体系结构中,M模式具有最高权限,拥有访问系统全部资源的权限。

默认情况下,S模式和U模式对内存映射的任何区域没有读、写、执行权限,除非配置PMP来允许S模式和U模式访问;

(2)在M模式下,只有PMP配置项的L字段是锁定状态,M模式才会去检查PMP权限;

作用:如果我们对某些地址范围有特殊需求,可以通过PMP来设置,防止出错;比如某个地址范围的数据希望只读不可写,可以设置PMP把这段地址范围设置成只读不可写属性,这样当有代码尝试修改数据时就会报错,防止误操作;

2.2、PMP配置寄存器

2.2.1、PMP配置寄存器数量

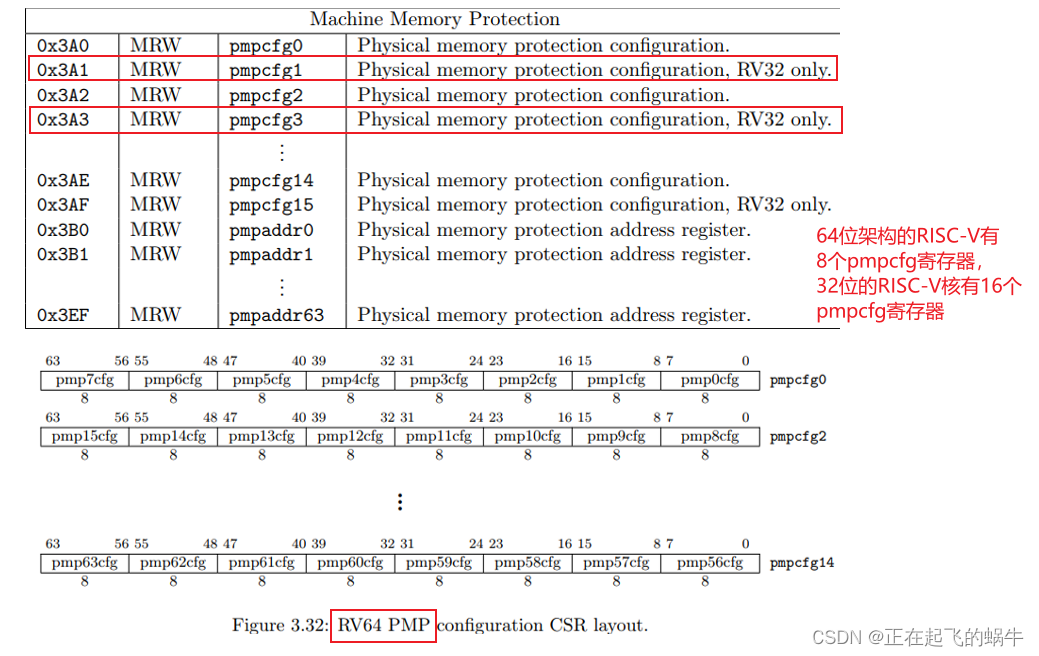

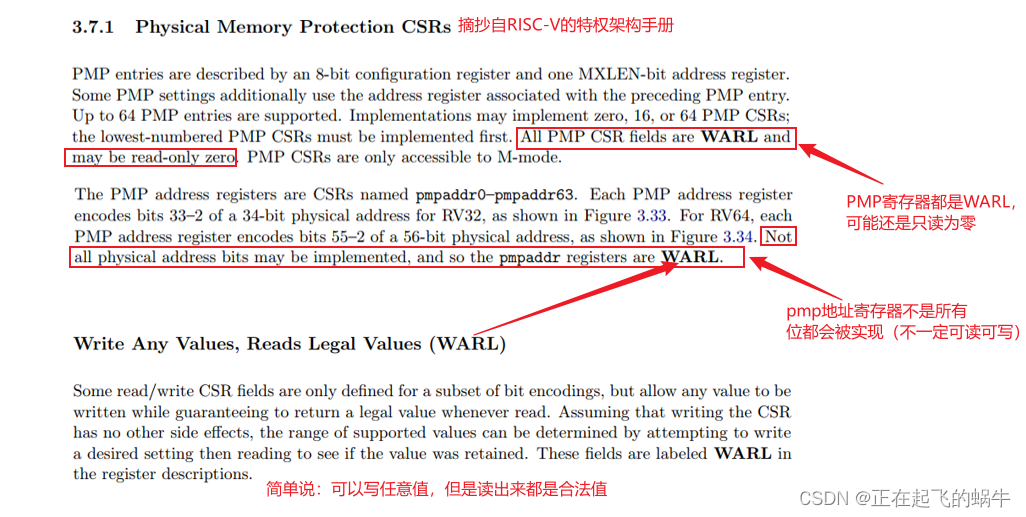

(1)RISC-V规定最多支持64个PMP配置项,也就是最多支持对64个地址范围做权限设置;

(2)每个地址范围对于的PMP配置表项是8位,要保存64个PMP配置项,64位RISC-V核只需要8个寄存器,32位RISC-V核需要16个寄存器;

(3)为了统一命名,64位RISC-V的pmpcfg寄存器只有pmpcfg0、pmpcfg2,只有双数的;

2.2.2、PMP配置表项

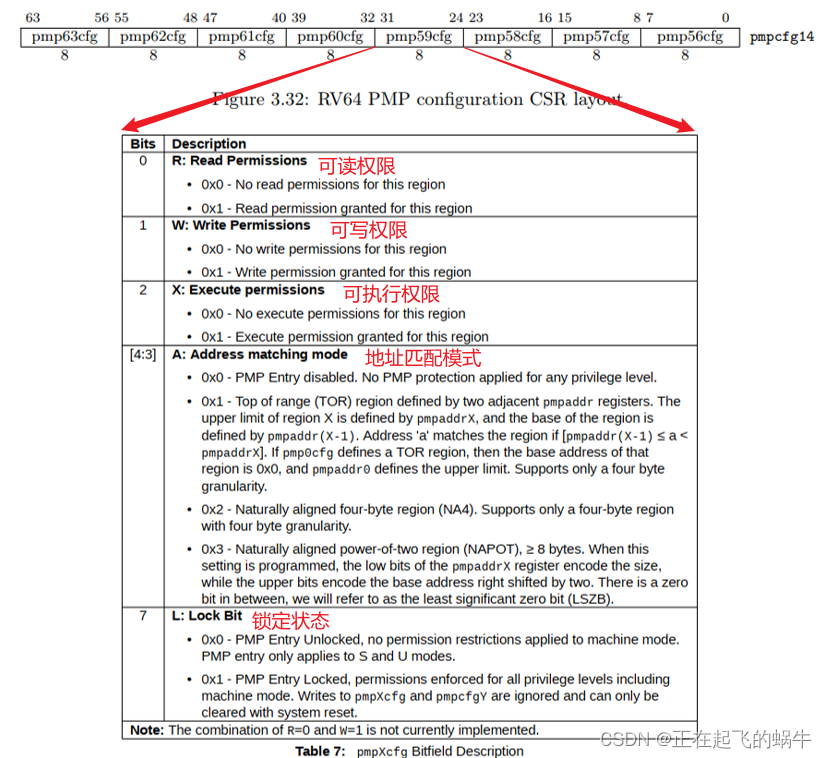

(1)地址匹配模式:怎么去计算配置的地址范围,见下一节;

(2)锁定状态:锁定状态下M模式需要去检查地址范围的权限;非锁定状态下,M模式拥有全部权限,不受PMP配置的权限限制;

2.2.3、地址匹配模式

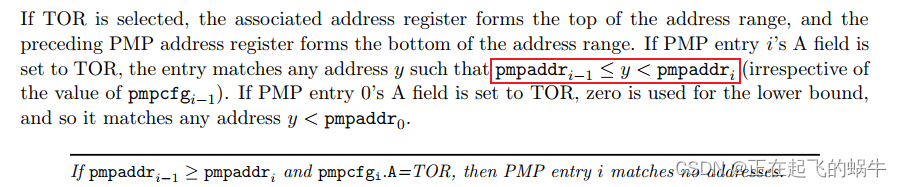

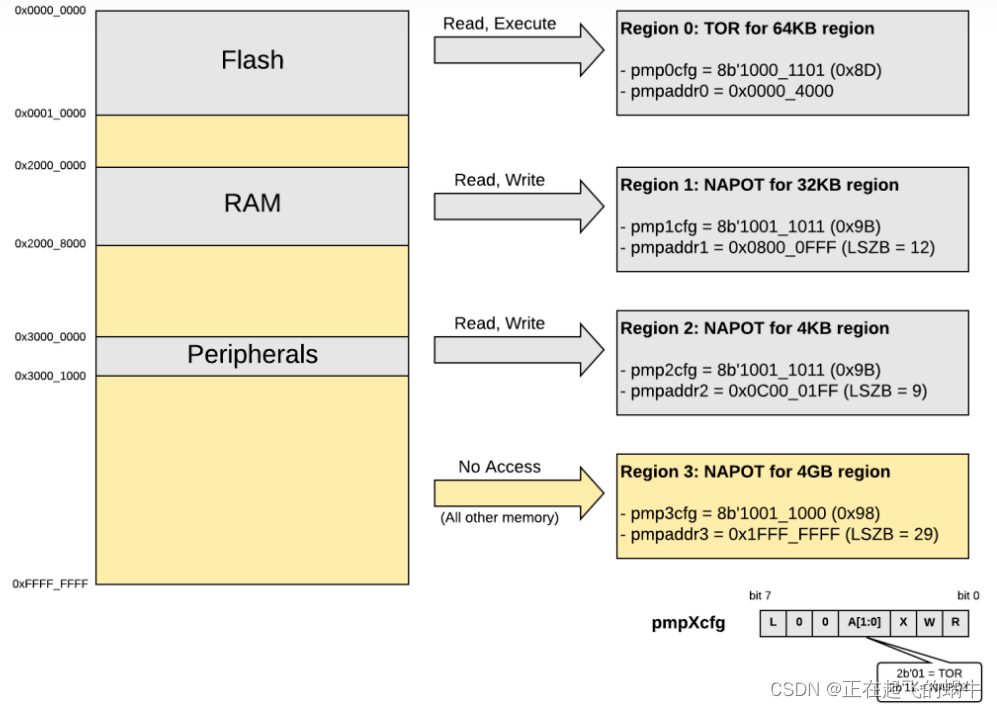

2.2.3.1、TOR模式

表示地址范围由相邻两个pmpaddr寄存器的值决定;

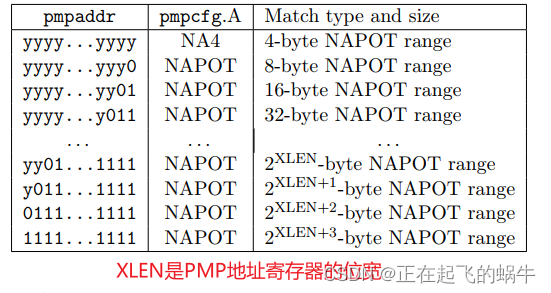

2.2.3.2、NAPOT模式

表示的地址范围:pmp地址寄存器的值从bit0开始连续1的个数为n,则表示的地址范围是2的(n+3)次方字节;

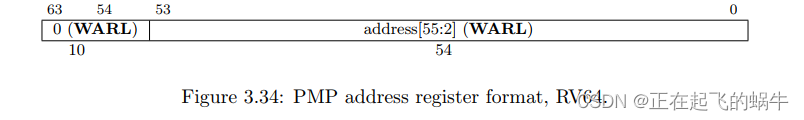

2.3、PMP地址寄存器

(1)pmp地址寄存器的bit[53:0]保存物理地址范围的bit[55:2];

2.4、如何配置一段物理内存地址的保护属性?

以RAM地址为例:

(1)地址权限是可读可写,所有8位pmp配置项的值为0x9B;

(2)起始地址0x20000000右移2位,变成0x8000000;

(3)RAM的地址范围是0x8000,也就是2的15次方,pmpaddr寄存器中的值需要15-3=12个连续低位1,即0x8000FFF;

3、opensbi中物理内存保护设置函数分析

4、注意事项

(1)可以参考玄铁C906的PMP模块说明,其中PMP地址寄存器的低九位就是WARL(可以写任意值,但是读出来都是0);

(2)参考博客:《玄铁C906——物理内存保护(PMP)介绍》;

本文详细介绍了RISC-V体系结构中的物理内存属性(PMA)和物理内存保护(PMP)机制,包括PMP的作用、配置寄存器、地址匹配模式以及在opensbi中的设置函数。特别提到了玄铁C906的PMP模块和注意事项。

本文详细介绍了RISC-V体系结构中的物理内存属性(PMA)和物理内存保护(PMP)机制,包括PMP的作用、配置寄存器、地址匹配模式以及在opensbi中的设置函数。特别提到了玄铁C906的PMP模块和注意事项。

14万+

14万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?