1. 显示屏设备树节点

panel-rgb {

compatible = "simple-panel";

bus-format = <MEDIA_BUS_FMT_RGB666_1X24_CPADHI>;

backlight = <&backlight>;

enable-gpios = <&gpio0 RK_PC5 GPIO_ACTIVE_HIGH>;

reset-gpios = <&gpio0 RK_PC7 GPIO_ACTIVE_LOW>;

reset-delay-ms = <5>;

status = "okay";

rockchip,cmd-type = "spi";

spi-sdi-gpios = <&gpio0 RK_PB6 GPIO_ACTIVE_HIGH>;

spi-scl-gpios = <&gpio0 RK_PB5 GPIO_ACTIVE_HIGH>;

spi-cs-gpios = <&gpio0 RK_PC6 GPIO_ACTIVE_HIGH>;

pinctrl-names = "default";

pinctrl-0 = <&spi0m0_pins_gpio &spi0m0_cs0>;

panel-init-sequence = [

00 00 01 FF

01 00 01 77

01 00 01 01

01 00 01 00

01 00 01 00

01 00 01 13

00 00 01 EF

01 00 01 08

00 00 01 FF

01 00 01 77

01 00 01 01

01 00 01 00

01 00 01 00

01 00 01 10

00 00 01 C0

01 00 01 4F

01 00 01 00

00 00 01 C1

01 00 01 10

01 00 01 02

00 00 01 C2

01 00 01 07

01 00 01 02

00 00 01 CC

01 00 01 10

00 00 01 CD //RGB18BIT--DB0-17

01 00 01 08

00 00 01 B0

01 00 01 06

01 00 01 16

01 00 01 1E

01 00 01 0E

01 00 01 12

01 00 01 06

01 00 01 0A

01 00 01 08

01 00 01 09

01 00 01 23

01 00 01 04

01 00 01 12

01 00 01 10

01 00 01 2B

01 00 01 31

01 00 01 1F

00 00 01 B1

01 00 01 06

01 00 01 0F

01 00 01 16

01 00 01 0D

01 00 01 10

01 00 01 07

01 00 01 04

01 00 01 09

01 00 01 07

01 00 01 20

01 00 01 05

01 00 01 12

01 00 01 10

01 00 01 26

01 00 01 2F

01 00 01 1F

00 00 01 FF

01 00 01 77

01 00 01 01

01 00 01 00

01 00 01 00

01 00 01 11

00 00 01 B0

01 00 01 65

00 00 01 B1

01 00 01 81

00 00 01 B2

01 00 01 82

00 00 01 B3

01 00 01 80

00 00 01 B5

01 00 01 42

00 00 01 B7

01 00 01 85

00 00 01 B8

01 00 01 20

00 00 01 C1

01 00 01 78

00 00 01 C2

01 00 01 78

00 00 01 D0

01 00 01 88

00 00 01 EE

01 00 01 42

00 00 01 E0

01 00 01 00

01 00 01 00

01 00 01 02

00 00 01 E1

01 00 01 04

01 00 01 A0

01 00 01 06

01 00 01 A0

01 00 01 05

01 00 01 A0

01 00 01 07

01 00 01 A0

01 00 01 00

01 00 01 44

01 00 01 44

00 00 01 E2

01 00 01 00

01 00 01 00

01 00 01 00

01 00 01 00

01 00 01 00

01 00 01 00

01 00 01 00

01 00 01 00

01 00 01 00

01 00 01 00

01 00 01 00

01 00 01 00

00 00 01 E3

01 00 01 00

01 00 01 00

01 00 01 22

01 00 01 22

00 00 01 E4

01 00 01 44

01 00 01 44

00 00 01 E5

01 00 01 0C

01 00 01 90

01 00 01 A0

01 00 01 A0

01 00 01 0E

01 00 01 92

01 00 01 A0

01 00 01 A0

01 00 01 08

01 00 01 8C

01 00 01 A0

01 00 01 A0

01 00 01 0A

01 00 01 8E

01 00 01 A0

01 00 01 A0

00 00 01 E6

01 00 01 00

01 00 01 00

01 00 01 22

01 00 01 22

00 00 01 E7

01 00 01 44

01 00 01 44

00 00 01 E8

01 00 01 0D

01 00 01 91

01 00 01 A0

01 00 01 A0

01 00 01 0F

01 00 01 93

01 00 01 A0

01 00 01 A0

01 00 01 09

01 00 01 8D

01 00 01 A0

01 00 01 A0

01 00 01 0B

01 00 01 8F

01 00 01 A0

01 00 01 A0

00 00 01 EB

01 00 01 00

01 00 01 00

01 00 01 E4

01 00 01 E4

01 00 01 44

01 00 01 00

01 00 01 40

00 00 01 ED

01 00 01 FF

01 00 01 F5

01 00 01 47

01 00 01 6F

01 00 01 0B

01 00 01 A1

01 00 01 AB

01 00 01 FF

01 00 01 FF

01 00 01 BA

01 00 01 1A

01 00 01 B0

01 00 01 F6

01 00 01 74

01 00 01 5F

01 00 01 FF

00 00 01 EF

01 00 01 08

01 00 01 08

01 00 01 08

01 00 01 40

01 00 01 3F

01 00 01 64

00 00 01 FF

01 00 01 77

01 00 01 01

01 00 01 00

01 00 01 00

01 00 01 00

00 00 01 FF

01 00 01 77

01 00 01 01

01 00 01 00

01 00 01 00

01 00 01 13

00 00 01 E6

01 00 01 16

01 00 01 7C

00 00 01 E8

01 00 01 00

01 00 01 0E

00 00 01 FF

01 00 01 77

01 00 01 01

01 00 01 00

01 00 01 00

01 00 01 00

00 1E 01 11

00 00 01 FF

01 00 01 77

01 00 01 01

01 00 01 00

01 00 01 00

01 00 01 13

00 00 01 E8

01 00 01 00

01 0A 01 0C

00 00 01 E8

01 00 01 00

01 00 01 00

00 00 01 FF

01 00 01 77

01 00 01 01

01 00 01 00

01 00 01 00

01 00 01 00

00 00 01 3A

01 00 01 66 //18bit,RGB666

00 00 01 35

01 00 01 00

00 00 01 29

];

display-timings {

native-mode = <&fx070_dhm11boe_timing>;

fx070_dhm11boe_timing: timing0 {

clock-frequency = <24000000>;

hactive = <480>;

vactive = <640>;

hback-porch = <70>;

hfront-porch = <40>;

vback-porch = <14>;

vfront-porch = <18>;

hsync-len = <12>;

vsync-len = <2>;

hsync-active = <0>;

vsync-active = <0>;

de-active = <0>;

pixelclk-active = <0>;

};

};

port {

panel_in_rgb: endpoint {

remote-endpoint = <&rgb_out_panel>;

};

};

};

1. 显示屏采用SPI接口以9bit格式发送初始化序列,然后使用RK3568的RGB信号驱动

2. 由于RK3568的硬件SPI仅支持8/16位格式,因此底层是用GPIO模拟SPI的,不过RK的panel-simple.c 已经实现了这个功能了

3. RGB接口在RK3588中已经取消,在RK3568中只能使用VOP中的VP2,即第三个显示控制器来输入

RGB接口类型说明

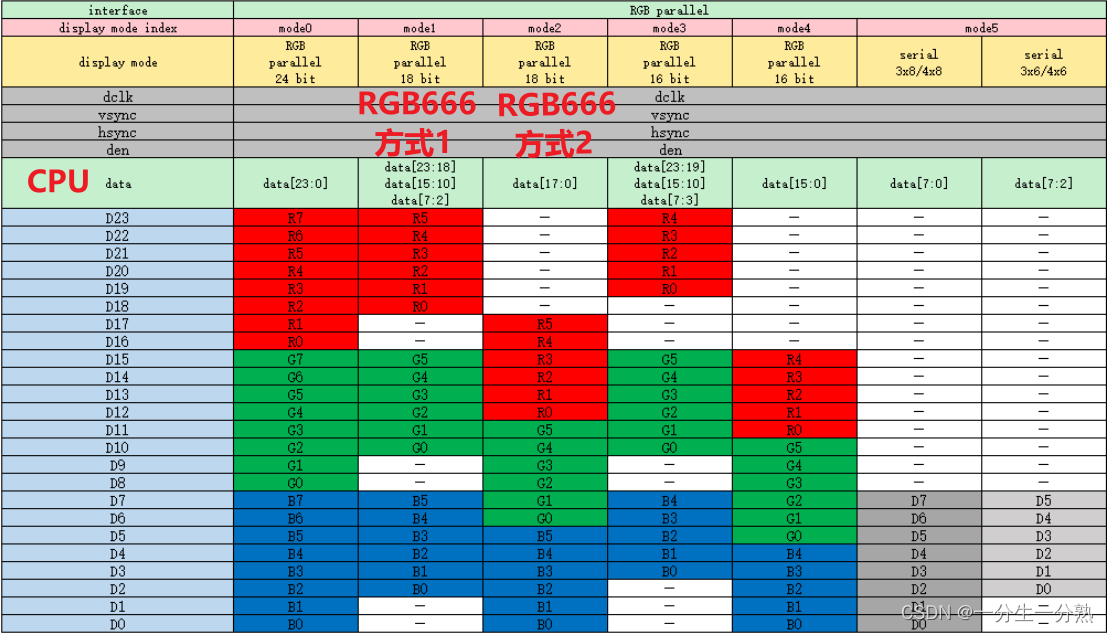

我使用的链接方式是RGB666,对下面几种总线格式简单说明一下

MEDIA_BUS_FMT_RGB666_1X18

MEDIA_BUS_FMT_RGB666_1X24_CPADHI

MEDIA_BUS_FMT_RBG888_1X24

早期的处理器可以根据配置修改显示屏和CPU之间的连接方式:(比如RK3399)

MEDIA_BUS_FMT_RGB666_1X24_CPADHI 对应方式1

MEDIA_BUS_FMT_RGB666_1X18 对应方式2

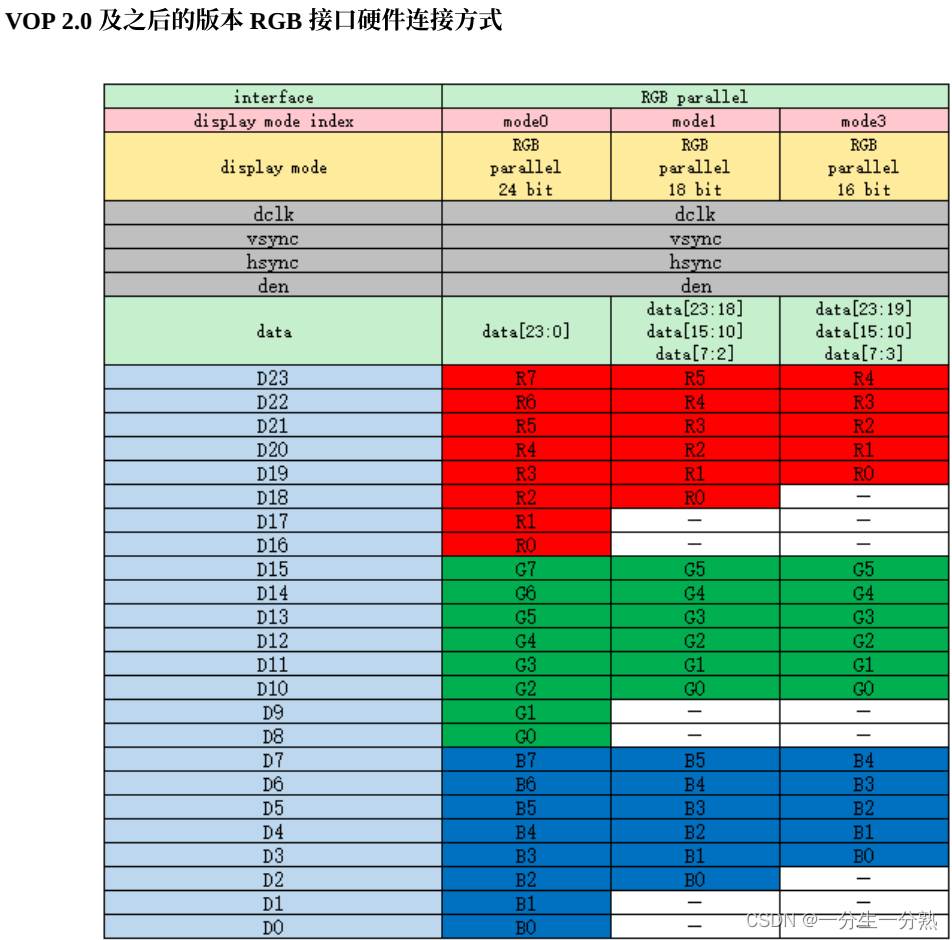

不过到了 RK3568 之后的CPU

MEDIA_BUS_FMT_RGB666_1X18 和

MEDIA_BUS_FMT_RGB666_1X24_CPADHI 已经没区别了

MEDIA_BUS_FMT_RBG888_1X24 方式用于RGB888

SPI 初始化序列

上面的参数 panel-init-sequence 是控制发送给SPI的初始化序列,根据不同厂商提供,原理很简单,就是比较长,我不说了!

RGB 时序序列

上面的参数display-timings 是控制RK3568的RGB信号,根据不同屏幕手册提供,原理很简单,就是比较简单,我不说了!

157

157

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?