结构化描述是用Verilog HDL 进行电路设计中最基本描述方式。对于系统级电路设计,为了把不同的功能模块有层次地组合在一起,主要是采用模块调用的结构化建模方式实现。

根据所调用子模块的不同抽象级别,可将模块的结构描述分成模块级建模、门级建模、开关级建模三类。

模块级建模通过调用有用户设计生成的低级子模块来对硬件电路结构进行说明,模块由低级模块的实例组成。

门级建模通过调用Verilog HDL内部的基本门级元件来对硬件电路结构进行说明,模块由基本门级元件的实例组成。

开关级建模通过调用Verilog HDL内部的基本开关元件来对硬件电路结构进行说明,模块由基本开关元件的实例组成。

- 模块

模块(module)表示一个基本的功能块,用于描述电路的特定功能及其通信端口。小到一个基本晶体管,大到一个复杂的微处理器系统,都可以作为一个模块来设计。一个复杂的数字系统一般由多个模块(module)构成,一个模块(module)的设计对应着系统设计中的某个功能模块,模块(module)的调用也对应这数字电路中某个功能的调用。模块设计可以采用行为描述,结构描述、数据流描述等多种描述方式。

一个模块的基本结构主要包括模块定义、模块端口定义、模块数据类型声明、模块参数声明、模块逻辑功能描述等几个基本部分。 在模块中只有module、模块名和endmodule必须出现,其他皆为可选部分。一个Verilog源文件(.v文件)中可以定义多个模块,Verilog HDL对模块的排列顺序没有要求。

module name(端口列表); //模块定义行

...端口定义...

...数据类型声明...

...参数声明...

...逻辑功能描述...

endmodule //模块结束行

端口是模块(module)与外界或其他模块沟通的信号线。端口列表里定义了外部可见的端口。端口类型有输入端口(input)、输出端口(output)和双向端口(inout)三种。有些模块(module)不包括端口,如仿真平台的顶层模块,所有的设计模块和激励模块是一个封闭的系统,没有输入和输出。

数据类型用于表示数字硬件系统中的数据存储和传输元素。Verilog有两组主要的数据类型:变量(variable)数据类型和网络(net)数据类型。这两个组在分配和保存值的方式上有所不同,它们表示不同的硬件结构。

参数型变量使用关键字parameter定义,在同一个模块中每个参数型变量的值必须为一个常量。在模块中使用参数可以增加程序的可读性和可维护性。

模块逻辑功能描述主要包括变量声明、数据流语句、底层模块实例,行为语句块、以及任务和函数五个组成部分,这些部分可以在模块的任意位置以任意顺序出现。

- 门级元件

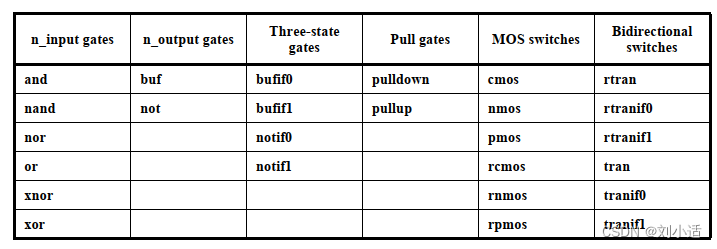

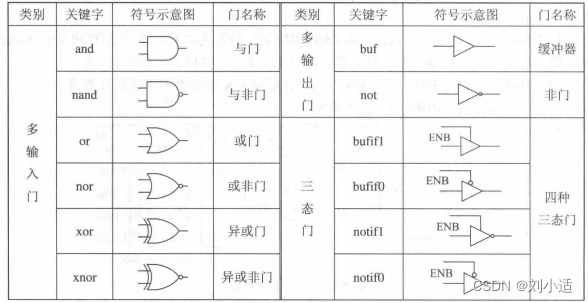

Verilog HDL 中规定了14个门级元件,其分为多输入门、多输出门、三态门和上下拉门(电阻)。其调用信号是1bit信号形式,位置按照输出信号、输入信号和控制信号排列。固定位置和把信号类型使得调用门级元件时,可以不用定义中间连接信号类型(wire)。

-

开关元件

Verilog 中规定了12个开关元件,分为MOS开关和双向开关。MOS开关只提供了信号的单向驱动能力,双向开关具有双向驱动能力,双向开关每个脚都被声明为inout类型,可以作为输入驱动另一脚,也可以作为输出被另一脚驱动。 -

模块调用

上述的模块(module),门级元件,开关元件在结构化建模中都可被视为电路调用的子模块。

模块调用的语法格式为:

//基本调用格式:

模块名<参数值列表>实例名(端口名列表);

//同一模块被当前模块多次调用方法1:

模块名<参数值列表>实例名1(端口名列表1);

<参数值列表>实例名2(端口名列表2);

......

<参数值列表>实例名n(端口名列表n);

//同一模块被当前模块多次调用方法2:

<被调用模块名><实例阵列名>[阵列左边界:阵列右边界]

例:

module and(ina, inbox,dout);

input ina,inb;

output dout;

assign dout = ina&inb;

endmodule

module array(a,b,out);

inpput [3:0] a,b;

output [3:0] out;

wire [3:0] out;

and and_array[3:0](out,a,b);

endmodule

模块级建模中,需要将被调用模块的输入和输出信号连接到调用模块中。Verilog提供了两种端口对应方式:端口位置对应和端口名称对应。

//端口位置对应语法:

模块名<参数值列表>实例名(<信号名1>,<信号名2>,...,<信号名n>);

//端口名称对应方式:

模块名<参数值列表>实例名(.端口名1(<信号名1>),.端口名2(<信号名2>),...,.端口名n(<信号名n>));

调用过程端口未匹配情形:原则上,用Verilog结构化描述进行电路设计时,端口位宽未匹配是被禁止的,因为位宽不匹配会对电路产生不稳定影响。当结构化描述过程中产生Verilog HDL语法中规定了相应的处理情况。

未连接端口:模块未连接输入端的值被置为 z。模块未连接的输出端表示该输出端口没有被使用。在CMOS电路中,这种情况是一定要避免的。

不同的端口位宽:在被调用模块端口和调用模块的端口表达式(调用信号)之间存在着一种隐含的连续赋值关系。因此,当端口和端口表达式(调用信号)的位宽不一致时,会进行端口匹配,采用的位宽匹配规则为右对齐(低位对齐)方式。

例:模块端口连接

module connect(a,b);

input [6:1] a;

output [3:0] b;

......

endmodule

module tb;

wire [5:3] c;

wire [5:1] d;

connect U1(.a(c),.b(d));

......

endmodule

c[3]、 c[4]、c[5] 分别和a[1]、a[2]、 a[3] 相连接,输入端口a剩余的位没有连接。同样,d[1]、 d[2]、d[3]、d[4] 分别连接到输出端口b的b[0]、b[1]、b[2]、 b[3] 上。

相关文献:

《Verilog HDL 数字集成电路高级程序设计》,蔡觉平等。

IEEE std 1800-2017 .

1866

1866

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?