今天突然有个疑问点Layout L与Layout XL有什么区别,在正常做版图的时候,我们一般怎么选择?

Layout L与Layout XL区别

- Cadence许多产品都会通过L、XL、GXL等代号表示不同级别,功能不断是增强

- 感觉版本迭代一样,1.0,2.0,3.0一样,但是不一定说Layout XL就比Layout L好,我觉得这个可能是要从需求出发的,如果是用不上Layout XL的功能直接用Layout L就好

- L只是basic的

- XL和GXL都具备电路图驱动和连接驱动的编辑模式

- GXL是“most advanced”

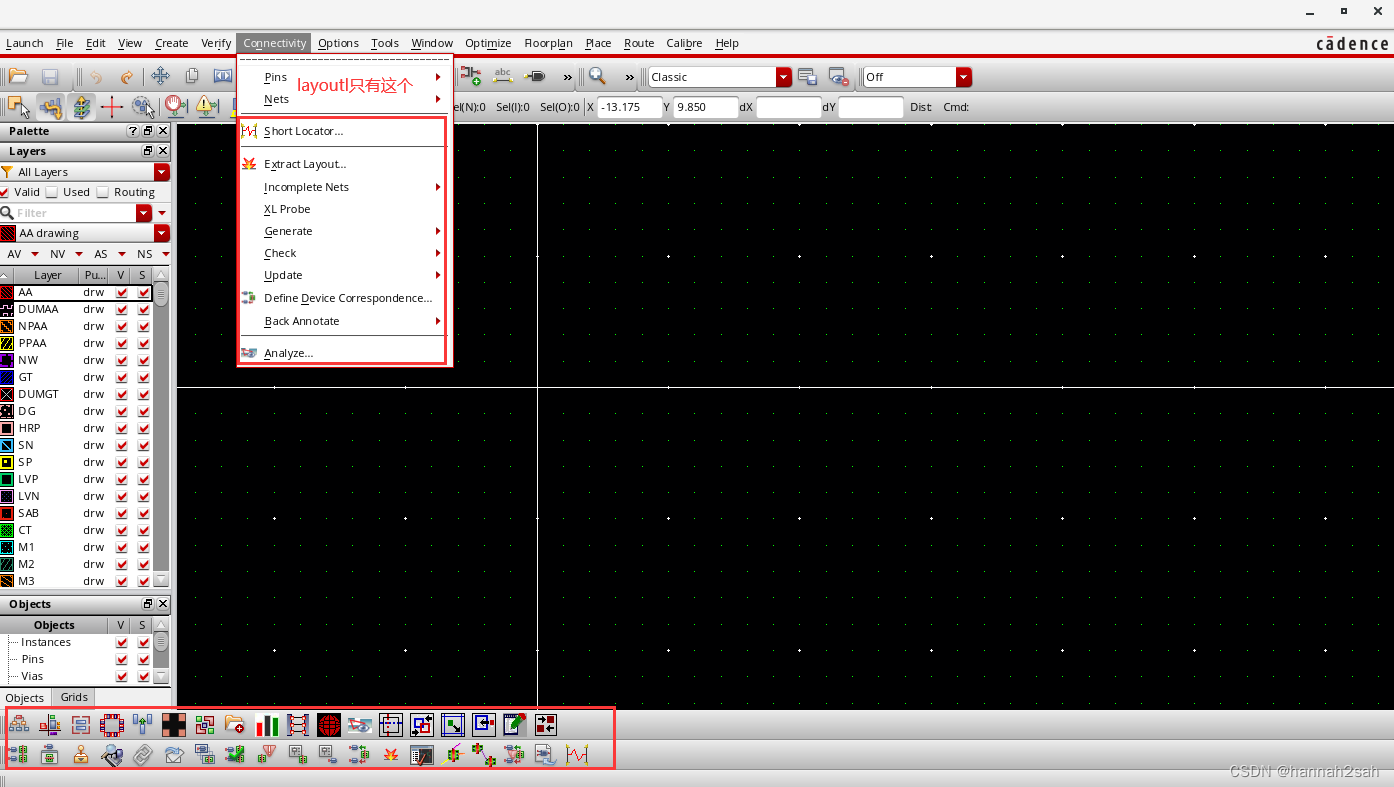

- 目前情况主要是Layout XL在Connectivity以及下方的位置比Layout L多了一些功能

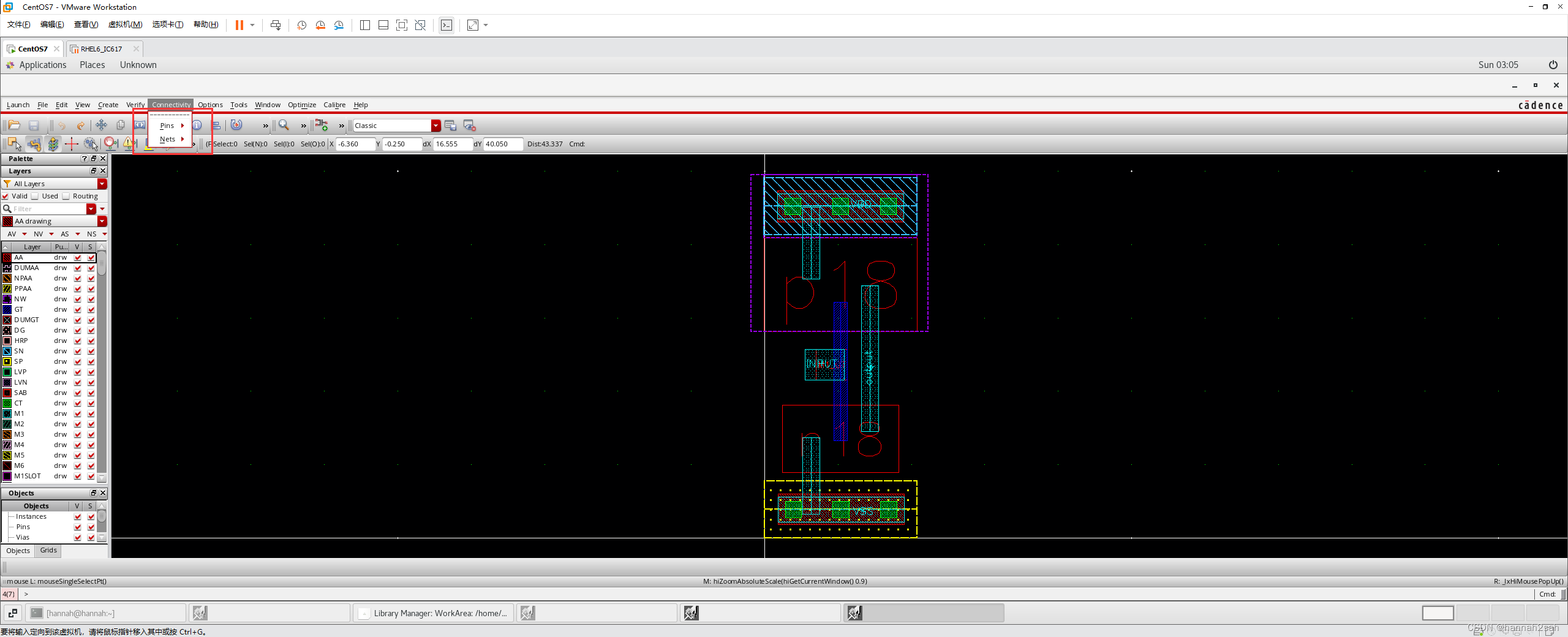

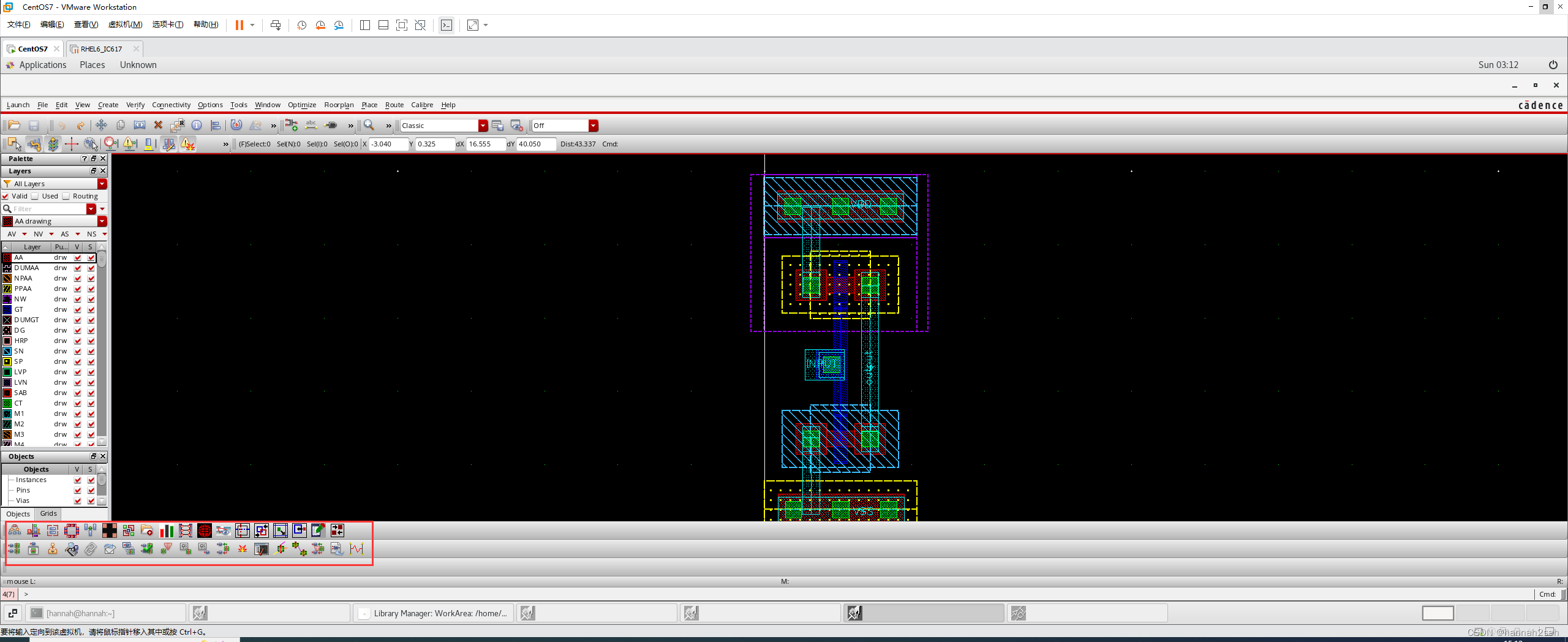

- Layout L

- Layout XL

- Layout L

Layout XL使用

一、 启动Layout XL

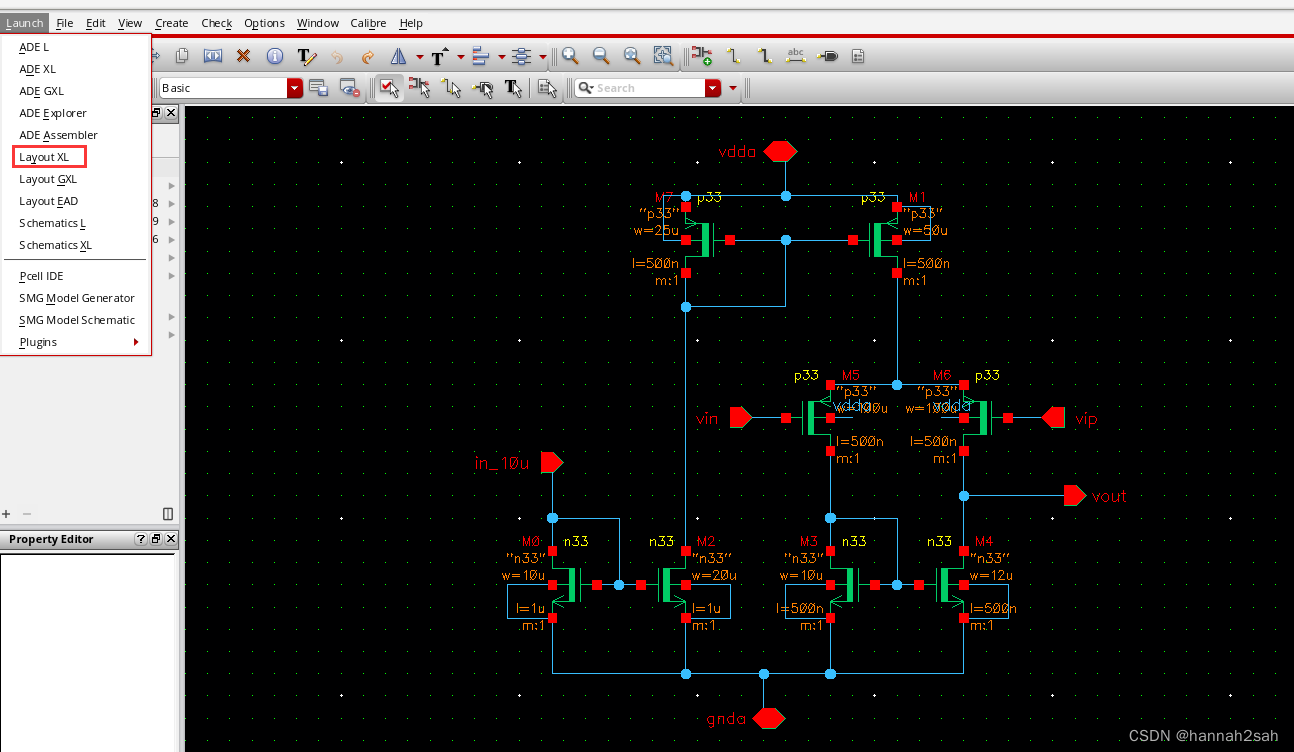

-

1.在原理图界面直接生成Layout XL

-

2.在【file】-【new】-【cell viwe】生成选择layout;【Open with】这里面选择Layout XL,这样版图就直接是layoutXL

-

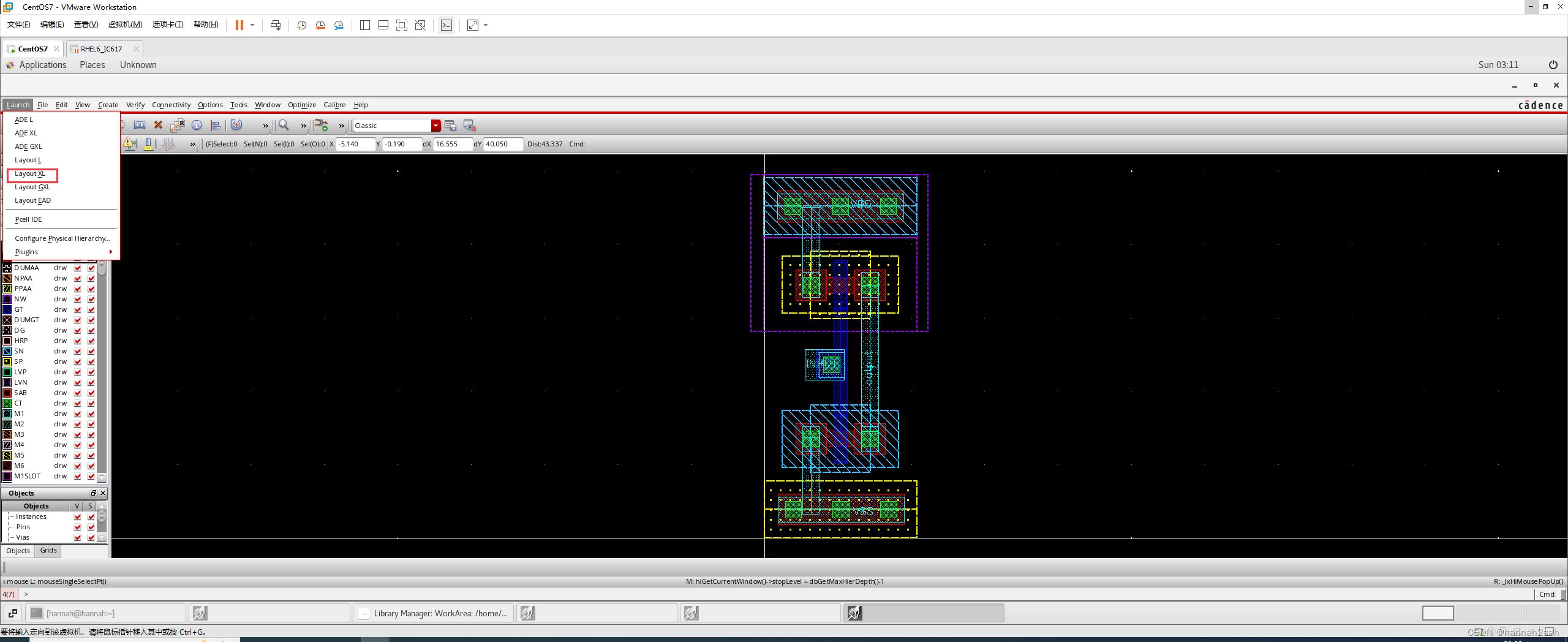

3.在版图界面直接选择【launch】-【Layout XL】,界面就会出现变化

-

所以其实这两个工具可以互相转换,选择当前最适合的工具

二、 生成PIN和cell

-

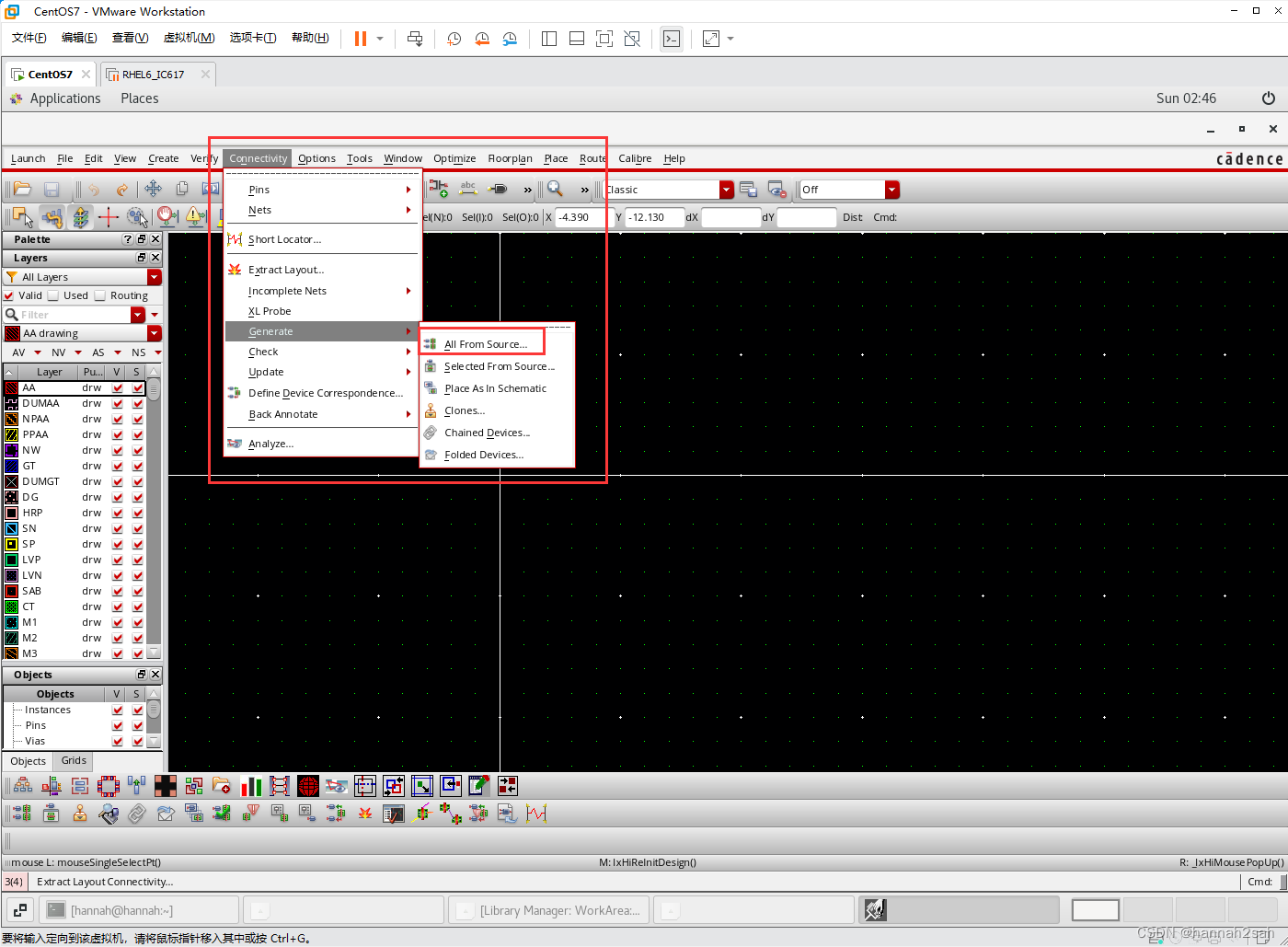

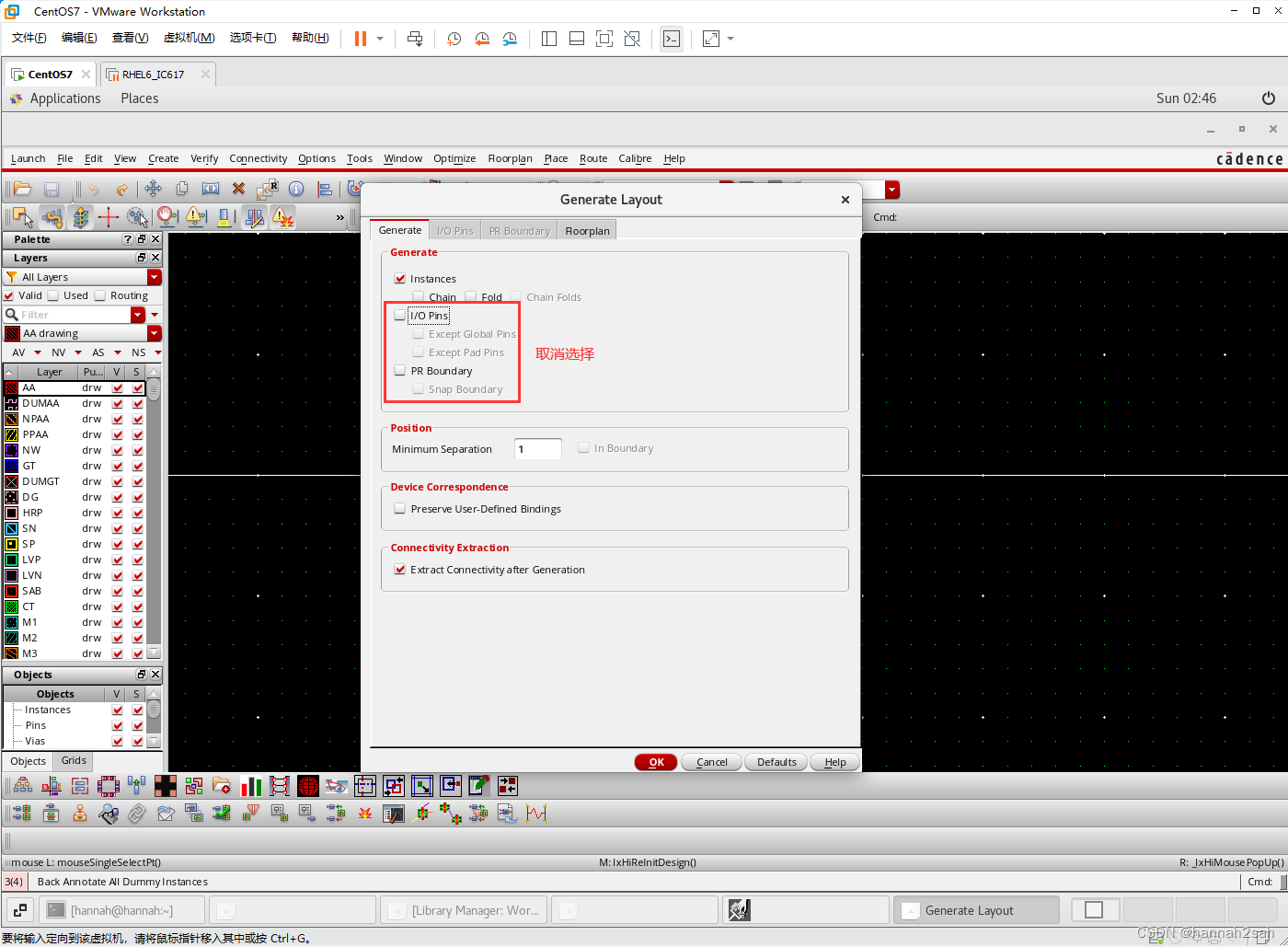

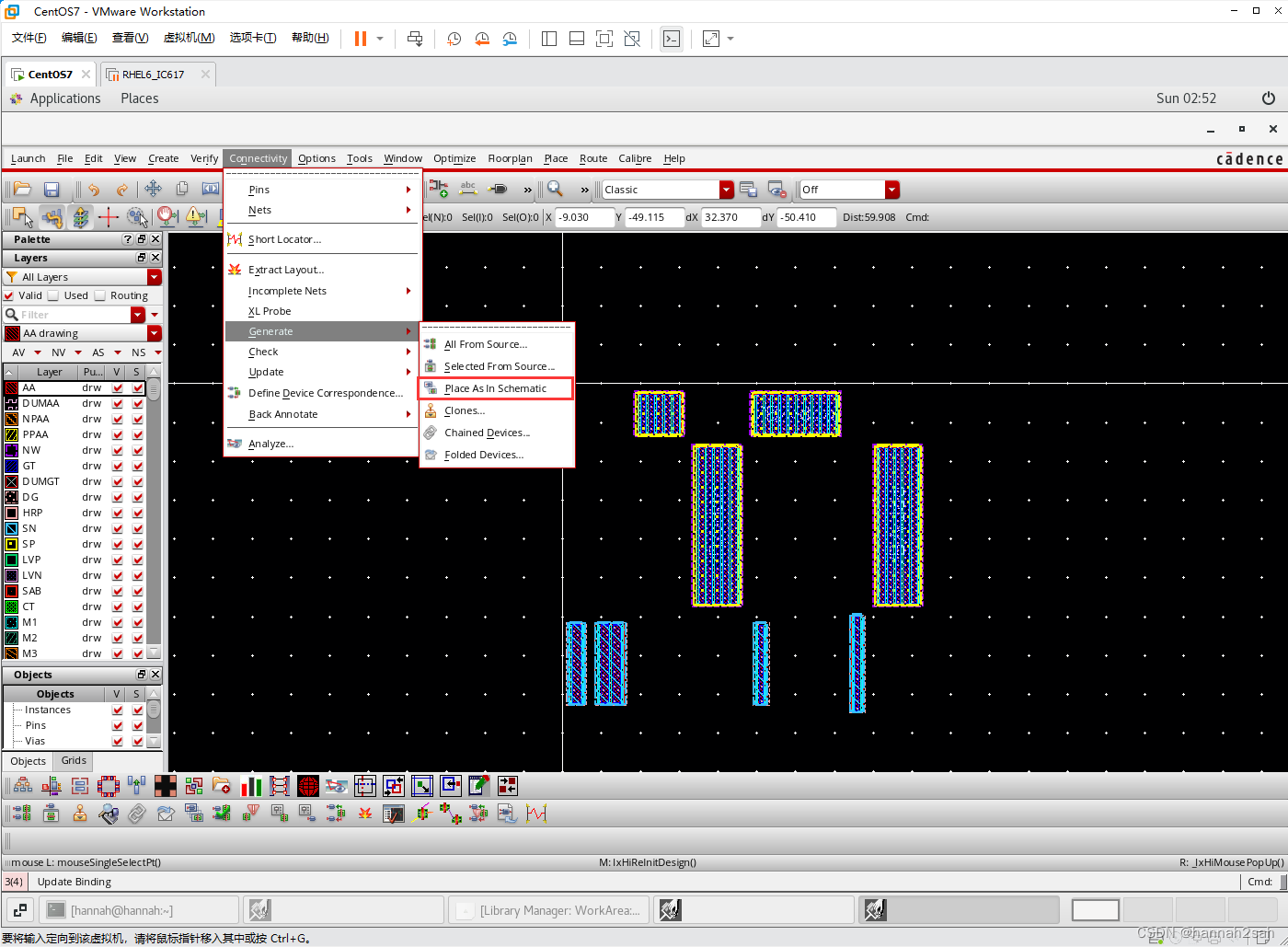

1.全部生成

-

在版图界面选择 Connectivity-> Gen From Source->All From Source;后续只选择器件就好,IO和PR Boundary取消选择

-

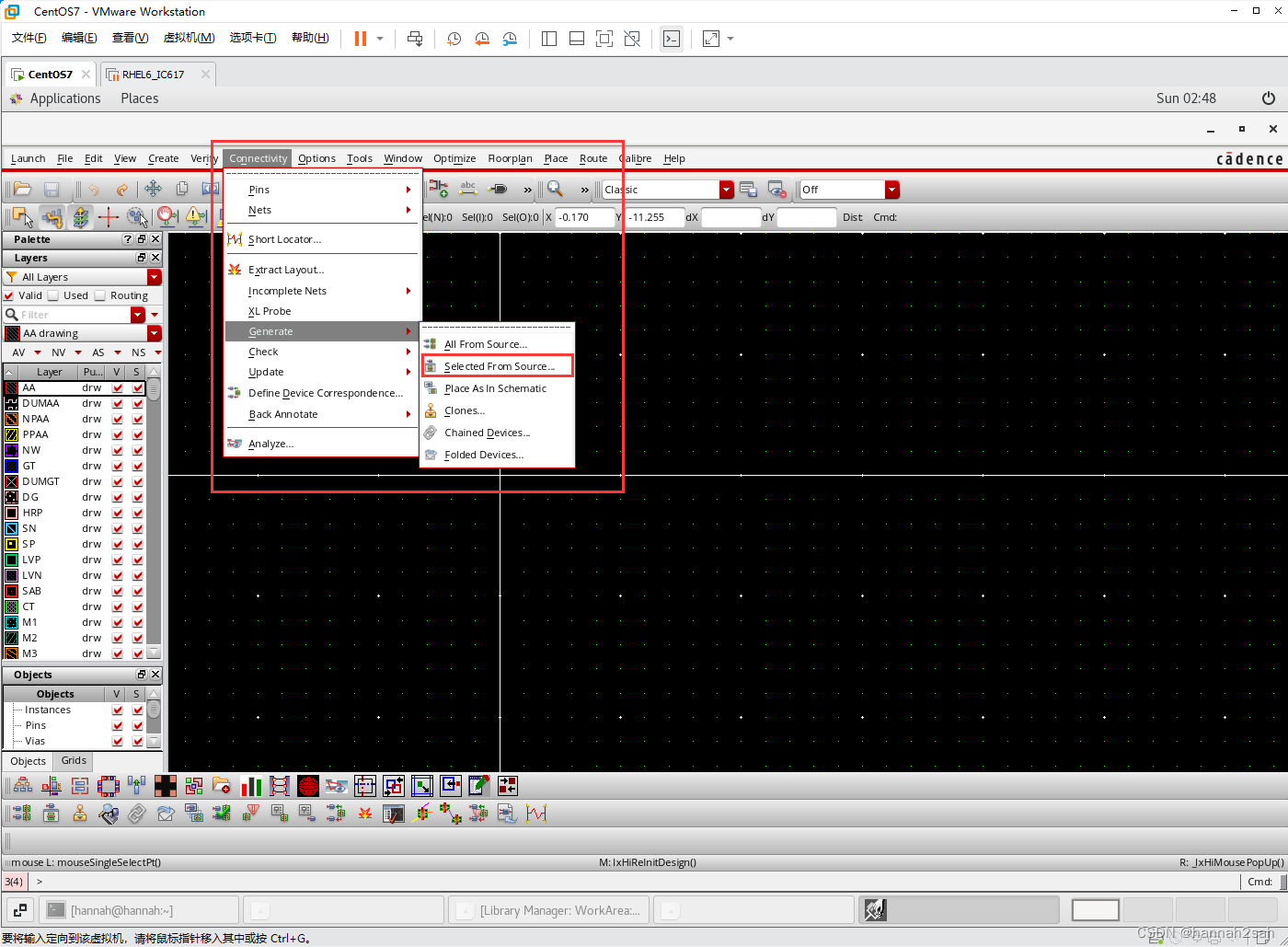

2.部分生成

-

在版图界面 Connectivity-> Gen From Source->Select From Source;在原理图上面选择对应的器件后移动到版图即可

三、 布局

- 在版图界面选择 Connectivity-> Gen From Source->Place As IN Schematic;版图就会出现变化

四、 飞线(使用LayoutXL提高效率)

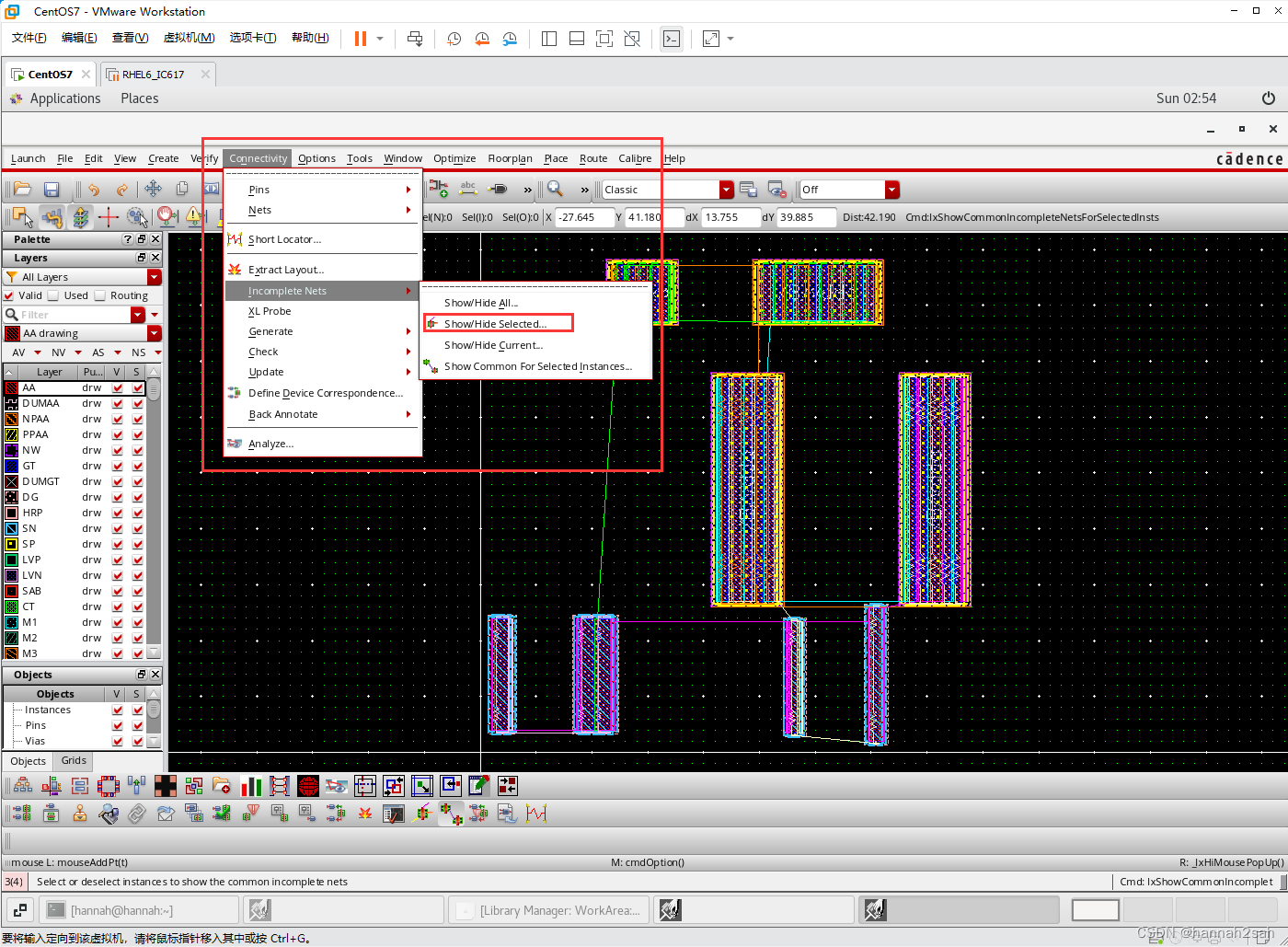

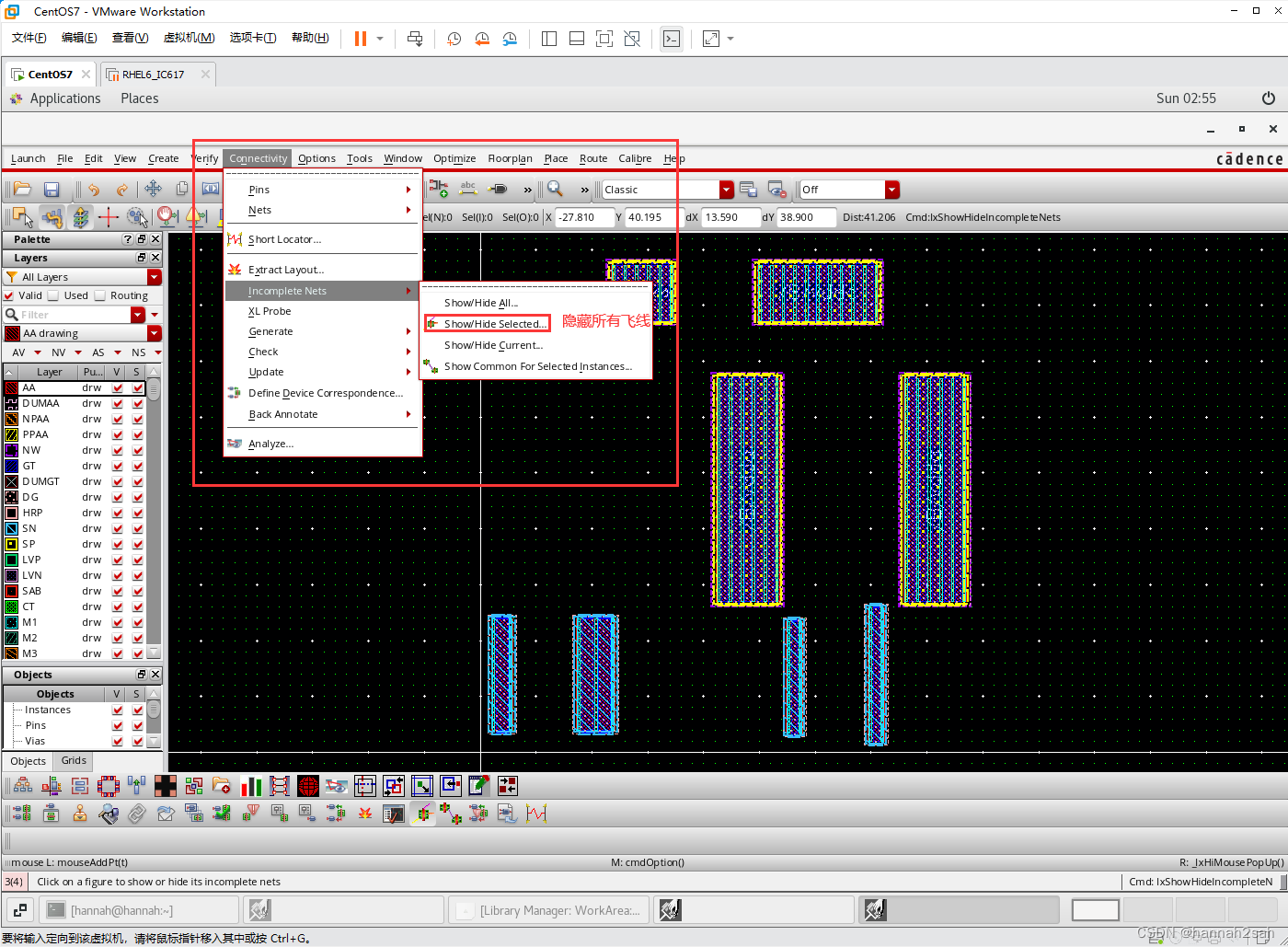

- 1.显示飞线:Connectivity-> Incomplete Nets->Show Incomplete Nets

- 2.隐藏所有飞线:Connectivity-> Incomplete Nets->Hide Incomplete Nets

- 建议选择性显示部分飞线进行连线操作,全部显示时由于颜色种类有限和飞线太多反而让人识别不清。

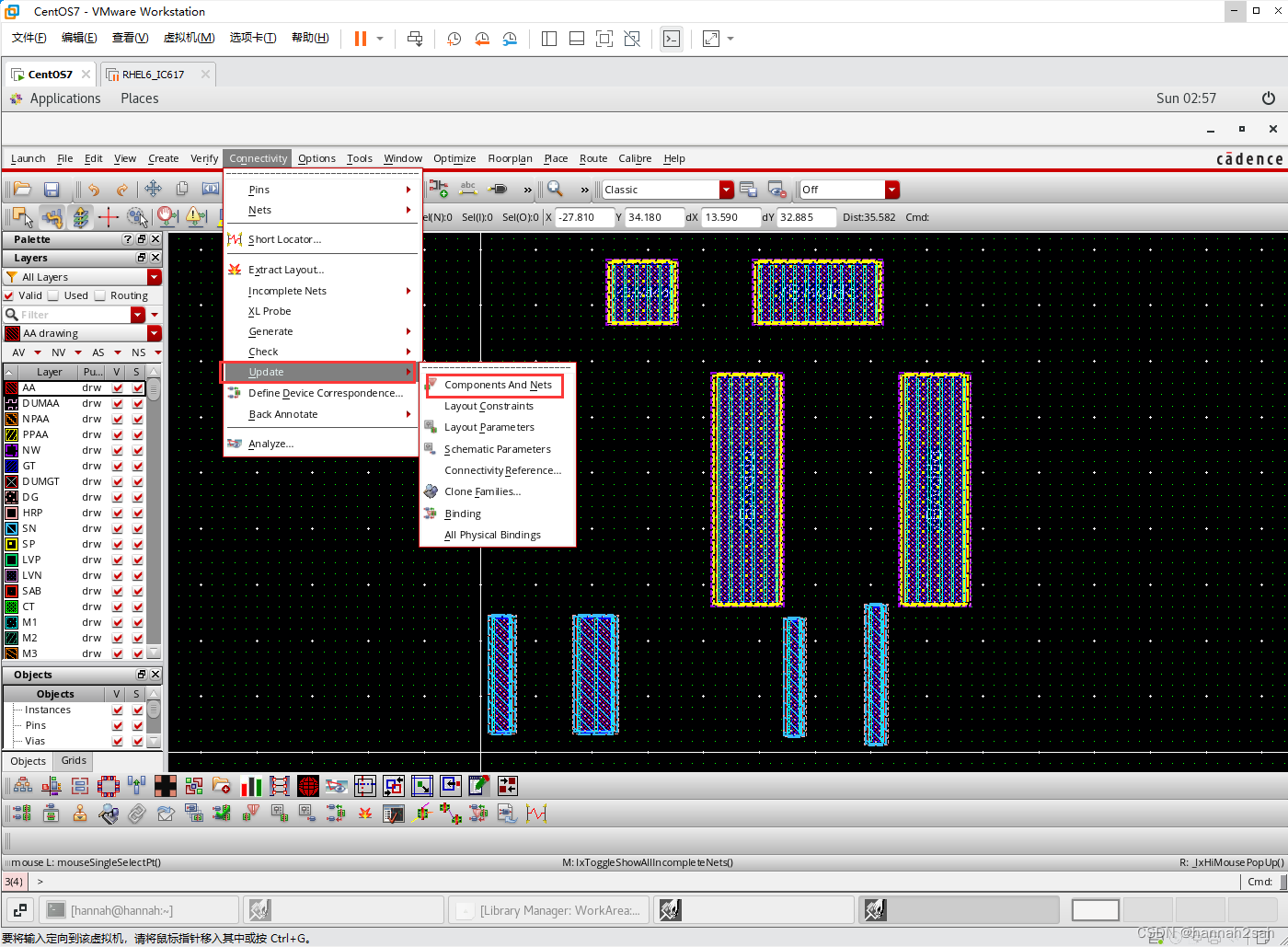

五、 改动

- 如果schematic有改动则可以依次点击Connectivity-> Update-> Components And Nets打开 Layout Generation Options, 会列出layout中没有但schematic中有的pin, 点击Ok后则会在layout窗口中产生schematic中新加的cell和pin, schematic中已删除的则在layout中会打叉。

Layout XL优缺点

- 优点:

- 第一可以方便的将电路中的所有instance准确无误的导入的Layout中,当然这也是建立在前期充分准备的基础上的;

- 第二点就是导入的layout cell是和schematic对应的,你在schematic中点cell, layout中就会自动点亮与之对应的cell, 反之也是;

- 第三点就是它会显示对应的连接关系,不用看电路也能准确的把所有net连接起来。

- 缺点:

- 第一,由于导入至layout中的instance都有了与电路对应的唯一的instance name所以布局上就有点费时。 比如电路中的 i1和i2都是用的同一个cell, 那么不用layoutXL时, 两个cell随便放都行,但用了layoutXL, 两个cell就必须与i1和i2对应。

- 第二,layoutXL的飞线是靠pin的名字连接的,一但导入的时候把所有的pin也导进来了,那么就需要把这些pin移动到对应的net上,而不是随手打个label就可以的,因为这样不会显示飞线的,所以手慢的人又会多用一些时间。

总结

- 通过上面我们可以了解到目前Layout XL中有许多比较好用的功能,如果是需要使用到这些功能的时候,当然是Layout XL更好一些

- 目前通过我的了解,我感觉Layout XL确实有些功能还挺好用的

1906

1906

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?