实现功能:在开发板的数码管上显示特定数字,并且让这些数字循环移位。

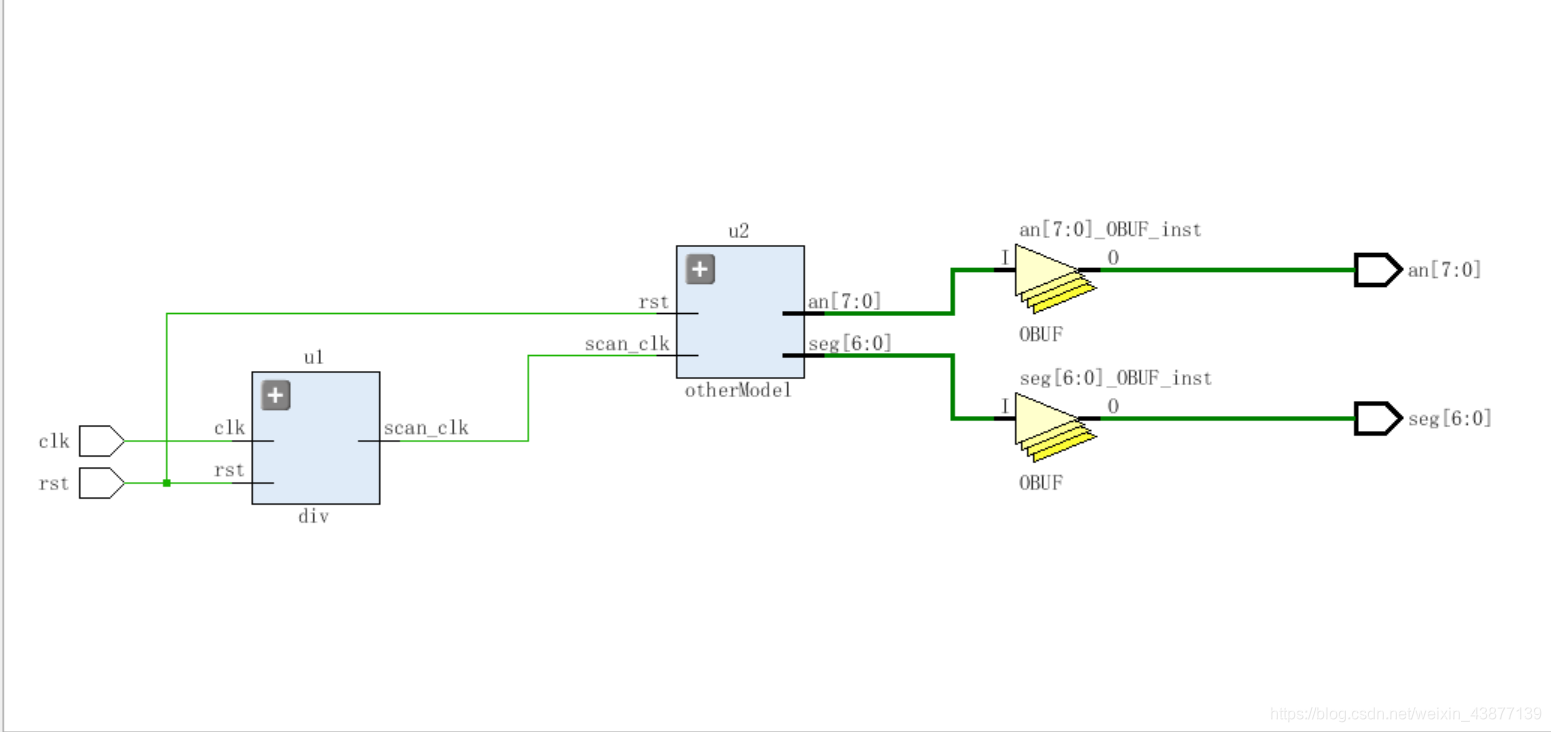

总体框图如下:

代码如下:

分频模块:

module div(

input clk, //输入自带的系统时钟(100Mhz)

input rst, //复位

output scan_clk //输出时钟,用于驱动数码管,让其动态扫描用

);

reg [19:0] clkdiv;

always @(posedge clk or posedge rst)

begin

if( rst == 1) clkdiv <=0;

else clkdiv <= clkdiv + 1;

end

assign scan_clk = clkdiv[15]; //使得san_clk = 190Hz

endmodule

其他模块(显示模块):

module otherModel(

input rst,

input scan_clk,

output reg [7:0] an,

output reg [6:0] seg

);

reg [3:0] digit; //选择位上显示的数字

reg [2:0] cnt; //选择哪一位显示

always @(posedge scan_clk or posedge rst)

begin

if ( rst == 1) cnt <=0;

else cnt <=cnt + 1;

end

always @ (*)

begin

case ( cnt )

3'b000:begin digit = 4'b0000; an = 8'b01111111; end

3'b001:begin digit = 4'b0001; an = 8'b10111111; end

3'b010:begin digit = 4'b0010; an = 8'b11011111; end

3'b011:begin digit = 4'b0011; an = 8'b11101111; end

3'b100:begin digit = 4'b0100; an = 8'b11110111; end

3'b101:begin digit = 4'b0101; an = 8'b11111011; end

3'b110:begin digit = 4'b0110; an = 8'b11111101; end

3'b111:begin digit = 4'b0111; an = 8'b11111110; end

default:begin digit= 4'b0000; an = 8'b01111111; end

endcase

end

always @ (*)

begin

case ( digit )

4'b0000:seg = 7'b0100100;

4'b0001:seg = 7'b1000000;

4'b0010:seg = 7'b1111001;

4'b0011:seg= 7'b0000000;

4'b0100:seg =7'b0100100;

4'b0101:seg =7'b1000000;

4'b0110:seg =7'b1111000;

4'b0111:seg =7'b0000000;

default: seg = 7'b0000001;

endcase

end

endmodule

顶层模块:

module top(

input clk,

input rst,

output [7:0] an,

output [6:0] seg

);

div u1(clk,rst,scan_clk); //例化模块

otherModel u2(rst,scan_clk,an,seg);

endmodule

测试文件:

注意:测试文件是针对otherModel文件的。在写测试文件之前,最好不要添加顶层模块,否则测试时会找不到想要测试的那个文件。如果,已经编写完了顶层模块,可以在design列表中,右键要测试的文件,然后点击 设置为顶层文件,这样就会测试到指定的文件了。

module otherModel_tb();

reg rst,scan_clk; //输入信号要用 reg型

wire [7:0] an; //输出信号要用 wire型

wire [6:0] seg; //输出信号

otherModel test(

.rst(rst),

.scan_clk(scan_clk),

.an(an),

.seg(seg)

);

initial fork

scan_clk = 0;

rst = 1; #50 rst = 0;

join

always #10 scan_clk = ~scan_clk; //定义没过10毫秒,信号就会进行翻转

endmodule

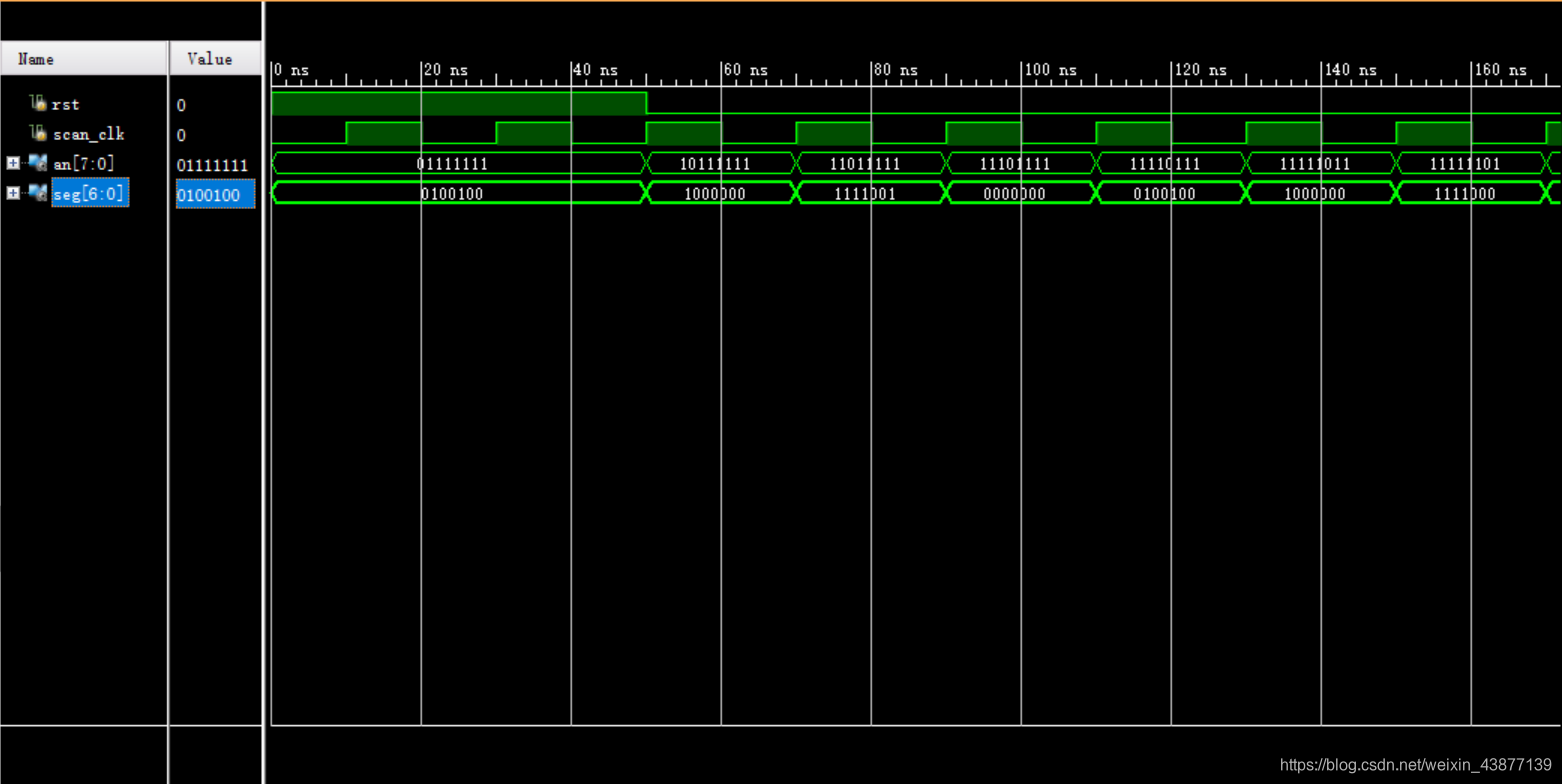

仿真波形如下:

我也写了几篇关于Veirlog的文章,感兴趣的同学可以去看看。该模块链接如下:

https://blog.csdn.net/weixin_43877139/article/category/8778400

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?