在本文中会进行一个简单的FPGA编程演示,这通常可以验证编译工具链是否正常使用。在LabVIEW FPGA中和rt、PC编程一样使用数据流编程,但是需要注意的是FPGA中有些函数是不可以用的,因为这些函数很占用资源,且FPGA只能同时下载运行一个程序。

1.在FPGA终端下面新建一个VI。

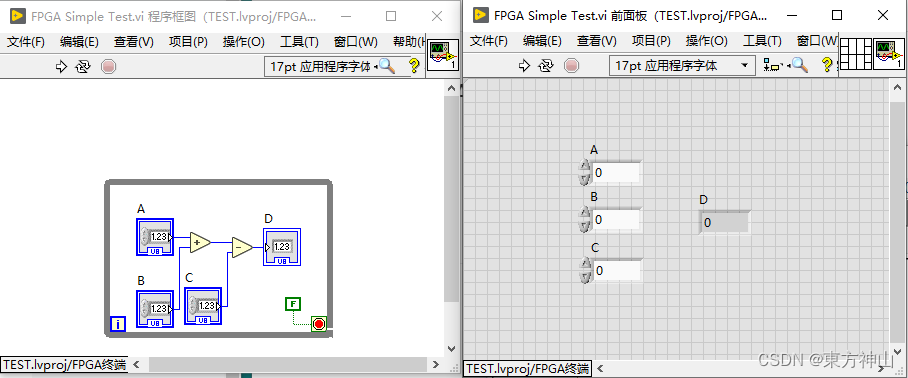

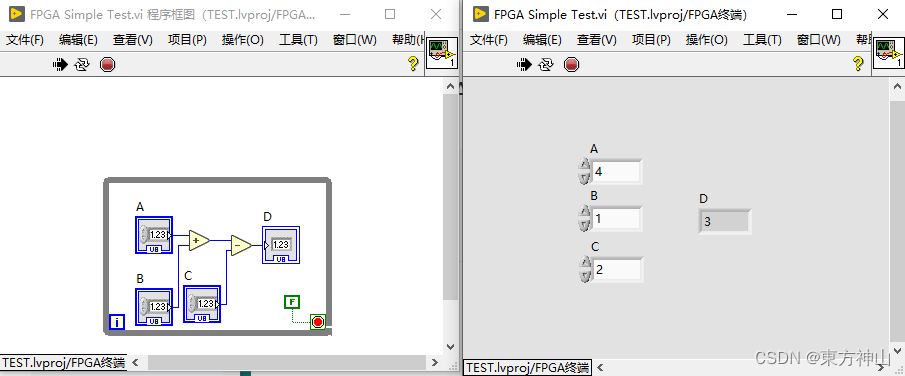

2.打开新创建的VI,随便写一点数学加减法函数用于编译验证编译器功能。

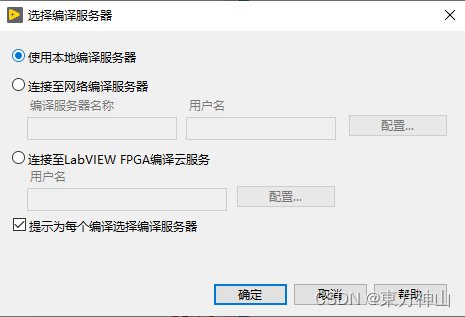

3.点 运行 箭头进行编译,使用本地编译器。

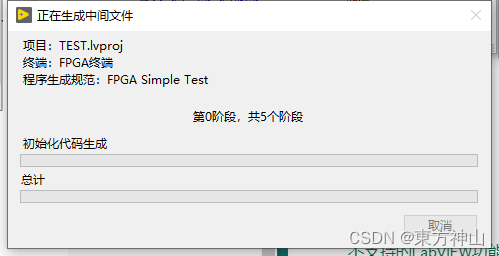

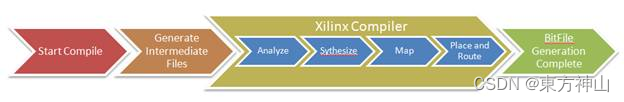

4.等待编译过程。编译过程的第一步是生成中间文件。在此过程中,LabVIEW 会解析您的框图并将代码转换为 Xilinx 编译器可以使用的形式。在此步骤中可能会出现许多错误,导致编译失败。这些错误通常涉及非法VI或放置在单周期定时循环中的VI组合。

完整的编译过程参考此图

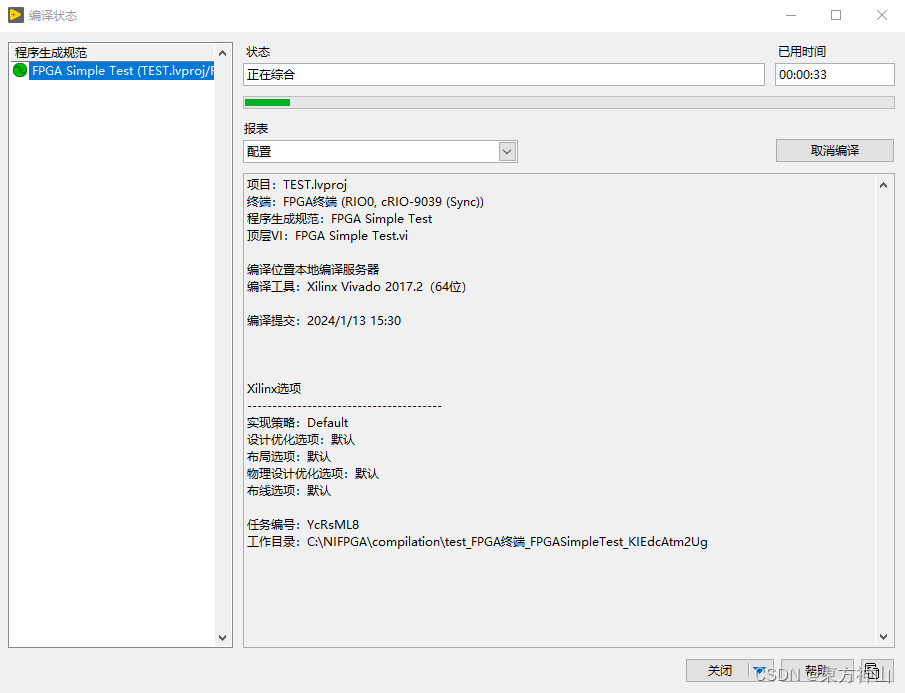

5.编译状态界面。

代码生成完成且没有错误后,将出现“编译状态”窗口。这是指导您完成编译的主窗口。它具有进度条和一些基本时间戳和 VI 信息。随着编译的继续,窗口底部的警报会告诉您新报告何时完成。一般编译时间根据代码的大小变化,初学者编译时间大概在5-10分钟,无论使用什么开发软件,FPGA的编译过程都是较久的。.

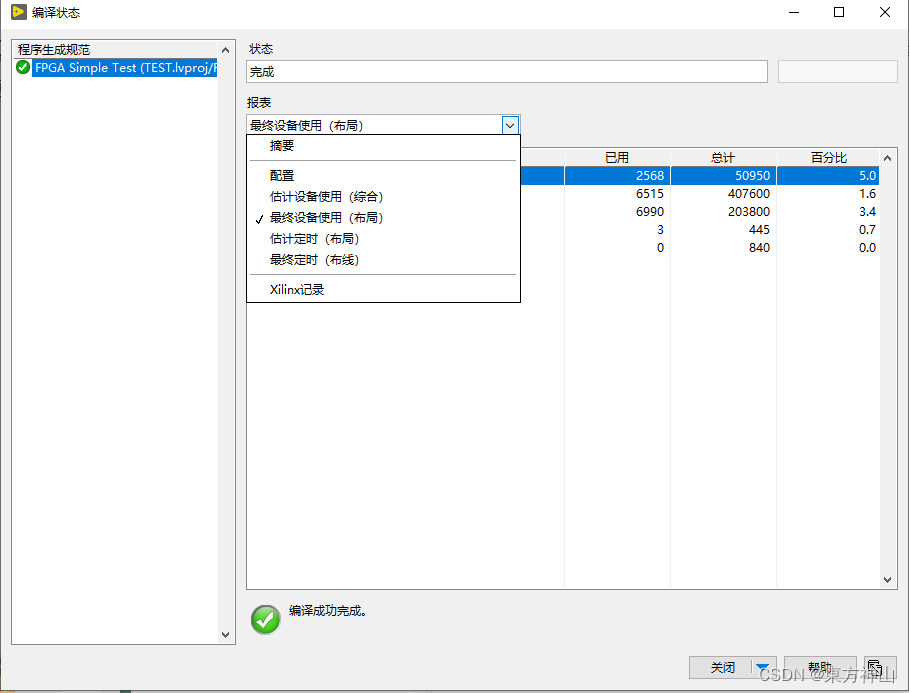

6.编译成功以后,会提示一个编译成功的界面,也可以查看占用的FPGA资源。

7.编译后的FPGA正在运行,可以做一个简单的测试,但是需要注意的是FPGA编程一般是不需要前面板的,同时因为前面板控件占用资源较多,尽量避免在FPGA前面板放太多的控件。

2.

本文详细介绍了如何在LabVIEWFPGA中进行简单的编程演示,包括创建VI、编写加减法函数、编译验证过程、资源占用注意事项以及编译成功后的资源查看。

本文详细介绍了如何在LabVIEWFPGA中进行简单的编程演示,包括创建VI、编写加减法函数、编译验证过程、资源占用注意事项以及编译成功后的资源查看。

2661

2661

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?