文章目录

- Direct Memory Access (DMA) Module

- 介绍

- 结构

- CPU 仲裁

- 通道优先级

- 地址指针和传输控制

- ADC 同步功能

- 超运行检测功能

- API 解析

- void DMAInitialize(void)

- void DMACH1AddrConfig(volatile Uint16 *DMA_Dest,volatile Uint16 *DMA_Source)

- void DMACH1BurstConfig(Uint16 bsize, int16 srcbstep, int16 desbstep)

- void DMACH1TransferConfig(Uint16 tsize, int16 srctstep, int16 deststep)

- void DMACH1WrapConfig(Uint16 srcwsize, int16 srcwstep, Uint16 deswsize, int16 deswstep)

- void DMACH1ModeConfig(Uint16 persel, Uint16 perinte, Uint16 oneshot, Uint16 cont, Uint16 synce, Uint16 syncsel, Uint16 ovrinte, Uint16 datasize, Uint16 chintmode, Uint16 chinte)

- StartDMACH1();

- 部分图

例程解析参考以下链接

DMA例程解析1

Direct Memory Access (DMA) Module

直接存储器访问(DMA)模块提供了一种在外设和/或存储器之间传输数据的硬件方法,而不需要来自CPU的干预,从而为其他系统功能释放带宽。此外,DMA有能力在数据传输时正交地重新排列数据,以及在缓冲区之间的“乒乓”数据。这些特性对于将数据构造成块以实现最佳的CPU处理非常有用.

介绍

数字信号控制器(DSC)的强大之处并不仅仅体现在处理器速度上,而是在于整体系统功能。作为等式的一部分,任何给定功能所需的CPU带宽减少,系统的功能就越强大。很多时候,应用程序会花费大量的带宽来移动数据,无论是从片外存储器到片上存储器,还是从模拟-数字转换器(ADC)到RAM这样的外设,甚至是从一个外设到另一个外设。此外,很多时候这些数据格式并不利于CPU的最佳处理能力。本参考指南中描述的DMA模块能够释放CPU带宽,并将数据重新排列成更流畅处理的模式。

DMA模块是事件驱动型,这意味着它需要一个外设中断触发器来启动DMA传输。虽然可以通过配置定时器作为中断触发源使其成为周期性时间驱动的机器,但模块本身内没有机制可以定期启动存储器传输。六个DMA通道的中断触发源可以单独配置,每个通道都包含自己的独立PIE中断,以便让CPU知道DMA传输何时开始或完成。六个通道中有五个是完全相同的,而通道1有一个额外的功能:可以配置为比其他通道更高的优先级。DMA的核心是一个状态机以及紧密耦合的地址控制逻辑。正是这个地址控制逻辑允许在传输过程中重新排列数据块,以及在缓冲区之间进行数据乒乓操作。本文档将详细讨论这些功能以及其他功能。

DMA 概述:

- 6个通道,带有独立的PIE中断

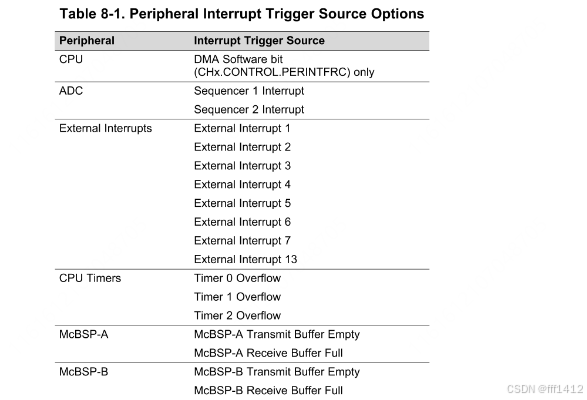

- 外设中断触发源

- ADC序列器1和序列器2

- 多通道缓冲串行端口A和B(McBSP-A, McBSP-B)的发送和接收

- XINT1-7和XINT13

- CPU定时器

- 软件

- ePWM1-6的ADCSOCA和ADSOCB信号

- 数据源/目的地:

- L4-L7 16K x 16 SARAM

- 所有XINTF区域

- ADC内存总线映射的结果寄存器

- McBSP-A和B的发送和接收缓冲区

- ePWM1-6 / HRPWM1-6外设框架3映射的寄存器

- 字大小: 16位或32位(McBSP限制为16位)

- 吞吐量: 每字4周期(McBSP读取为每字5周期)

结构

框图

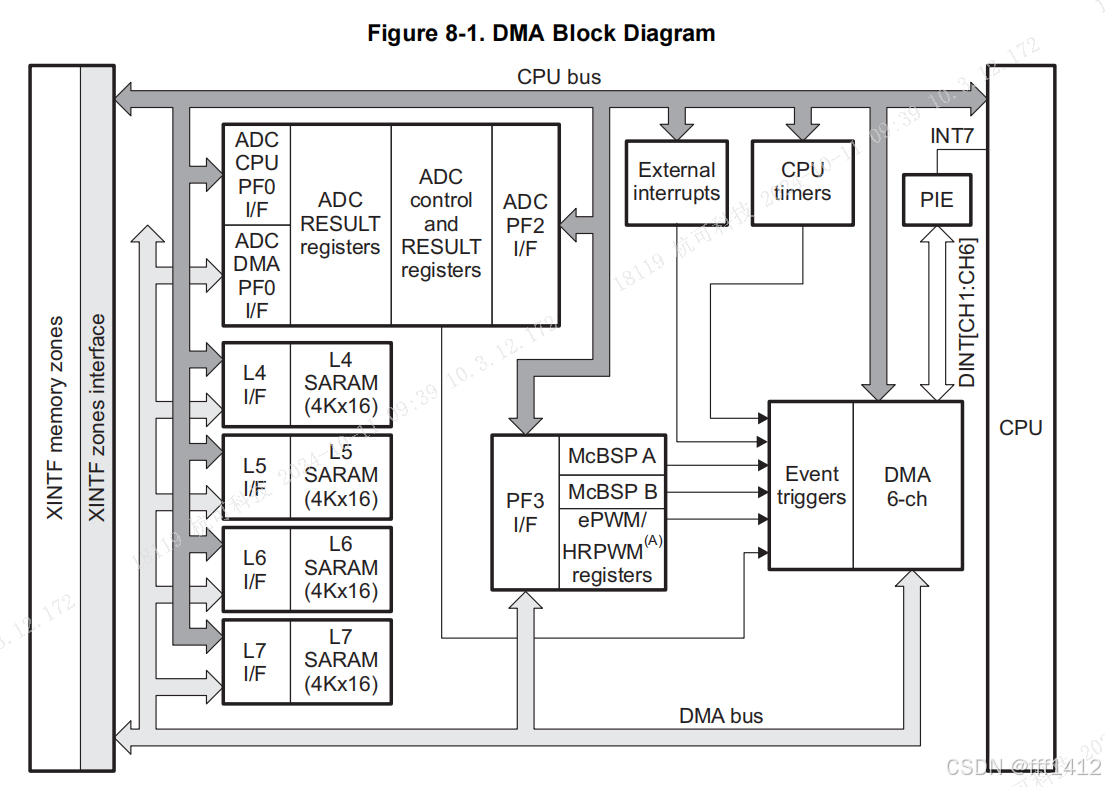

下图显示了DMA的设备级方框图。

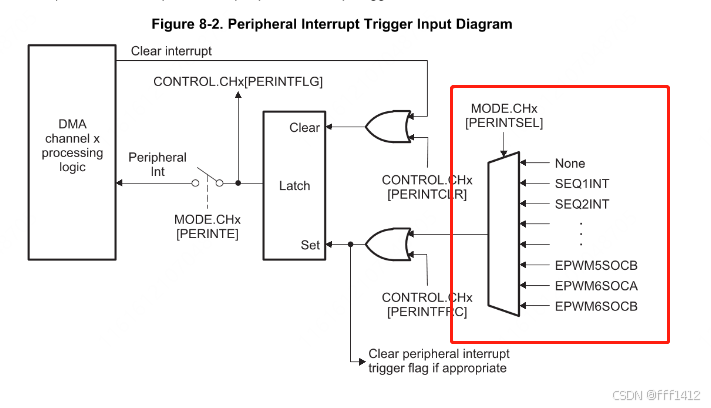

外设中断事件触发器源

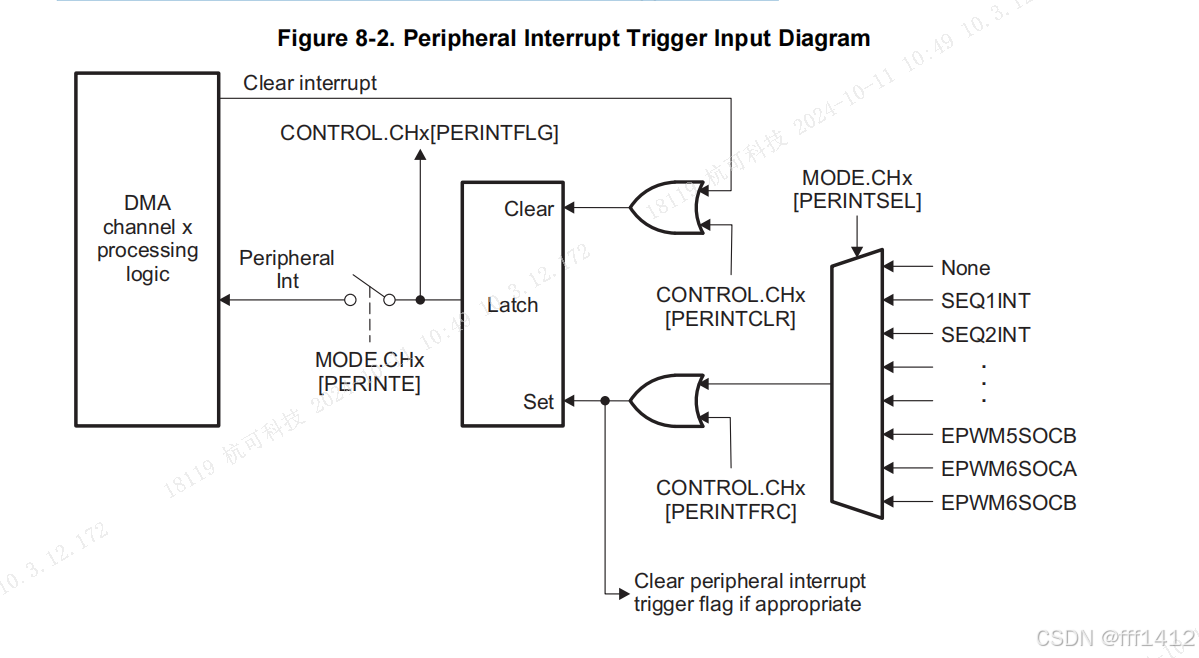

外设中断事件触发器可以为六个DMA通道中的每一个独立配置为十八种不同源之一。这些源包括8个外部中断信号,可以连接到设备上的大多数通用输入/输出(GPIO)引脚。这为事件触发功能增加了显著的灵活性。每个通道的MODE寄存器中有一个名为PERINTSEL的位字段,用于选择该通道的中断触发源。活动的外设中断触发器将被锁定到CONTROL寄存器的PERINTFLG位,如果相应的中断和DMA通道被使能(参见MODE.CHx[PERINTE]和CONTROL.CHx[RUNSTS]位),它将由DMA通道服务。在接收到外设中断事件信号后,DMA将自动向中断源发送一个清除信号,以便后续的中断事件会发生。

无论MODE.CHx[PERINTSEL]位字段的值如何,软件总是可以通过使用CONTROL.CHx[PERINTFRC]位来强制触发。同样,软件总是可以使用CONTROL.CHx[PERINTCLR]位来清除挂起的DMA触发器。

一旦特定的中断触发器设置了一个通道的PERINTFLG位,该位将保持挂起状态,直到状态机的优先级逻辑开始该通道的突发传输。一旦突发传输开始,标志就会被清除。如果在突发传输过程中生成了新的中断触发器,突发传输将在响应新的中断触发器之前完成(在适当的优先级排序之后)。如果在挂起的中断被服务之前发生了第三个中断触发器,CONTROL.CHx[OVRFLG]位将设置一个错误标志。如果在外部中断触发器发生的同时锁定位正在被清除,外设中断触发器具有优先级,PERINTFLG将保持设置状态。

显示了触发选择电路的示意图。有关外设中断触发源的完整列表,请参见MODE.CHx[PERINTSEL]位字段的描述。

显示了触发选择电路的图示。请参见MODE.CHx[PERINTSEL]位字段的描述,以获取完整的外设中断触发源列表。

DMA bus

DMA总线架构由22位地址总线、32位数据读取总线和32位数据写总线组成。连接到DMA总线的存储器和寄存器位置是通过有时与CPU内存或外围总线共享资源的接口。仲裁规则的定义见第8.4节。以下资源已连接到DMA总线:

- XINTF Zones 0, 6, and 7

- L0-L7 SARAM

- L4 SARAM

- L5 SARAM

- L6 SARAM

- L7 SARAM

- ADC Memory Mapped Result Registers

- McBSP-A and McBSP-B Data Receive Registers (DRR2/DRR1) and Data Transmit Registers

(DXR2/DXR1) - ePWM1-6/HRPWM1-6 Register when mapped to Peripheral Frame 3

管道定时和吞吐量

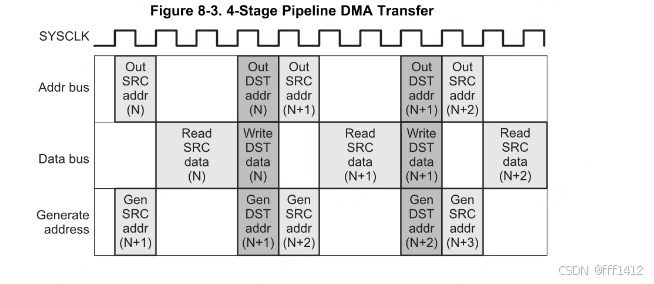

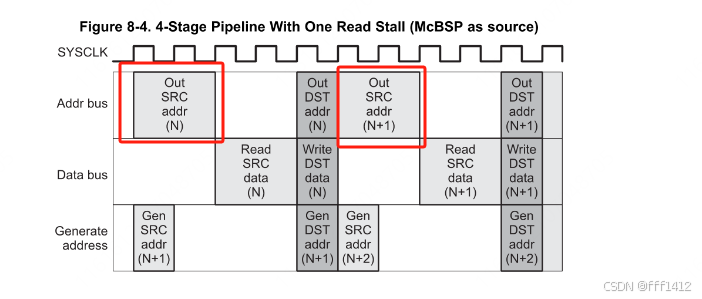

DMA由图8-3所示的四个阶段管道组成。唯一例外是当DMA通道配置为使用其中一个McBSP作为其数据源时。读取一个McBSP DRR寄存器会将DMA总线在读取部分传输期间阻塞一个周期,如图8-4所示。

除了管道之外,DMA的其他一些行为也会影响其总吞吐量:

-

在每个突发的开始处添加一个周期延迟

-

返回CH1高优先级中断时添加一个周期延迟

-

32位传输的速度是16位传输速度的两倍(即,传送一个32位字的时间与传送一个16位字的时间相同)

-

与CPU的碰撞可能会添加延时槽(见第8章)

例如,要将128个16位字从ADC传输到RAM,可以配置一个通道来传输每批16个字的8次bursts。这将得到:

8次bursts*[(每个字4周期/字*每次bursts16个字)+ 1] = 520周期。

如果相反地,该通道被配置为一次传输相同数量的数据32位(每个字的大小是配置为32位),传输需要:

8次bursts*[(每个字4周期/字*每次bursts8个字)+ 1] = 264周期。

CPU 仲裁

通常,DMA活动与CPU活动无关。在DMA和CPU同时尝试访问同一接口中的内存或外围寄存器的情况下,仲裁程序将发生。唯一的例外是映射到内存的ADC寄存器(PF0),即使同时由CPU和DMA读取,也不会产生冲突,即使不同的地址被访问。任何不同接口之间的联合访问,或者当CPU访问不在DMA正在访问的接口之外时都不会产生冲突。

内部包含冲突的接口有:

- XINTF内存区0、6和7

- L4 RAM

- L5 RAM

- L6 RAM

- L7 RAM

- 外设帧3(McBSP-A,McBSP-B)

对于外部存储接口(XINTF)区域

-

如果CPU和DMA在同一周期尝试访问XINTF区中的任何一个,那么DMA将首先被服务,然后是所有待处理的CPU访问(按CPU访问的正确优先级顺序:写入→读取→获取)。

-

如果CPU对一个XINTF区有未完成或正在由XINTF处理的访问,并且试图进行DMA访问,则DMA访问会被暂停,直到所有CPU未完成访问完成。例如,如果有一个CPU写入和读取访问正在进行中并且有一个获取正在进行中,则首先完成获取操作,然后执行CPU写入操作,然后执行CPU读取操作,最后执行DMA访问。

-

如果CPU和DMA同时尝试进行写访问,则存在1个周期的延迟。

如果DMA或CPU用于写入XINTF区域,则XINTF的写缓冲区可以帮助避免CPU或DMA阻塞。如果CPU或DMA从XINTF进行读取,那么可能会发生显著的阻塞。这里唯一的关注点是如果DMA被阻塞并且DMA错过了其他优先级更高的DMA事件(例如服务ADC),该事件可以以高速率生成数据。在这种情况下,在阻塞时间过长的情况下,可能错过其他DMA事件时,不应使用DMA在XINTF上传输数据。

DMA不支持从XINTF读取的中断机制。如果DMA正在访问其中一个XINTF区域,并且DMA访问被阻塞(XREADY未响应),则CPU可以发出一个HARDRESET,以终止访问。HARDRESET的行为类似于对DMA进行系统复位。同样,需要向XINTF应用HARDRESET,以便释放外围设备从准备就绪状态中解脱出来。任何写入缓冲或在XINTF或DMA上等待的数据都将丢失。

对于其他所有外围设备/内存

-

如果CPU和DMA在同一周期访问相同的接口,DMA具有优先级并且CPU被阻塞。

-

如果一个CPU正在访问一个接口,并且另一个CPU对同一接口的访问处于等待状态,例如,CPU正在进行写操作,而从CPU的读取操作处于等待状态,则当当前CPU访问完成时,对相同接口的DMA访问具有比等待中的CPU访问更高的优先级。

注意:如果CPU正在执行读-修改-写操作,而DMA正在向同一位置进行写入,则在CPU读取和CPU写入之间发生操作时,DMA写入可能会丢失。因此,建议不要将此类CPU访问与DMA访问混合到相同的位置。

在RAM的情况下,可以实现乒乓方案以避免CPU和DMA同时访问同一RAM块,从而避免任何停滞或损坏问题。

通道优先级

当确定通道优先级时,有两种优先级方案:轮询模式和通道1高优先级模式。

轮询模式

在这种模式下,所有通道具有相同的优先级,并且每个启用的通道按以下方式轮询服务:

CH1 → CH2 → CH3 → CH4 → CH5 → CH6 → CH1 → CH2 →…

在上述情况下,每个通道在传输完一个突发后,下一个通道被服务。您可以为每个通道指定突发的大小。一旦CH6(或最后一个启用的通道)被服务,并且没有其他待处理的通道,则轮询状态机进入空闲状态。

从空闲状态开始,如果通道1已启用,则总是首先服务通道1。但是,如果DMA正在当前处理另一个通道x,则在x和本轮结束之间所有等待的通道在CH1之前都被服务。这就是为什么所有通道具有相同的优先级。例如,在轮询模式下,假设CH1、CH4和CH5已启用并且CH4目前正在处理中。然后,在CH4完成之前,CH1和CH5都会从各自的外围设备接收中断触发器。现在,CH1和CH5都处于等待状态。当CH4完成其突发时,将服务CH5。只有在CH5完成后才会服务CH1。当CH1完成时,如果没有更多的通道处于等待状态,轮询状态机将进入空闲状态。

更复杂的例子如下所示:

-

假设所有通道都已启用,DMA处于空闲状态,

-

初始时CH1、CH3和CH5在同一周期上触发,

-

当CH1开始突发传输时,CH3和CH5的请求正在等待,

-

在完成CH1突发之前,DMA接收到来自CH2的请求。现在待处理的请求是来自CH2、CH3和CH5,

-

完成CH1突发后,由于它是轮询方案中的下一个通道,所以将服务CH2。

-

在CH2突发完成后,CH3突发将被服务,然后是CH5突发。

-

现在当CH5突发正在进行时,DMA接收到来自CH1、CH3和CH6的请求。

-

由于它是在CH5之后的轮询方案中的下一个通道,因此CH6突发将在完成CH5突发后开始。

-

这将被CH1突发和CH3突发所跟随。

-

在CH3突发完成后,假设没有发生更多触发,则轮询状态机将进入空闲状态。

通过DMACTRL[PRIORITYRESET],轮询状态机可以重置到空闲状态。

通道1高优先级模式

在这种模式下,如果CH1触发器发生,则在任何其他通道上完成当前字传输或当前+ 1个字传输(取决于新CH1触发器发生在当前DMA传输的哪个阶段)(不是完整的突发),执行停止,并为完整的突发计数服务CH1。当CH1突发完成后,执行返回到CH1触发时处于活动状态的通道。所有其他通道具有相同的优先级,并且每个启用通道以轮询方式依次进行服务:

Higher Priority: CH1

Lower priority: CH2 → CH3 → CH4 → CH5 → CH6 → CH2 →…

给定一个示例,其中CH1、CH4和CH5在通道1高优先级模式下启用,并且当前正在处理CH4。然后,在CH4完成之前,CH1和CH5都从各自的外围设备接收中断触发器。现在,CH1和CH5都是待命状态。当当前的CH4字传输完成后,无论DMA是否完成了整个CH4突发,都会暂停CH4执行并服务CH1。在CH1突发完成后,CH4将恢复执行。

完成CH4后,将服务CH5。在CH5完成后,如果没有任何待处理的通道,则轮询状态机将进入空闲状态。

通常情况下,在这种模式下会使用通道1来为ADC提供数据,因为其数据率很高。当然,通道1高优先级模式可以与任何外围设备一起使用。

NOTE:在通道1上,高优先级模式和ONESHOT模式不能同时使用。当通道1处于高优先级模式时,其他通道可以使用ONESHOT模式。

地址指针和传输控制

DMA状态机,最基础的层面是两个嵌套循环。内层循环在接收到外围中断触发时传输数据burst。burst是最小的数据量,其大小由每个通道的BURST_SIZE寄存器定义。BURST_SIZE寄存器允许在一个突发中最多传输32个十六位字节。外层循环,其大小由每个通道的TRANSFER_SIZE寄存器设置,定义整个传输中执行多少次突发。由于TRANSFER_SIZE是一个16位寄存器,允许传输的最大总大小远远超出任何实际要求。如果启用,则每次传输都会产生一个CPU中断。此中断可以通过模式.CHx[CHINTMODE]位配置,在传输开始或结束时发生。

在MODE.CHx[ONESHOT]位的默认设置中,每当外围中断触发器接收时,DMA会每次传输一个数据突发。在突发完成之后,状态机将移动到优先级方案中的下一个待处理通道,即使刚刚完成的通道还有另一个触发器等待也是如此。此功能可防止任何单个通道垄断DMA总线。如果希望为单个触发器进行超过每个突发的最大字数的传输,则可以将MODE.CHx[ONESHOT]位设置为触发时完成整个传输。使用这种模式时应谨慎操作,因为这可能会导致一个触发器占用大部分DMA带宽的情况。

每个DMA通道包含指向源地址和目标地址的阴影指针。这些指针,SRC_ADDR和DST_ADDR,在状态机操作期间可以独立控制。每次传输开始时,每个指针的阴影版本会复制到其各自的活动寄存器中。在突发循环过程中,每字节传输后,将Burst_STEP寄存器中的适当源或目标值添加到活动SRC/DST_ADDR寄存器中。在传输循环过程中,每完成一次突发后,有两种方法可以修改活动地址指针。第一种,也是默认的方法是通过将SRC/DST_TRANSFER_STEP寄存器中的有符号值添加到适当的指针来实现。第二种是在称为“包装”的过程中进行的,其中将一个包装地址加载到活动地址指针中。当发生包装过程时,相关的SRC/DST_TRANSFER_STEP寄存器没有效果。

当由适当的SRC/DST_WRAP_SIZE寄存器指定的多个突发完成时,会发生地址包装。每个DMA通道包含两个阴影包装地址指针,即SRC_BEG_ADDR和DST_BEG_ADDR,允许源和目标包装彼此独立。就像SRC_ADDR和DST_ADDR寄存器一样,在传输开始时,活动SRC/DST_BEG_ADDR寄存器从其阴影对应物加载。当指定数量的突发发生后,将进行两部分包装程序:

• 适当活动的SRC/DST_BEG_ADDR寄存器通过SRC/DST_WRAP_STEP寄存器中包含的有符号值增加,

• 新的活动SRC/DST_BEG_ADDR寄存器被加载到活动SRC/DST_ADDR寄存器中。

此外,还重新加载了包裹计数器(SRC/DST_WRAP_COUNT)寄存器以设置下一个包裹周期。这允许通道在单个传输中多次包裹。结合上面的第一条,这使通道能够在单次传输中访问多个缓冲区。

DMA包含以下地址指针的活动和阴影集。当DMA传输开始时,将阴影寄存器集复制到活动工作寄存器集。这样可以编程下一次传输的阴影寄存器值,同时DMA与活动集一起工作。它还可以让您实现Ping-Pong缓冲方案而不会中断DMA通道执行。

源/目标地址指针(SRC/DST_ADDR)—写入影子寄存器的值是被读取或写入数据的第一个位置的起始地址。在传输开始时,阴影寄存器被复制到活动寄存器中。活动寄存器作为当前地址指针执行。

源/目标开始地址指针(SRC/DST_BEG_ADDR)—这是包装指针。写入影子寄存器的值将在传输开始时被加载到活动寄存器中。在包装条件下,活动寄存器在加载到活动SRC/DST_ADDR寄存器之前,将由相应的SRC/DST_WRAP_STEP寄存器中的签名值增加。

源/目标包裹步骤(SRC/DST_WRAP_STEP):—— 当包裹计数器达到零时,此值指定要添加到/从BEG_ADDR指针中减去的单词数量,并且因此设置新的开始地址。

这实现了循环类型的寻址模式,在许多应用程序中非常有用。这个值是一个有符号的补码数字,以便可以按需要增加或减少地址指针。

注意:无论DATASIZE位的状态如何,STEP寄存器中指定的值都是为16位地址。所以,为了增加一个32位地址,应该将这些寄存器中的值设为2。

提供了三种模式来控制状态机在突发循环和传输循环中的行为:

单次模式(ONESHOT)— 如果在中断事件触发时启用单次模式,DMA将连续传输数据直到TRANSFERS_COUNT为零。如果禁用单次模式,则每个突发传输都需要一个中断事件触发,并且这将持续到TRANSFERS_COUNT为零。

注意:当启用单次模式时,DMA将在给定通道上连续传输突发数据,直至TRANSFERS_COUNT值为零。这可能会占用外围设备的带宽并导致CPU长时间停顿。为了避免这种情况,您可以配置CPU定时器或类似功能,并禁用单次模式以避免这种情况发生。

高优先级模式和单次模式不能在同一时间用于通道1。其他通道可以在通道1处于高优先级模式时使用单次模式。

连续模式(CONTINUOUS)——如果禁用连续模式,将在传输结束时清除CONTROL寄存器中的RUNSTS位,从而禁用DMA通道。

在另一个传输开始之前,必须通过设置CONTROL寄存器中的RUN位重新启用该通道。如果启用连续模式,则在传输结束时不会清除RUNSTS位。

通道中断模式(CHINTMODE)——此模式位选择是否在新传输的开始或传输结束时生成来自相应通道的DMA中断。

如果实施ping-pong缓冲方案并使用操作连续模式,则中断会在传输开始后立即产生,即在工作寄存器复制到阴影集之后。如果DMA不以连续模式运行,则通常会在传输完成后在传输结束时产生中断。

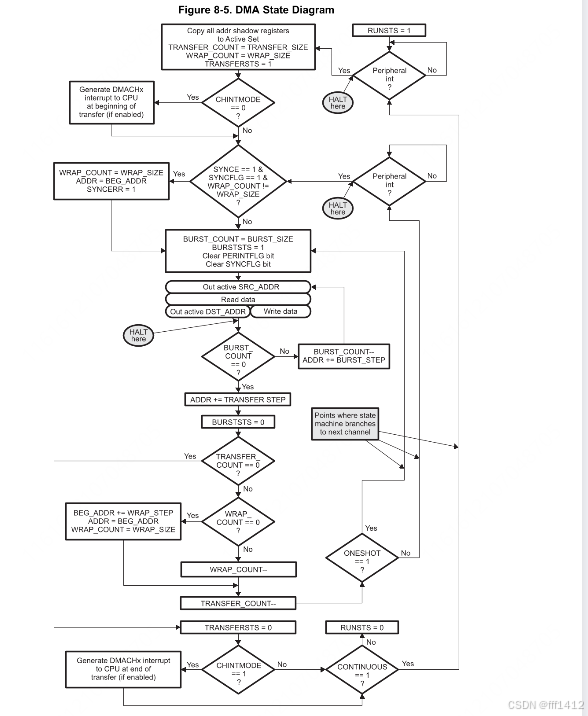

以下项目参考图8-5。

-

HALT点表示在高优先级通道1触发中断或HALT命令设置时,或模拟暂停指令发出且FREE位清零为0时,通道停止操作的位置。

-

在传输开始时,ADDR寄存器不受BEG_ADDR的影响。仅在发生重叠或同步错误时,BEG_ADDR会影响ADDR寄存器。以下是当首次启动传输时每个ADDR寄存器会发生的情况:

- BEG_ADDR_SHADOW保持不变。

- ADDR_SHADOW保持不变。

- BEG_ADDR=BEG_ADDR_SHADOW

- ADDR=ADDR_SHADOW

-

当发生重叠时,活动寄存器会更新。阴影寄存器保持不变。具体来说:

- BEG_ADDR_SHADOW保持不变。

- ADDR_SHADOW保持不变。

- BEG_ADDR+=WRAP_STEP

- ADDR=BEG_ADDR

-

当发生同步错误时,活动寄存器会更新。阴影寄存器保持不变。具体来说:

- BEG_ADDR_SHADOW保持不变。

- ADDR_SHADOW保持不变。

- BEG_ADDR保持不变。

- ADDR=BEG_ADDR

要记住所有这些内容的最简单方法是:

- 阴影寄存器除了由软件更改外不会改变。

- 活动寄存器除硬件更改外不会改变,并且一个阴影寄存器只会被复制到自己的活动寄存器中,而不是另一个名称的活动寄存器。

ADC 同步功能

DMA提供了一种同步到ADC测序器1中断(SEQ1INT)的硬件方法。在这种特定的模式下,ADC将连续转换一个ADC通道序列,而不会在每个序列的末尾重置排序器指针。由于DMA不知道排序器指针在接收到触发器时指向哪个ADC结果寄存器,因此DMA和ADC有可能超出步骤。因此,当ADC在此模式下配置时,每次为从RESULT0寄存器开始的序列产生事件触发器时,它都向DMA提供同步信号。DMA期望这个信号与一个包装程序或一个传输的开始相一致。如果没有,则会发生一个重新同步的过程:

- 用WRAP_SIZE

- 重新加载WRAP_COUNT寄存器。用BEG_ADDR.active

- 加载ADDR.活动寄存器。

在控制寄存器中设置同步器位。这允许使用多个缓冲区来存储数据,并让DMA和ADC在必要时重新同步。例如,假设四个ADC通道被配置为在排序器1上一次转换。由于测序器1的最大长度是8个元素,测序器将重置自身,并每隔其他序列产生一个同步信号。假设软件期望前四个结果将被DMA放入缓冲区A中,第二个结果将放入缓冲区b中。如果DMA活动负担过重,事件触发器丢失,DMA和ADC将变得不同步。此时,DMA将在控制寄存器中设置同步器位,并执行上面的重新同步过程,使DMA和ADC恢复同步。或者,同步特性可以将其配置为通过MODE寄存器中的同步器位在源地址指针上工作。

或者,同步特性可以将其配置为通过MODE寄存器中的同步器位在源地址指针上工作。

如图8-6所示,同步源由MODE寄存器中的周边位段选择。如果为选定的源和通道启用了SYNC特性,则只有在运行位设置后接收到第一个SYNC后,才能开始对该通道的传输。所有外围中断触发器都被忽略。

超运行检测功能

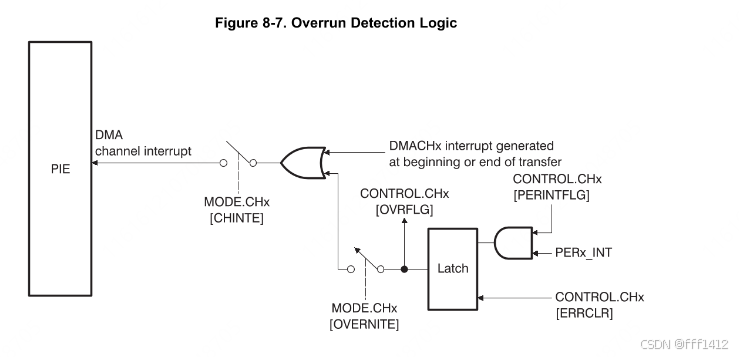

DMA包含溢出检测逻辑。当DMA接收到外围事件触发器时,将设置控制寄存器中的外围tflg位,等待到DMA状态机的通道。当该通道的突发启动时,清除。但是,如果在事件触发器设置插入位并在突发开始时清除之间,另一个事件触发器到达,第二个触发器将丢失。此条件将在控制寄存器中设置OVRFLG位,如图8-7所示。如果启用了溢出中断,则将向PIE模块生成通道中断。

API 解析

void DMAInitialize(void)

DMA初始化 传参个寄存器 硬件复位

void DMACH1AddrConfig(volatile Uint16 *DMA_Dest,volatile Uint16 *DMA_Source)

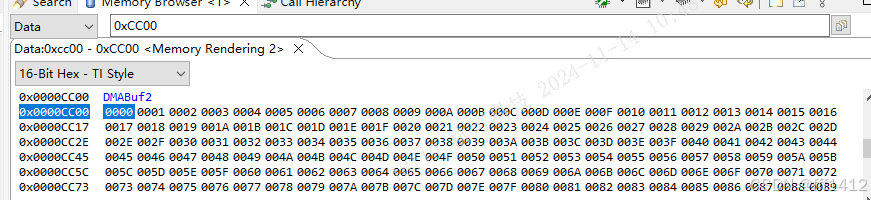

DMA移动的目标地址和源地址

void DMACH1BurstConfig(Uint16 bsize, int16 srcbstep, int16 desbstep)

参数:

bsize:突发传输中传输的单词数量(X-1) 31 代表一次burst传32个字

srcbstep:在处理数据突发时,这些位指定源地址递增/减少后的步长:只有从-4096到4095的值是有效的。

desbstep:在处理数据突发时,这些位指定目标地址递增/减少后的步长:只有从-4096到4095的值是有效的。

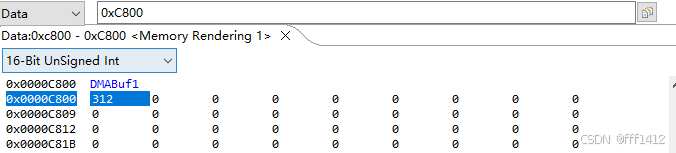

举例 srcbstep = 3 desbstep = 0 bsize = 4

把DMACH1TransferConfig里的参数的偏移都置0

.TransferConfig_tsize = 31,

.TransferConfig_srctstep = 0,

.TransferConfig_deststep = 0,

配置以16bit为单位

bsize = 4 说明一个burst 传5个字

srcbstep = 3 说明每次在source那边每次的偏移为3

desbstep = 0说明每次在dest那边每次的不偏移最后的DMAdestbuf结果为

现象:每次在第1个位置按步长12来传输 如果是以32bit为单位 那就是 6 7

为什么bsize是4 反而只有第一个点有数据 因为 desbstep = 0 还有 TransferConfig_deststep = 0

这是DMAsource里的数据

void DMACH1TransferConfig(Uint16 tsize, int16 srctstep, int16 deststep)

void DMACH1WrapConfig(Uint16 srcwsize, int16 srcwstep, Uint16 deswsize, int16 deswstep)

srcwsize:

这些位指定了在包装回来之前传输地址指针的数量。要禁用包装函数,请将包装大小位字段设置为大于转移大小位字段的数字

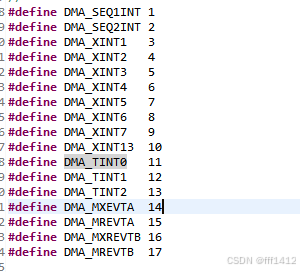

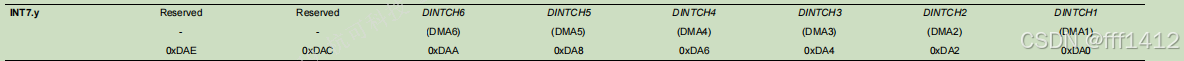

void DMACH1ModeConfig(Uint16 persel, Uint16 perinte, Uint16 oneshot, Uint16 cont, Uint16 synce, Uint16 syncsel, Uint16 ovrinte, Uint16 datasize, Uint16 chintmode, Uint16 chinte)

-

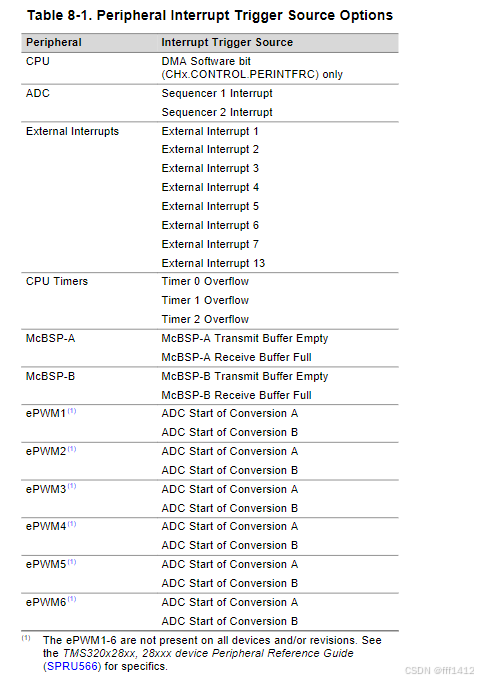

perselPassed DMA channel as peripheral interrupt source 中断触发源

可选参数:

对应的是这张图

28335 没法用PWM来触发DMA

-

perintePeripheral interrupt enable 外设中断使能

外设中断触发器启用位:此位将启用/禁用DMA中的选定外设中断触发器。0h =中断触发器。所选的外围设备和软件都不能启动DMA突发。1h =中断触发。 -

oneshotOneshot enable Oneshot使能

参数:

ONESHOT_DISABLE:

每个事件触发器只执行一个突发传输。

ONESHOT_ENABLE: subsequent burst transfers occur without additional event triggers after the first event trigger. 一旦开始,这一系列的数据传输会自动继续进行,不需要每次传输都进行单独的触发 -

contContinous enable

参数:

CONT_DISABLE: 控制寄存器中的RUNSTS位在传输结束时被清除,从而禁用DMA通道

CONT_ENABLE: 传输结束时不清除RUNSTS位 -

synce:

同步启用位:如果此位设置为1,如果由周围位字段选择,则识别同步信号。

此同步信号用于将ADC中断事件触发器同步到DMA包装计数器。如果此位为0,则将忽略该同步事件

参数:

SYNC_DISABLE: 禁用同步

SYNC_ENABLE: 启用同步 -

syncsel同步效果的源或目标

同步模式选择位:此位选择SRC或DST包装计数器是否由同步函数控制(如果由SYNCE位启用)。

SYNC_SRC: SRC包装计数器控制

SYNC_DST: DST wrap counter controlled -

ovrinte

启用溢出中断功能:此位设置为1时,使DMA能够在检测到溢出事件时生成中断。当设置了插入时间并发生另一个中断事件时,会产生溢出中断。

正在设置的永久flg表示以前的外围事件被锁定,DMA没有提供服务。

参数:

OVRFLOW_DISABLE:禁用溢出中断

OVEFLOW_ENABLE: 启用溢出中断 -

datasize:数据大小模式位:此位选择DMA信道是否一次传输16位或32位的数据。

参数:

SIXTEEN_BIT: 16位

THIRTYTWO_BIT: 32位 -

chintmodegenerate interrupt to CPU at beginning/end of transfer 如果选择产生中断 是在传输前还是传输后 -

chinte:通道中断启用位:此位启用/禁用针对CPU的相应DMA通道中断(通过PIE)。

参数:

CHINT_DISABLE:禁用DMA通道中断

CHINT_ENABLE:启用DMA通道中断

StartDMACH1();

启动DMA

部分图

IER中断

2047

2047

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?