以下错误也可能是由于其他错误所引起,我写的只是我遇到的错误,所以如果按照下面的方法依旧无法解决,并不一定是我的方法有问题,这时建议寻找其他人的解决经验。

verilog语言里需要仔细检查自己写的变量名是否上下一致。

- 对于模块的输入变量,如果想要将其作为if或case的参数,那么需要将if或case放到always语句中

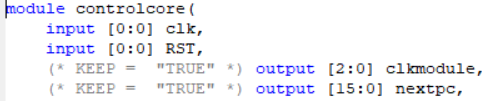

- 在编辑.cdc文件时,一部分例化模块没有出现。我在网上查到一个原因是

图片来源:https://www.cnblogs.com/geekite/p/5241638.html

但是我已经在总的模块中声明了,所以可能是信号被优化,这时可以对不想被优化的信号前面加入(* KEEP = “TRUE” *),就像这样:

如果仍然被优化,可以考虑将该信号绑定到板子的输出上

3.Syntax error near “£”.

加入了中文符号,比如中文逗号,中文冒号。

4.Size mismatch in connection of port . Formal port size is 16-bit while actual signal size is 8-bit.

一种情况:网上搜到的说是,n+1位的变量,你用的是第n位的变量

另一种情况:变量名定义时写的是123456,但是在后面误写为12356

另一种情况:总模块all,分模块a,b,c,d,e。

all的output是x1,y1,z1,a的output是x1,y1,z2,同时你在总模块all里用到了z2,这时它会默认z2为1位,从而产生这个警告。

解决方法:我采用的是将a的输出z2也作为all的输出,但是感觉这样在分模块的输出较多时比较累赘,暂时还没有想到别的方法。

5.经过一番修改,原本正确的仿真波形变成了XXXXX

原因一:缩短了某些变量的位数,导致判断错误

eg:修改之前使用的是32位变量lmd,if(lmd == 32’hffff ffff),之后将lmd修改为8位,但是判断条件没有修改,这时应该修改为 if(lmd == 8’hff)

6.连接开发板后显示Found 0 Core Units in the JTAG device Chain,或者显示如下图片,也就是红框部分是空白:

将总模块中的output转化为wire

7.Bitstream:stanbsbitfile.c:3408:1.57 - Incorrect number of bits in

重新运行一次生成二进制文件

转自:http://blog.sina.com.cn/s/blog_66c807290102wta5.html

807

807

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?