概述

用软件开发的思想来完成硬件设计的工作,这就是可编程逻辑器件(PLD)的功能,而FPGA就是其中的一种,即现场可编程门阵列。

它是一种SRAM编程器件(此外还有熔丝与反熔丝、UEPROM 、EEPROM等),掉电需要重新进行程序配置。是一种半定制电路。

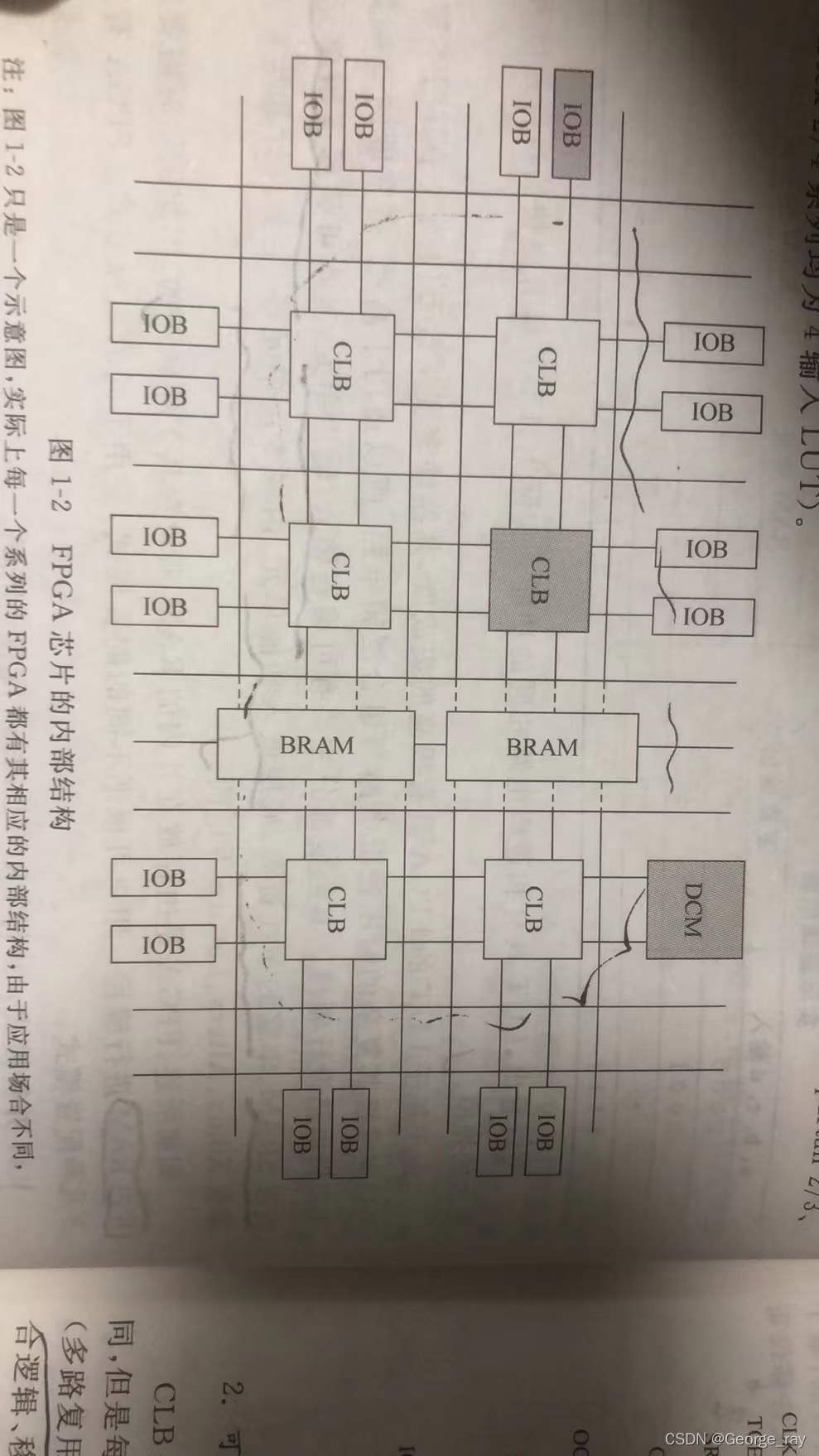

结构

采用的是基于SRAM工艺的查找表结构。(LUT可以看成是一种有4(或6)位地址线的161或641的RAM),在写好了逻辑电路以后,开发软件会把逻辑电路不同输入的所有结果存到sram去,这就相当于填好了一个"真值表"。这样根据输入的信号(相当于SRAM的地址,就可以找到对应的结果进行输出)。在fpga里面有成千上万的LUT。基本组成:

1.可编程输入\输出单元(IOB)—与BANK有关

2.可配置逻辑块(逻辑阵列块CLB) :FPGA内部基本逻辑单元,有一个可配置的开关矩阵、选路器与触发器。

3.数字时钟管理模块\模拟相位环路锁定

4.嵌入式块RAM

5.布线资源:全局、长、短、分布四种

6.底层内嵌功能单元与内嵌专用硬核

开关矩阵是高度灵活的,可以对其进行配置以便处理组合逻辑、移位寄存器或RAM。

特点

有丰富的FF触发器,更适合完成时序逻辑电路的设计;分段式布线结构决定了其信号的延时是不可预测;有很大的编程灵活性;集成度比较高;基于SRAM编程,所以可以任意编程。

可以解决全定制ASIC流片后不可修改的不足;也能克服PLD\CPLD中可编程器件门电路有限的缺点。

工作原理

查找表:实质上就是一种RAM,FPGA之所以可以反复编程就是因为有查找表的存在。当用户通过原理图或者HDL语言描述了一个逻辑电路之后,FPGA开发软件会通过逻辑综合实现该逻辑RTL,并将结果写入SRAM中,每一组输入信号就是等同于需要进行查表的地址值,随后开发软件会寻找出对应地址的内容,然后输出。

目前fpag仍基于LUT,但概念和性能远不止于此,比如ZYNQ。

配置模式

- 串行模式:PROM串行配置FPGA;

- 并行模式:Flash、PROM串行配置FPGA;

- 主从模式:一片PROM配置多片FPGA;

- 外设模式:将FPGA作为微处理器的外设,由微处理器对其进行编程。

设计流程

需求分析–HDL语言描述–功能仿真–综合–综合后仿真(把综合产生的标准延时文件反标到综合仿真模型中去?)–布局布线–实现后进行时序仿真(把布局布线的延时信息反标到设计网表中来看有没有时序违规)–配置下载–在片测试。

软核、固核、硬核

硬核、软核都可有DSP,那究竟这三种有什么区别?

软核:综合之前的寄存器RTL(传输级)模型,只经过功能仿真,必须还要经过综合以及布局布线后才能使用。

固核:带有布局规划的软核,等于RTL代码和具体工艺网表的混合形式。和软核相比,灵活性差但可靠性好。IP固核的设计程度则是介于软核和硬核之间,除了完成软核所有的设计外,还完成了门级电路综合和时序仿真等设计环节。一般以门级电路网表的形式提供给用户。

硬核:经过验证的设计版图。已经实现了布局和工艺固定、前端和后端验证也已经完成。有知识产权。但不占用fpga内部的逻辑资源和存储单元,运行速度高且不影响周边的逻辑布线。CDM(时钟管理单元)、DSP、BRAM、SDRAM控制器、ARM等都是。

5388

5388

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?