PS端以太网通过PL端扩展方法记录

我的板卡上的FPGA选用的是xilinx的z7系列的片子,型号是XC7Z045-2FFG900I,选用的phy的型号是marvell的88e1116RA0-NNC1C000。通过PL端与phy芯片相连接,本文是记录pS端的以太网通过EMIO扩展到PL端的方法。

1、 新建FPGA工程,我的工程命名为z7_1g_ethernet。

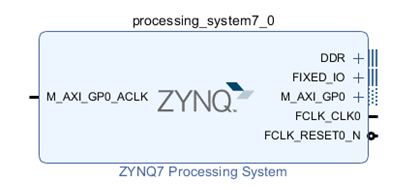

2、 新增block,block中添加模块,首先添加z7的PS模块。如下图

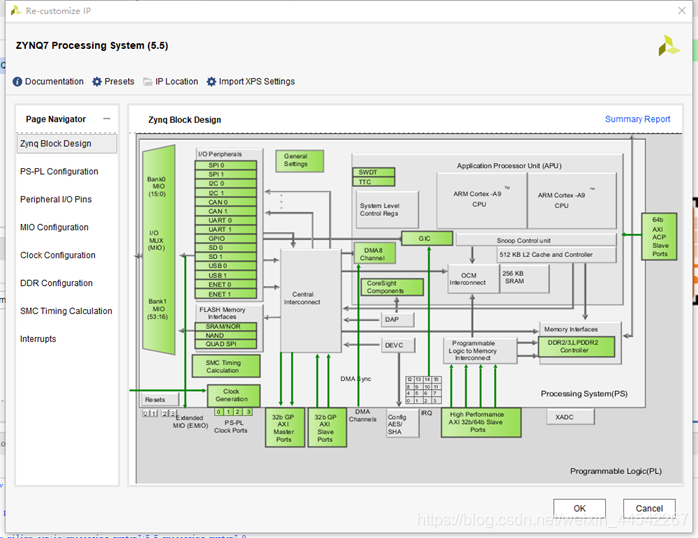

3、 对z7的PS端进行配置,双击打开如下图所示:

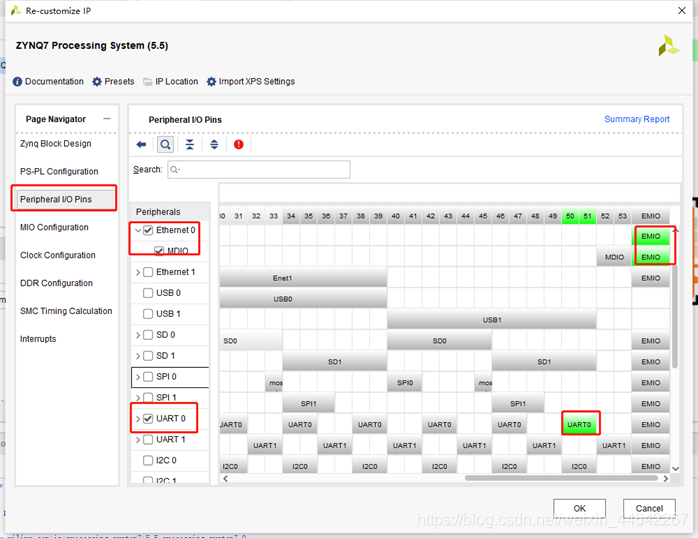

3.1对peripheral进行配置,如下图所示:由于我的板子上与Ethernet0复用的的各个MIO口没有用到,因此我们选择Ethernet0通过PL端来扩展,因此选择Ethernet并MDIO,二者均选择EMIO。选择PS端的UART0接口作为调试候串口

3.2时钟配置,我板上的时钟是33.333mHz的,因此时钟填

本文详细记录了如何在Xilinx Z7 FPGA板卡上通过PL端扩展实现以太网连接,使用Marvell 88E1116RA0-NNC1C000 PHY芯片,通过EMIO扩展Ethernet0,配置PS端的UART0为调试串口,并介绍从配置FPGA工程、转换接口到管脚约束的完整过程,最后通过SDK创建应用项目进行网络测试。

本文详细记录了如何在Xilinx Z7 FPGA板卡上通过PL端扩展实现以太网连接,使用Marvell 88E1116RA0-NNC1C000 PHY芯片,通过EMIO扩展Ethernet0,配置PS端的UART0为调试串口,并介绍从配置FPGA工程、转换接口到管脚约束的完整过程,最后通过SDK创建应用项目进行网络测试。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

527

527

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?