1.1、SPI接口组成部分以及功能

SPI接口是一种高速、全双工的同步串行外设接口,允许MCU与各种外围设备进行全双工同步串行通信。SPI总线是三线制,采用主从模式架构,支持一个或多个从设备。常用于单片机EEPROM、FLASH、实时时钟、数字信号处理器等器件的通信。

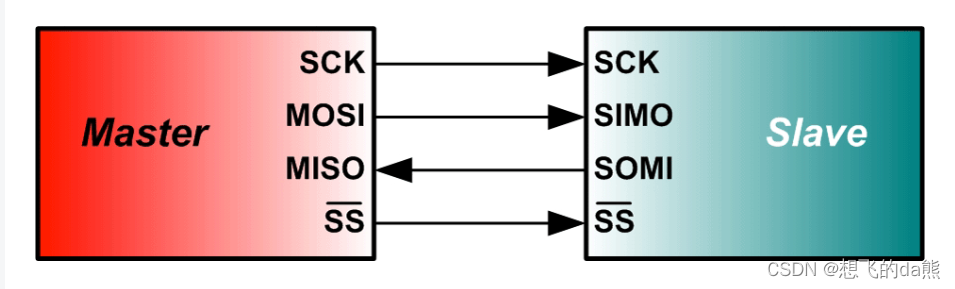

SCK(时钟信号):主设备通过SCK线发送时钟信号,控制数据传输的速率和同步。从设备根据时钟信号的脉冲边沿(上升沿或下降沿)进行数据的读写操作。

MOSI(主设备输出/从设备输入):当主设备需要与从设备通信时,通过MOSI线发送数据给从设备。

MISO(主设备输入/从设备输出):从设备通过MISO线将数据发送给主设备。

SS/CS(片选/从设备选择):主设备通过SS/CS线选择特定的从设备进行通信,确保一次只有一个从设备与主设备进行数据传输。

其他控制信号:如中断线等,用于在特定条件下触发中断,实现中断服务程序的处理。

1.2、单主机多从机SPI通信电路

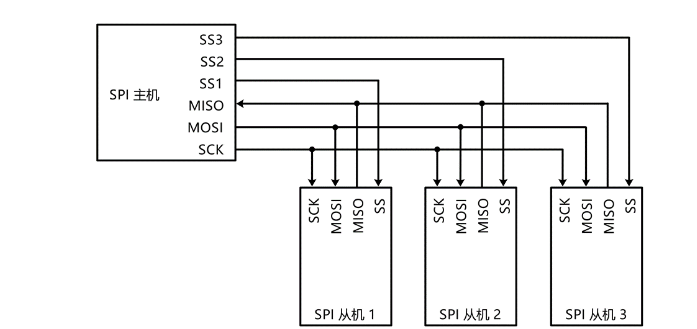

1.硬件连接

将主机的SCK线连接到所有从机的SCK线,以实现时钟信号的共享。

将主机的MOSI线连接到所有从机的MOSI线,用于主机向所有从机发送数据。

将每个从机的MISO线单独连接到主机的MISO线。

每个从机设备连接一根独立的SS/CS线到主机,以便主机能够选择特定的从机进行通信。

2.通信过程

主机通过拉低某个从机的SS/CS线来选择该从机进行通信。

主机通过SCK线产生时钟信号,并通过MOSI线发送数据给被选中的从机。

被选中的从机在时钟信号的同步下,通过MISO线返回数据给主机。

通信完成后,主机拉高SS/CS线,结束与当前从机的通信,并可以选择下一个从机进行通信。主片在访问某一从片时,必须使该从片的片选信号有效;主片在 SCK 信号的同步下,通过 MOSI 线发出指令、地址信息;如需将数据输出,则接着写指令,由 SCK 同步在 MOSI 线上发出数据;如需读回数据,则接着读指令,由主片发出 SCK,从片根据 SCK 的节拍通过 MISO 发回数据。对具有 SPI 接口的从片器件来讲,SCK、MOSI 是输入信号,MISO 是输出信号。

1.3、SPI功能特点及基本架构

1.功能特点

1)3线全双工同步传输,带或不带第3根双向数据线的双线单工同步传输。

2)8位或16位传输帧格式选择。

3)支持多主模式。

4)可编程的时钟极性、相位和数据顺序。

5)可触发中断的专用发送和接收标志、主模式故障、过载以及CRC错误标志。

6)SPI总线忙状态标志。

7)支持可靠通信的硬件CRC。

8)支持DMA功能的1字节发送和接收缓冲器,产生发送和接收请求。

9)兼容I2S音频协议。

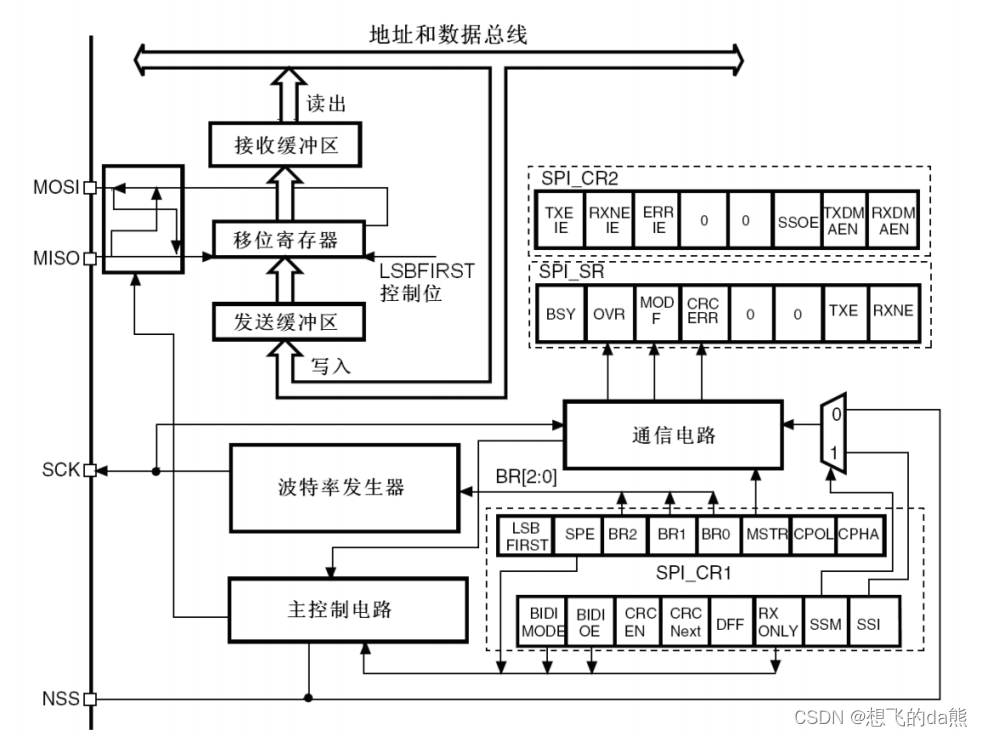

2.基本架构

SPI 的所有硬件架构都从上图中左 MOSI、MISO、SCK及 NSS 线展开的。其内部包括地址和数据总线、接收缓冲区、移位寄存器、发送缓冲区、波特率发生器、主控制电路、通信电路以及3个相关寄存器。

STM32 芯片有多个 SPI 外设,它们的 SPI 通讯信号引出到不同的 GPIO 引脚上,使用时必须配置到这些指定的引脚。

1.4、SPI的NSS两种模式

通过SPI_CR1寄存器的SSM位可以设置NSS两种模式:硬件NSS模式和软件NSS模式。

其软件模式:是通过普通GPIO去控制NSS的高低电平;硬件模式:是NSS连接的引脚使能复用功能,该引脚绑定了外设,不能再作为一个普通IO来使用。

1.硬件NSS模式

硬件NSS又分为hard_input和hard_output,即硬件NSS的输入输出模式。

1)hard_output模式:

应用场景:主要用在SPI主模式下。

工作原理:在这种模式下,NSS连接的引脚使能复用功能,并且作为SPI专用的输出IO使用。SPI硬件会自动控制NSS信号的高低电平,用于选择与之通信的从设备。

配置:当SPI配置为Master模式时,NSS需要配置为hard_output模式。NSS引脚会发送一个低电平信号给从设备,表示主设备要与该从设备进行通信。这个低电平信号通常通过直接连接主设备的NSS引脚和从设备的CS引脚来实现。

特点:由于NSS由SPI硬件自动控制,因此数据传输速率较高。但需要注意的是,当STM32作为主设备时,同一SPI接口上只能连接一个从设备。

2)hard_input模式:

应用场景:主要用在SPI从模式下。

工作原理:在这种模式下,NSS连接的引脚同样使能复用功能,但作为SPI专用的输入IO使用。从设备通过NSS引脚接收来自主设备的信号,以判断是否需要进行通信。

配置:当SPI配置为Slave模式时,NSS需要配置为hard_input模式。NSS引脚会持续监听主设备发送的信号,当检测到低电平时,表示主设备要求与该从设备进行通信。

特点:在从模式下,NSS信号由主设备控制,从设备只能被动地接收并响应。这种模式下,从设备可以根据NSS信号的变化来判断何时开始或结束通信。

2.软件NSS模式

软件NSS模式在SPI通信中,主要通过软件控制NSS信号的高低电平,以模拟硬件NSS信号的功能。

1)工作原理

NSS输出被使能:当STM32或其他SPI主设备工作为主SPI,并且NSS输出已经通过SPI_CR2寄存器的SSOE位使能时,NSS引脚被拉低。所有NSS引脚与这个主SPI的NSS引脚相连并配置为硬件NSS的SPI设备,将自动变成从SPI设备。

NSS输出被关闭:在某些情况下,可能需要关闭NSS的输出功能,以允许多主环境或其他特殊配置。这可以通过软件来控制SPI_CR1寄存器的相关位来实现。

2)配置与操作

设置SPI_CR1寄存器:通过设置SPI_CR1寄存器的NSSM位来使能软件NSS模式。在这个模式下,NSS引脚可以用作其他功能,而内部NSS信号电平可以通过写SPI_CR1的SSI位来驱动。

控制NSS电平:在软件NSS模式下,可以通过软件代码来控制NSS信号的高低电平。通常涉及到对GPIO端口的操作,因为NSS引脚通常连接到某个GPIO端口上。

数据传输:当NSS信号被正确设置后,SPI主设备和从设备之间就可以进行正常的数据传输。在数据传输过程中,NSS信号的状态将保持不变,直到数据传输完成或需要改变通信对象。

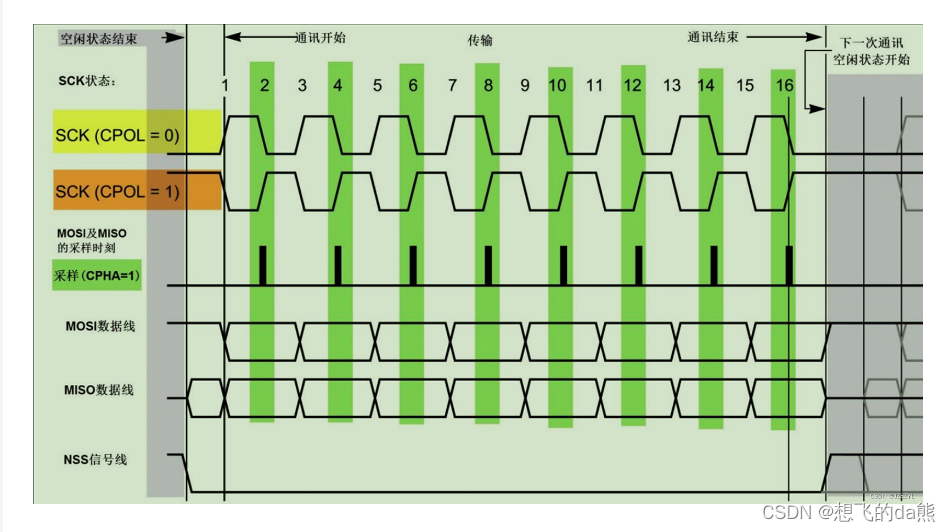

1.5、时钟相位和极性

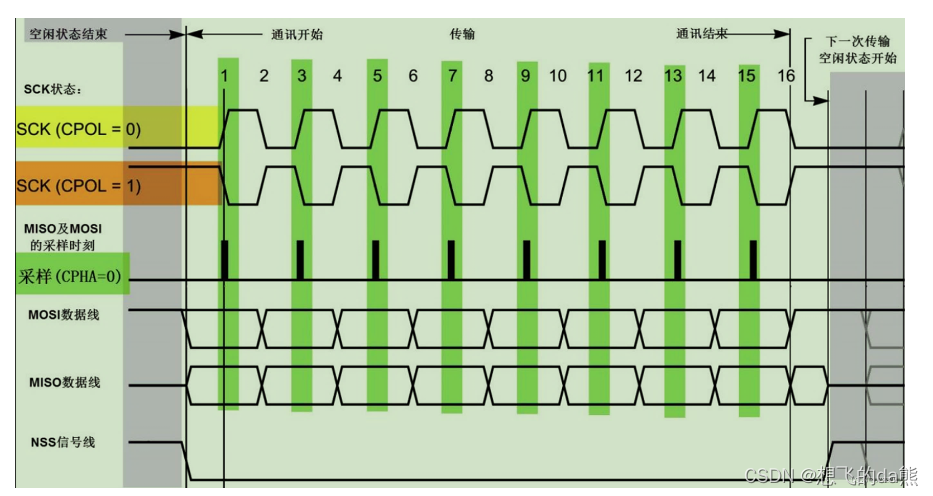

时钟相位和极性决定了SPI通信中的时序和数据采样方式。

1. 时钟极性(CPOL)

定义:时钟极性定义了SCLK时钟线空闲状态时的电平。

取值与含义:

CPOL=0:SCLK时钟信号线在空闲状态时的电平为低电平,因此有效状态为高电平。

CPOL=1:SCLK时钟信号线在空闲状态时的电平为高电平,因此有效状态为低电平。

2. 时钟相位(CPHA)

定义:时钟相位定义了数据位相对于时钟线的时序(即相位),即决定了何时进行信号采样。

取值与含义:

CPHA=0:在时钟信号SCK的第一个跳变沿(取决于CPOL的值,可能是上升沿或下降沿)采样。当CPOL=0时,采样发生在SCK的上升沿。当CPOL=1时,采样发生在SCK的下降沿。

CPHA=1:在时钟信号SCK的第二个跳变沿(取决于CPOL的值,可能是上升沿或下降沿)采样。当CPOL=0时,采样发生在SCK的下降沿。当CPOL=1时,采样发生在SCK的上升沿。

3. SPI通信模式

时钟极性和时钟相位的组合定义了SPI通信的四种模式:

模式0(CPOL=0, CPHA=0):空闲时低电平,数据在第一个上升沿采样。

模式1(CPOL=0, CPHA=1):空闲时低电平,数据在第二个下降沿采样。

模式2(CPOL=1, CPHA=0):空闲时高电平,数据在第一个下降沿采样。

模式3(CPOL=1, CPHA=1):空闲时高电平,数据在第二个上升沿采样。

数据线被采样,都是等待数据线变化稳定半个时钟周期进行采样

由CPOL及CPHA的不同状态,SPI分成了四种模式,主机与从机需要工作在相同的模式下才可以正常通讯,因此通常主机要按照从机支持的模式去设置。

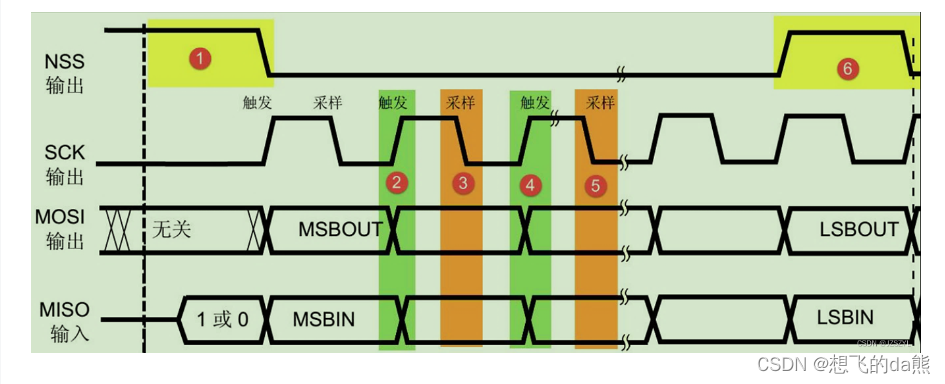

1.6、主从模式下数据发送和接收过程

起始信号:NSS信号线由高到低,是SPI通信的起始信号

结束信号:NSS信号线由低到高,是SPI通信的停止信号数据传输:SPI使用MOSI及MISO信号线来传输数据,使用SCK信号线进行数据同步。MOSI及MISO数据线在SCK的每个时钟周期传输一位数据高位在前低位在后,且数据输入输出是同时进行的。

1.SPI主模式

在主模式下,MOSI引脚是数据输出,而MISO引脚是数据输入,SCK引脚产生串行时钟。

1)配置步骤

通过SPI_CR1寄存器的BR位定义串行时钟波特率。

选择CPOL和CPHA位,定义数据传输和串行时钟间的相位关系(见图212)。

设置DFF位来定义8位或16位数据帧格式。

配置SPI_CR1寄存器的LSBFIRST位定义帧格式。

如果需要NSS引脚工作在输入模式,硬件模式下,在整个数据帧传输期间应把NSS脚连接 到高电平;在软件模式下,需设置SPI_CR1寄存器的SSM位和SSI位。如果NSS引脚工作 在输出模式,则只需设置SSOE位。

必须设置MSTR位和SPE位(只当NSS脚被连到高电平,这些位才能保持置位)。

2)数据发送过程

当写入数据至发送缓冲器时,发送过程开始。 在发送第一个数据位时,数据字被并行地(通过内部总线)传入移位寄存器,而后串行地移出到 MOSI脚上;MSB在先还是LSB在先,取决于SPI_CR1寄存器中的LSBFIRST位的设置。数据从 发送缓冲器传输到移位寄存器时TXE标志将被置位,如果设置了SPI_CR1寄存器中的TXEIE 位,将产生中断。

3)数据接收过程

对于接收器来说,当数据传输完成时: 传送移位寄存器里的数据到接收缓冲器,并且RXNE标志被置位。 如果设置了SPI_CR2寄存器中的RXNEIE位,则产生中断。 在最后采样时钟沿,RXNE位被设置,在移位寄存器中接收到的数据字被传送到接收缓冲器。读 SPI_DR寄存器时,SPI设备返回接收缓冲器中的数据。 读SPI_DR寄存器将清除RXNE位。 一旦传输开始,如果下一个将发送的数据被放进了发送缓冲器,就可以维持一个连续的传输 流。在试图写发送缓冲器之前,需确TXE标志应该为’1’。

2.SPI从模式

在从模式下,MOSI引脚是数据输入,而MISO引脚是数据输出。SCK引脚用于接收从主设备来的串行时钟。其中SPI_CR1寄存器中BR的设置不影响数据传输速率。

1)配置步骤

设置DFF位以定义数据帧格式为8位或16位。

选择CPOL和CPHA位来定义数据传输和串行时钟之间的相位关系。为保证正确的数据传输,从设备和主设备的CPOL和CPHA位必须配置成相同的方式。

帧格式(SPI_CR1寄存器中的LSBFIRST位定义的”MSB在前”还是”LSB在前”)必须与主设备 相同。

硬件模式下,在完整的数据帧(8位或16位)传输过程中, NSS引脚必须为低电平。在NSS软件模式下,设置SPI_CR1寄存器中的SSM位并清除SSI 位。

清除MSTR位、设置SPE位(SPI_CR1寄存器),使相应引脚工作于SPI模式下。 在这个配置中,MOSI引脚是数据输入,MISO引脚是数据输出。

2)数据发送过程

在写操作中,数据字被并行地写入发送缓冲器。 当从设备收到时钟信号,并且在MOSI引脚上出现第一个数据位时,发送过程开始(此时 第一个位被发送出去)。余下的位(对于8位数据帧格式,还有7位;对于16位数据帧格式,还有 15位)被装进移位寄存器。当发送缓冲器中的数据传输到移位寄存器时,SPI_SP寄存器的TXE 标志被设置,如果设置了SPI_CR2寄存器的TXEIE位,将会产生中断。

3)数据接收过程

对于接收器,当数据接收完成时: 移位寄存器中的数据传送到接收缓冲器,SPI_SR 寄存器中的RXNE标志被设置。如果设置了SPI_CR2寄存器中的RXNEIE位,则产生中断。 在最后一个采样时钟边沿后,RXNE位被置’1’,移位寄存器中接收到的数据字节被传送到接收缓 冲器。当读SPI_DR寄存器时,SPI设备返回这个接收缓冲器的数值。 读SPI_DR寄存器时,RXNE位被清除。

1587

1587

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?