一、128b/130b编码

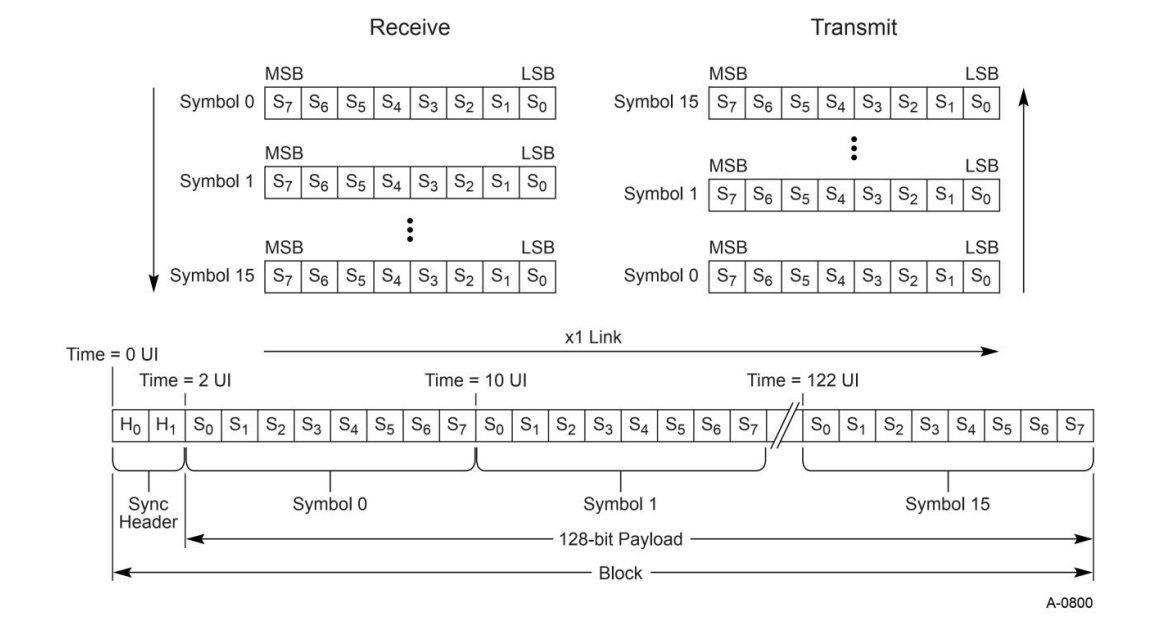

PCIE1/2使用8b/10b编码,PCIE3/4/5使用128b/130b编码。128b/130b相比8b/10b(80%)而言有更高的带宽利用率。严格意义上来说128b/130b不是编码,而是将16个字节数据组合在一起(128bit),再加Sync Header(2bit),共同组成。

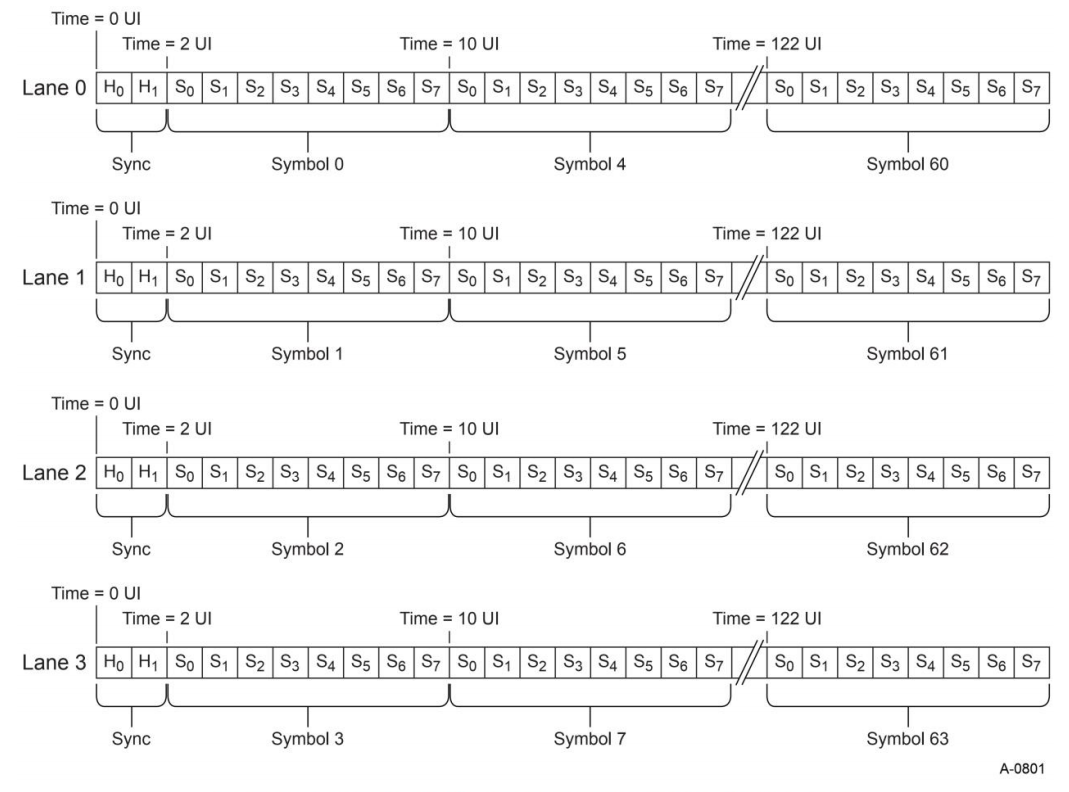

一个4lane的例子:

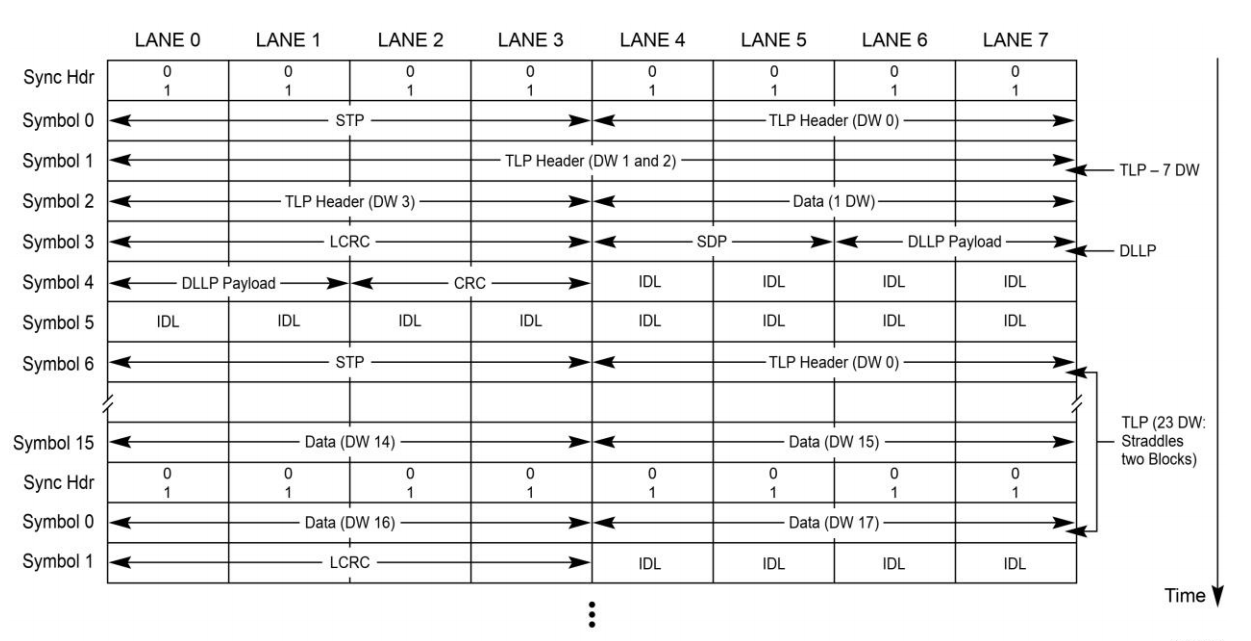

数据包在X8 lane上分布

Sync Header有两种:

10b表示Data Block,包含TLP/DLLP/Framing Token等

01b表示Ordered Set Block;包含TS1OS/TS2OS/EIOS/EIEOS等

二、Data Block

Data Block 的有效载荷是符号流(Symbol Stream),定义为“Data Stream”,它由 Framing Tokens、TLP 和 DLLP 组成。数据流的每个符号都放置在链路的单个 Lane 中,并且符号流在链路的所有Lane上分布,并跨越 Block 边界。 数据流从紧随 SDS 有序集的Data Block的第一个符号开始。当检测到帧错误时,或者以除 SKP 有序集以外的有序集之前的数据块的最后一个符号时,该数据流结束。 数据流中出现的 SKP 有序集具有特定要求,如以下所述。

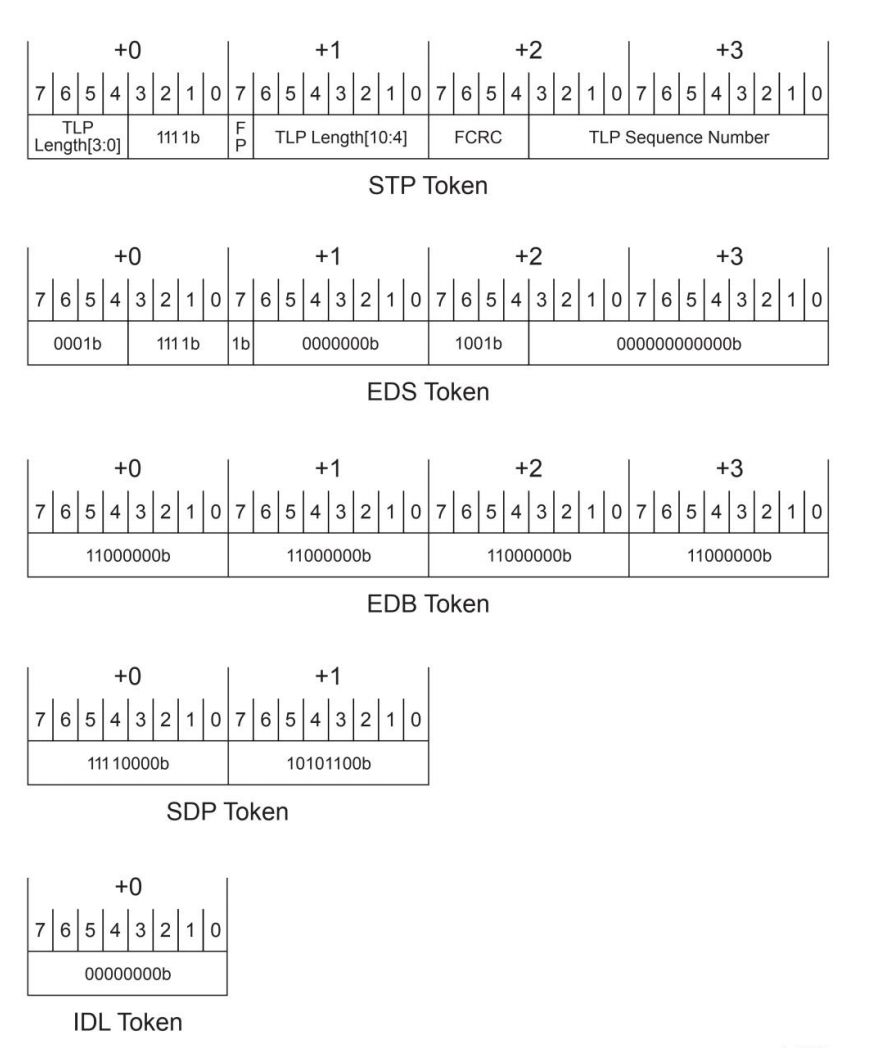

对于Data Block而言,需要依据Framing Token(gen3/4/5才有)来区分Payload中的数据类型是TLP或者DLLP。Framing Token有以下五种:

Start TLP(STP):TLP开头

Start DLLP(SDP):DLLP开头

Logical Idle(IDLA):逻辑空闲(00h)

End of Data Stream(EDS):提示下一个block是Ordered Sets

End Bad(EDB):表示当前为无效包

三、Ordered Set Block

在gen1/2模式下,物理层首先完成位锁定(Bit Lock),然后完成字节锁定(Byte Lock),只有gen3/4/5中完成位锁定(Bit Lock),再开始块锁定(Block lock)。完成块锁定需要借助EIEOS(00/FF交替出现)。

Ordered Set共有五种类型:

TS1/TS2 Ordered Set(TS1OS/TS2OS):用于链路初始化和训练;

Electrical Idle Ordered Set(EIOS):用于控制PHY进入电气IDLE状态;

FTS Ordered Set(FTSOS):用于L0s状态到L0状态的切换;

SKP Ordered Set(SOS):用于CTC(Clock Tolerance Compensation);

Electrical Idle Exit Ordered Set(EIEOS):用于控制PHY退出电气IDLE状态;

Start of Data Stream Ordered Set(SDS):当链路准备发送数据流时,会先发送SDS,然后进入L0状态;

Note:几乎所有的Ordered Set的Payload都是16个字节,除了SKP(可以是8/12/16/20/24)。

四、Ordered Set SKP的使用

为什么会有SKP这个东西?Serdes是有RX和TX二部分组成的,采用的是非同源时钟架构Independent Reference Clock Mode(IR),存在时钟偏差,这种架构的CDR一般是二阶系统,否则不能消除这个偏差。作为PCIe的物理层在向对端发送数据时自然携带了这种偏差。

在接收端,接收到的数据是按照对面发送端的频率接收的。当这些数据传给接收端的上层逻辑的时候,等于是从发送端的时钟域,穿越到接收端的时钟域,此时,如果双方的频率存在偏差,就会存在数据溢出问题,一般接收机内部都会内置弹性缓冲器,而在PCIe中,还要结合SKP字符解决这种不同频溢出问题。

Note:与IR相反的是同源时钟Common Clock Mode(CC)。

虽然弹性缓冲区可以解决部分溢出部分,但又不能全部解决,不如一直写快读慢,迟早缓冲区会存满数据。加入SKP就不一样了,如它的名字一样具有丢弃的意思,发送端在发送数据时,会耗费一定的使用用于发送SKP,但接收方却是直接忽略不进行处理,这样间接的实现收发平衡。

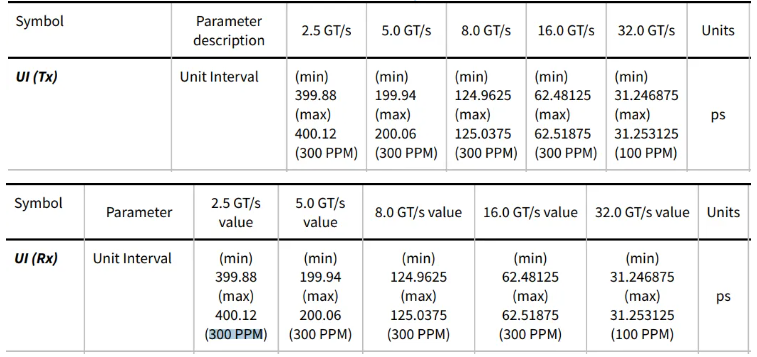

通过SPEC手册计算一下如何设计SKP的插入频率。以非同源时钟架构不开SSC情况为例。如果发送端和接收端采用非同源时钟,根据PCIe Spec对UI(TX)和UI(RX)的规定:

可以看出,在32GT/s速率下,发送端和接收端最大会相差200PPM。其他相差600PPM。以600PPM为例进行计算。通常电脑PCIe的插槽口提供的时钟源是100MHz,则协议允许的频率偏差可以是+/-300 PPM,最差的情况,两个不同的时钟源频率最大可能会有600PPM的偏差。即一个时钟源的频率是标准频率+300PPM等于100.0003MHz,而另一个时钟源的频率是标准频率-300PPM等于99.9997MHz。由于串行速率与参考时钟是倍频关系,而相同时间内发送bit的数量与串行速率也是倍数关系,因此在某段时间内,写入缓冲Buffer的bit量与读出的bit量也会呈现相同的偏差关系,即写入一百万个bit的时间与读出一百万减去600个bit的时间相同。那么可以计算出每多少个bit就会出现1个bit的偏差:

1000000/600 = 1666.6667

即大约发送1666个bit,双方会产生1个bit的偏差。按照这个规律发展下去,就可以得到当双方偏差达到600个bit的时候,发送端大约发送了一百万个bit。

在这里,说下不同编码下的SKP发送。

8b/10b:

对发送端而言,一个SKP有序集由一个COM符和三个SKP符组成。但 Loopback.Active 状态下的 Loopback 从设备 除外。收到的 SKP 有序集是一个 COM 符号,后跟一到五个 SKP 符号

对接收端而言,一个SKP有序集由一个COM符和一到五个SKP符组成。

收发之间的差异来自retimer,根据协议描述,retimer可以在传递8b/10b编码的SKP有序集时增加或减少1个SKP符。

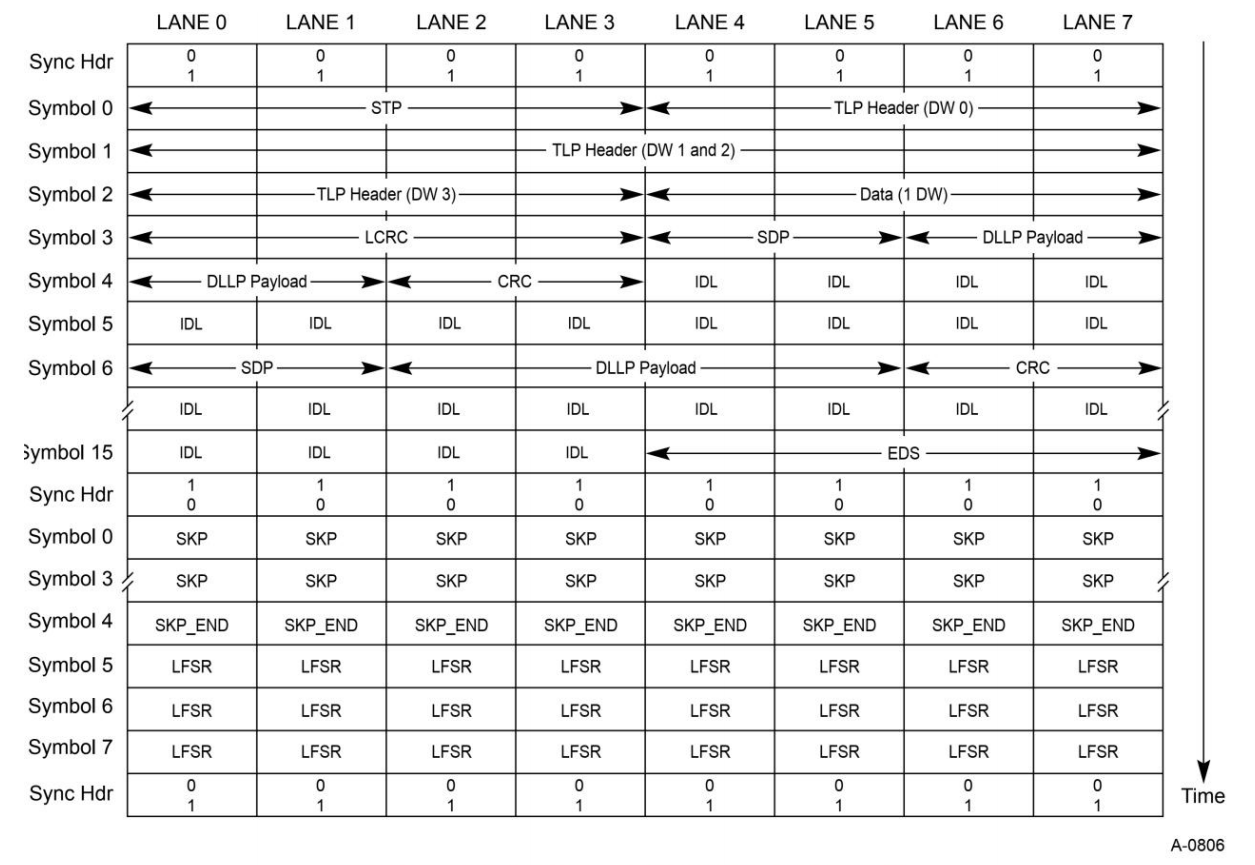

128b/130b

对发送端而言,一个有SKP序集由4*4SKP符组成。

对接收端而言,一个有SKP序集由2/3/4/5/6*4SKP符组成。

差异同样来自retimer,根据协议描述,retimer可以在传递128b/130b编码的SKP有序集时增加或减少4个SKP符。

Standard SKP与Control SKP

在GEN2以上的速率工作时,存在两种SKP有序集,分别是standard和control。当不采用flit-mode时,8GT/s速率下只需使用standard SKP,16GT/s、32GT/s、64GT/s则需使用两种SKP。当采用flit mode时,所有速率下都需使用两种SKP。所有lane在同一时间都必须传输相同种类的SKP,如全部传输standard SKP或全部传输control SKP。

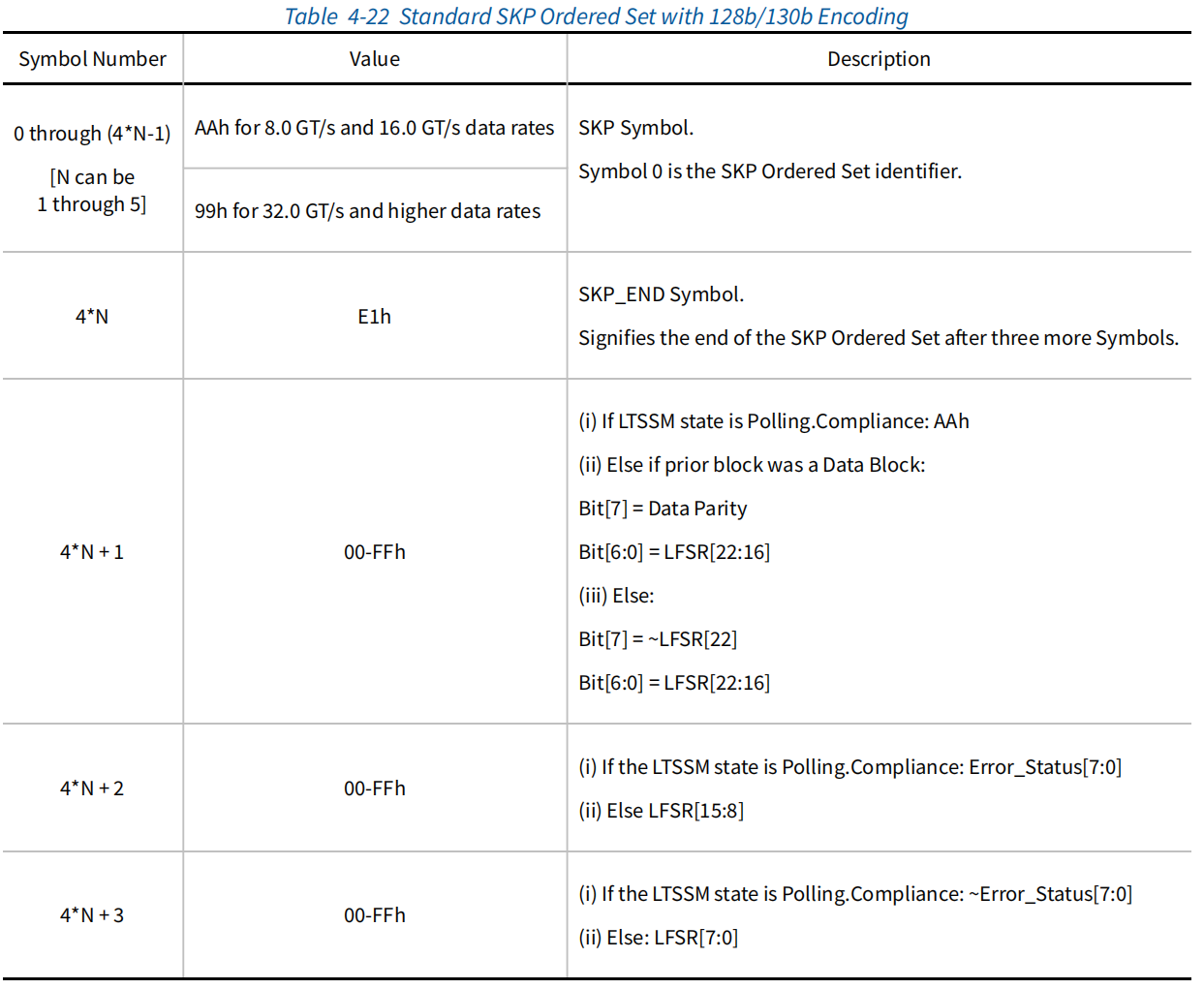

Standard SKP格式如下图所示

可以看出首先发送SKP symbol、紧随着是SKP END symbol,从第三个符号起就需要判断

(1)若LTSSM处于Polling.Compliance状态,则后续三个symbol分别为:AAh,Error_Status[7:0]与~Error_Status[7:0]。

(2)若前一个block为data block,则后续三个symbol分别为:{Data Parity, LFSR[22:16]},LFSR[15:8]与LFSR[7:0]。

(3)否则后续三个symbol分别为:{~ LFSR[22], LFSR[22:16]},LFSR[15:8]与LFSR[7:0]。

在8GT/s且非flit模式下,若SKP接在Data block之后,则parity位继承data block的数据进行计算。在传输SKP或SDS后初始化parity值。

在16GT/s,32GT/s或flit mode下的8GT/s下,除data block外,FEC的数据也需要继承;除了SKP与SDS外,Recovery.Speed状态下也需初始化。

LFSR指扰码逻辑的初始值;传输 LFSR 值使得跟踪工具即使在比特流中间需要重新获取块对齐时也能够运行。由于跟踪工具无法强制链路进入Recovery 状态, 因此如果需要的话它们可以重新获取比特锁定,并监视 SKP 有序集以获取Block alignment 并执行Lane-to-Lane de-skew。可以将 “SKP 有序集中的 LFSR 值加载到其LFSR中,以开始解释比特流。必须注意的是,使用比特流时,可能会将其别名为非块边界上 的 SKP 有序集。跟踪工具可以通过使用特定于实现的方式(例如,接收固定数量的有效数据包或同步头或后续的 SKP 有序集)来验证其块对齐。

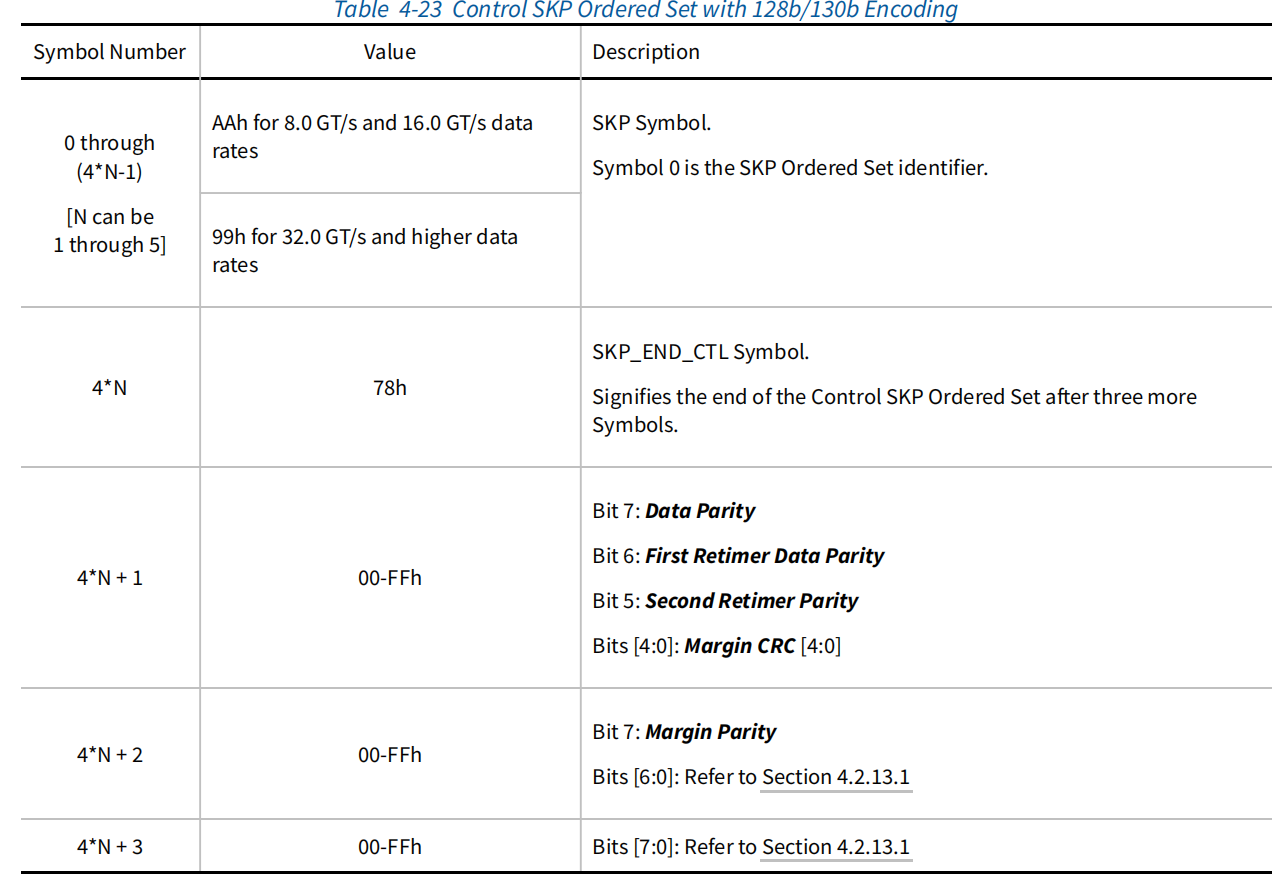

Control SKP格式如下图所示:

首先发送的是上文提到过的SKP symbol,然后是SKP END CTL symbol,接着是{Data Parity, First Retimer Data Parity, Second Retimer Data Parity, Margin CRC [4:0] },最后是Margin Party与Margin Payload,这部分与lane margin有关。

SKP发送规则

对于同一link的所有lane,应以相同的速率发送Symbol,指相差0ppm。同时,这些lane应当同时发送相同数量和类型的SKP有序集。

在8b/10b编码模式下,如果未支持SRIS或双方沟通在SRIS模式下使用低SKP频率,则每间隔1180到1538个symbol发送一个SKP。如果在SRIS且双方未沟通在SRIS模式下使用低SKP频率,则最多每隔154个symbol就需要发送一次SKP。

在128b/130b编码模式下,如果未支持SRIS或双方沟通在SRIS模式下使用低SKP频率,则每间隔370到375个symbol发送一个SKP。如果在SRIS且双方未沟通在SRIS模式下使用低SKP频率,则最多每隔38个symbol就需要发送一次SKP。Loopback模式下相同。若使用flit mode且不在loopback模式下,则需要以flit模式中描述的方式传输SKP。

可以使用control SKP的速率下,当链路状态在L0p,或LTSSM状态在Configuration.Idle或Recovery.Idle时,必须传输control SKP;在数据流中则需要交替传输standard SKP与control SKP。

在1b/1b编码模式下,如果未支持SRIS或双方沟通在SRIS模式下使用低SKP频率,则每间隔740到750个symbol发送一个SKP。如果在SRIS且双方未沟通在SRIS模式下使用低SKP频率,则最多每隔76个symbol就需要发送一次SKP。Loopback模式下相同。

PHY payload在Polling.Compliance下必须为type 1,其他时候在type 0与type 1之间交替传输。

在连续监测有序集时,SKP不被认为是中断。例如training过程中检测8个TS1的过程中,即使中间出现SKP也不会终端TS1的计数。

电气闲时无需传输SKP。同时协议建议在电气闲时重置SKP发送计数。

回归正题,以8b/10b 下SKP Ordered Set的定义为例:

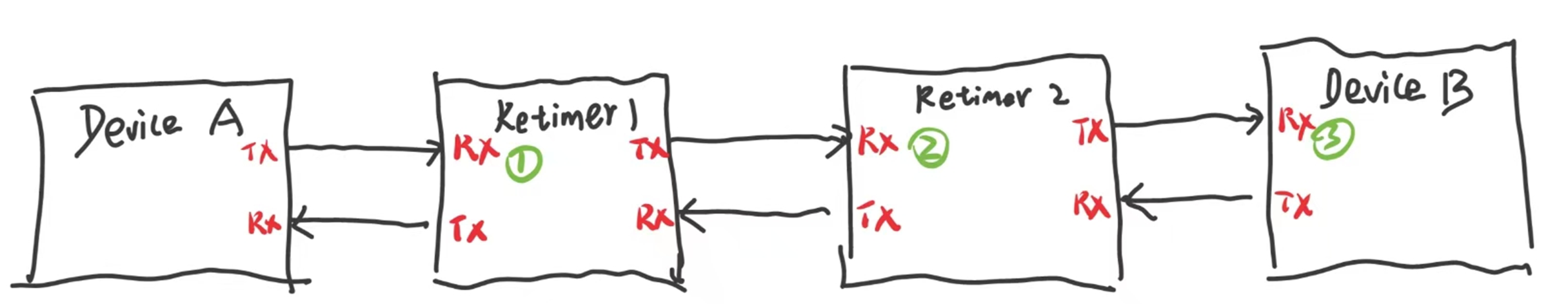

在2.5 GT/s或者5.0 GT/s的链路上,插入的SKP Ordered Set如上图所示,整个SKP Ordered Set由一个COM Symbol加三个SKP Symbol组成。整个PCIe链路最多支持两个Retimer,即如下图所示:

设备A到B从左向右,链路最多跨越时钟域三次,分别在绿色的1,2和3处。每次跨时钟域的时候,协议规定都可以增删一个SKP Symbol,但所以如果1,2和3都是删除动作的话,Device A需要准备三个SKP Symbol才够用。而如果大家都是增加一个SKP Symbol的话,在3的前面可能会遇到一个COM带5个SKP Symbol的情况。

当Symbol采用8b/10b编码,链路上一个Symbol将由10个bit组成。即一个SKP的Symbol在链路上就是10个bit。如果Device A与Retimer1之间采用了非同源时钟方案,并且双方的频偏达到了600PPM的最大值,那么为了消除这个频偏,Retimer1的接收端就需要通过增加或者删除SKP Symbol的方式解决。而一个SKP Symbol由10个bit组成,这10个bit将能够抵消Device A发送端发送1666x10个bit产生的偏移(600PPM发送1666个bit会有1个bit偏差),换句话说,能够抵消发送1666x10 = 16660个bit的偏差,而每10个bit一个Symbol,16660就是1666个Symbol。所以Device A每发送大约1666个Symbol就要发送一个SKP Ordered Set。为了留有一些裕量,PCIe Spec实际的定义值将会比这个值小。但也不能小太多,如果插入的特别频繁,会导致链路的使用效率下降。目前PCIe Spec规定在没有开SSC的情况下,采用8b/10b编码的链路SKP的插入间隔为1180-1538个Symbol Time之间。

对于128b/130b编码,一个SKP Group由4个SKP Symbol组成,即32个bit。接收端可以一次性增加和移除一个SKP Group。所以这32个bit将能够抵消1666x32 = 53312个bit产生的偏移。所以在使用128/130编码的场景时,一个block由130个bit组成,53312相当于410个block。所以我们的插入的间隔要小于410个block。目前PCIe Spec给出的规范是在370-375个block之间。

如果打开了SSC,发送和接收端的频率偏移有可能超过5000ppm,加上时钟本身的偏移600ppm,最大可以达到5600ppm。同样的方式计算。

204

204

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?