目录

2.4.DDR SDRAM(双数据率同步动态随机存取存储器)

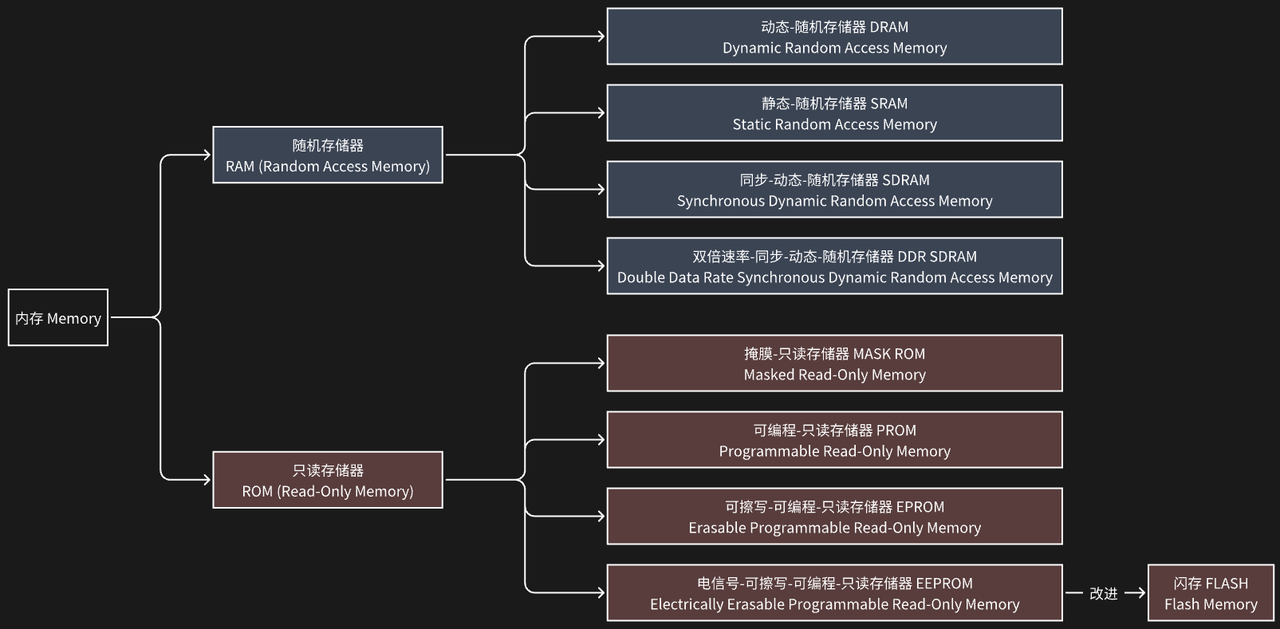

1.RAM 和 ROM

-

RAM:Random Access Memory,随机存储器,可随时进行读写操作,速度快,掉电后数据会丢失,如内存条、SRAM、SDRAM、DDR 等均为 RAM,RAM 一般用于保存程序数据和中间结果;

-

ROM:Read-Only Memory,只读存储器,容量大且掉电后数据不会丢失,适合存储资料,如音乐、图片、视频等信息;

| 类型 | RAM(Random Access Memory) | ROM(Read-Only Memory) |

| 读写特性 | 可读可写,数据可随时被修改或覆盖 | 通常只读(早期类型),现代类型(如 Flash)支持擦写,但性能受限 |

| 数据易失性 | 断电后数据丢失,用于临时存储运行中的程序和数据 | 断电后数据保留,用于长期存储系统启动代码或固定数据 |

| 访问速度 | 极快(纳秒级),与CPU直接交互,支持随机地址访问 | 较慢(微秒级),适合顺序读取,随机访问,性能较差 |

| 主要用途 | 系统内存(如计算机的内存条),存储正在运行的程序和数据 | 存储固件(如 BIOS)、嵌入式系统程序、引导代码等 |

1.1.工作原理差异

-

RAM:

-

基于晶体管或电容存储数据(如 DRAM 使用电容,SRAM 使用触发器);

-

数据以电信号形式存在,需持续供电维持状态(如 DRAM 需保持定期刷新);

-

支持高速随机访问,地址线直接映射到存储单元;

-

-

ROM:

-

数据通过物理结构(如熔丝、浮栅晶体管)存储,无需供电维持;

-

早期类型(如 MASK-ROM)数据在制造时固化,现代类型(如 EEPROM/Flash)可通过电信号读写;

-

访问需通过特定接口(如 SPI、I²C),速度受限于协议;

-

1.2.应用场景

-

RAM:

-

计算机主内存(DDR SDRAM)、显卡显存(GDDR);

-

嵌入式系统中的工作内存(如单片机的 SRAM);

-

缓存数据(如 CPU 缓存 L1/L2/L3);

-

-

ROM:

-

计算机 BIOS(早期为 EPROM,现为 Flash);

-

手机/智能设备的固件(如 Android 系统存储在 eMMC Flash 中);

-

游戏卡带(如任天堂 Switch 卡带使用 NAND Flash);

-

汽车电子控制单元 ECU 的程序存储;

-

1.3.常见类型与技术对比

| 类型 | 特点 | 擦写特性 | 典型应用 |

| SRAM | 高速(纳秒级)、低容量、高成本 | 可无限读写 | CPU 缓存、高速缓冲存储器 |

| DRAM | 低成本、大容量、需定期刷新 | 可无限读写 | 计算机主内存(DDR 系列) |

| MASK-ROM | 数据在制造时固化,不可修改 | 不可擦写 | 早期游戏机卡带、工业控制固件 |

| PROM | 一次性可编程(熔丝熔断) | 仅可写入一次 | 早期固件存储、加密设备 |

| EPROM | 紫外线擦除,可重复编程 | 擦写次数约 1000 次 | BIOS(已淘汰) |

| EEPROM | 电信号擦除,按字节操作 | 擦写次数约 10 万次 | 配置数据存储(如 BIOS 设置) |

| Flash | 电信号块擦除,大容量、低成本 | 擦写次数约 10 万 ~ 100 万次 | SSD、U 盘、手机存储 |

2.RAM 常见类型

| 类型 | DRAM | SRAM | SDRAM | DDR SDRAM |

| 存储单元结构 | 1 晶体管 + 1 电容 | 6 晶体管(触发器) | 同 DRAM | 同 SDRAM |

| 是否需要刷新 | 是(每几毫秒) | 否 | 是 | 是 |

| 时钟同步 | 异步 | 异步/同步 | 同步 | 同步 |

| 数据传输率 | 低(如 100MHz) | 高(如 500MHz) | 中(如 133MHz) | 极高(如 3200MHz) |

| 带宽 | 低(如 0.8GB/s) | 高(如 4GB/s) | 中(如 1.06GB/s) | 极高(如 25.6GB/s) |

| 成本/容量 | 低(适合大容量) | 高(适合小容量) | 中 | 中高 |

| 典型应用 | 计算机主内存 | CPU 缓存、高速缓冲 | 早期计算机内存 | 现代计算机、移动设备 |

2.1.DRAM(动态随机存取存储器)

-

工作原理:

-

基于电容存储数据(充电 = 1,放电 = 0)。

-

电容会漏电,需每隔几毫秒刷新(Refresh)一次,否则数据丢失。

-

-

性能特点:

-

低成本:结构简单(1 个晶体管 + 1 个电容),适合大规模集成。

-

低功耗:刷新操作消耗额外能量,但待机功耗低。

-

速度较慢:存取时间约 10-100ns,刷新操作会引入延迟。

-

-

典型应用:

-

计算机主内存(如 DDR 系列)、显卡显存(GDDR)。

-

服务器、超级计算机等需要大容量内存的场景。

-

2.2.SRAM(静态随机存取存储器)

-

工作原理:

-

基于触发器(Flip-Flop)存储数据,由 6 个晶体管组成一个存储单元。

-

无需刷新,只要供电就保持数据。

-

-

性能特点:

-

高速:存取时间约 1-10ns,比 DRAM 快 10 倍以上。

-

高成本:结构复杂,占用芯片面积大,单位成本是 DRAM 的 10 倍以上。

-

高功耗:静态电流大,适合小容量高速缓存。

-

-

典型应用:

-

CPU 缓存(L1/L2/L3 Cache)、高速缓冲存储器(如网络路由器)。

-

嵌入式系统中的关键数据存储(如 FPGA 内部缓存)。

-

2.3.SDRAM(同步动态随机存取存储器)

-

工作原理:

-

在 DRAM 基础上引入同步时钟,所有操作与系统时钟同步。

-

通过时钟信号的上升沿触发数据传输。

-

-

性能特点:

-

高速:比异步 DRAM 快 30-50%,支持突发传输(Burst)。

-

带宽提升:时钟频率与数据传输率直接挂钩(如 PC133 的时钟为 133MHz,带宽 1.06GB/s)。

-

-

典型应用:

-

2000 年代初期的计算机内存(如 PC100/PC133 SDRAM)。

-

已逐步被 DDR SDRAM 取代,但仍用于某些低功耗嵌入式系统。

-

2.4.DDR SDRAM(双数据率同步动态随机存取存储器)

-

工作原理:

-

在 SDRAM 基础上发展,采用双倍数据率技术。

-

在时钟的上升沿和下降沿各传输一次数据,使带宽翻倍。

-

-

性能特点:

-

极高带宽:例如 DDR4-3200 的时钟为 1600MHz,数据率 3200MT/s,带宽 25.6GB/s。

-

低电压:DDR4 工作电压 1.2V,DDR5 工作电压 1.1V,功耗低。

-

多通道设计:支持双通道/四通道,进一步提升带宽。

-

-

典型应用:

-

现代计算机主内存(如 DDR4/DDR5 内存条)。

-

移动设备(LPDDR 系列)、服务器、游戏主机(如 PS5 使用 GDDR6)。

-

2.5.演进路线

DRAM → SDRAM(同步技术) → DDR SDRAM(双倍数据率) → DDR2 → DDR3 → DDR4 → DDR5DRAM → SDRAM(同步技术) → DDR SDRAM(双倍数据率) → DDR2 → DDR3 → DDR4 → DDR5

每一代 DDR 技术通过提升时钟频率、预取位数和降低电压,实现带宽翻倍和功耗优化,例如:

-

DDR2:引入 4 位预取,时钟频率提升至 800MHz。

-

DDR3:8 位预取,支持 1600MHz,工作电压降至 1.5V。

-

DDR4:16 位预取,最高 3200MHz,电压 1.2V,带宽 25.6GB/s。

-

DDR5:32 位预取,最高 6400MHz,带宽突破 51.2GB/s,支持片上 ECC。

3.ROM 常见类型

| 类型 | MASK-ROM | PROM | EPROM | EEPROM | FLASH |

| 擦除方式 | 不可擦除 | 一次性写入 | 紫外线照射(整片) | 电信号(按字节) | 电信号(按块) |

| 擦写次数 | ∞(只读) | 1 次 | 约 1,000 次 | 约 10 - 100 万次 | 约 10 - 100 万次 |

| 写入速度 | 无(制造时写入) | 慢(需编程器) | 慢(需擦除器) | 较慢(1-10ms/字节) | 快(顺序写入) |

| 读取速度 | 快 | 快 | 快 | 快 | 快(NOR)/较快(NAND) |

| 成本/容量 | 极低(大规模) | 低 | 中 | 高(小容量) | 低(大容量) |

| 典型容量 | 几 KB - 几 MB | 几 KB - 几 MB | 几 KB - 几 MB | 几 KB - 几 MB | 几 MB - 几 TB |

| 应用场景 | 固定程序(如游戏) | 小批量固件 | 早期 BIOS | 配置数据存储 | SSD、U 盘、手机存储 |

3.1.MASK-ROM(掩膜只读存储器)

-

工作原理:

-

数据在芯片制造过程中通过光刻掩膜(Photomask)永久性写入,无法修改。存储单元通过晶体管的连接/断开表示二进制值(如熔断熔丝或离子注入)。

-

-

擦写特性:

-

不可擦除,数据写入后永久固定,需重新流片(Tape-out)才能更新内容。

-

-

典型应用:

-

早期游戏机卡带(如任天堂红白机的游戏卡带)。

-

工业控制设备中的固定程序存储(如电梯控制器固件)。

-

对成本极度敏感且数据无需更新的场景(如遥控器代码)。

-

-

特点:

-

生产成本低,但前期开发成本高,掩膜制作费用约 10 - 100 万美元。

-

3.2.PROM(可编程只读存储器)

-

工作原理:

-

出厂时存储单元全为 1 或 0,用户通过专用编程器一次性写入数据(如熔断内部熔丝或击穿二极管),写入原理基于物理结构的永久性破坏,不可逆转。

-

-

擦写特性:

-

仅能写入一次(One-Time Programmable, OTP),写入后无法擦除或修改。

-

-

典型应用:

-

小批量生产的固件存储(如早期 BIOS 芯片)。

-

加密设备中的密钥存储(如电子钱包)。

-

军工/航空航天领域的高可靠性数据存储(避免意外修改)。

-

-

特点:

-

抗干扰性强,数据稳定性高于可擦写类型,但使用灵活性极低。

-

3.3.EPROM(可擦除可编程只读存储器)

-

工作原理:

-

基于浮栅晶体管(Floating Gate Transistor)存储数据,通过高电压注入电子到浮栅,擦除需通过紫外线照射,通常需移除芯片并使用专用擦除器。

-

-

擦写特性:

-

可重复擦写约 1000 次,擦除后需整片重写(无法按字节操作)。

-

-

典型应用:

-

20 世纪 80-90 年代的计算机 BIOS(如 IBM PC/AT 的 27C512 芯片)。

-

工业设备的固件更新(需定期移除芯片擦写)。

-

已逐步被 EEPROM 和 FLASH 取代,仅用于历史设备维护。

-

-

特点:

-

芯片顶部有透明石英窗口用于紫外线照射,擦写操作繁琐且耗时。

-

3.4.EEPROM(电可擦除可编程只读存储器)

-

工作原理:

-

改进的浮栅晶体管设计,通过电信号(而非紫外线)擦除数据,支持按字节擦写,无需移除芯片,擦除电压通常为 5V 或更低。

-

-

擦写特性:

-

可重复擦写约 1 万-100 万次,擦写速度较慢(约 1 - 10ms/ 字节)。

-

-

典型应用:

-

存储系统配置参数(如计算机 BIOS 设置、打印机墨粉余量)。

-

智能卡(如公交卡、银行卡)中的用户数据。

-

传感器校准数据(如汽车胎压监测系统)。

-

-

特点:

-

读写成本高(擦写耗时),容量通常较小(几 KB 到几 MB),适合小数据频繁更新。

-

3.5.FLASH(闪存)

-

工作原理:

-

基于 EEPROM 技术,但优化为按块擦写(Block Erase)以提高效率。分为两种类型:

-

NOR Flash:支持随机读写,适合代码存储(如 BIOS)。

-

NAND Flash:顺序读写速度快,容量大(如 SSD),但需 FTL(闪存转换层)管理坏块。

-

-

擦写特性:

-

可重复擦写约 10-100万次(MLC/TLC 闪存通过 ECC 提升可靠性),擦写单位为块(Block,通常 4KB-128KB),写入前需先擦除。

-

-

典型应用:

-

NOR Flash:嵌入式系统固件(如路由器、智能手表)。

-

NAND Flash:SSD、U 盘、手机存储(eMMC/UFS)、SD卡。

-

汽车电子(如行车记录仪、车载导航)。

-

-

特点:成本低、容量大、速度快,但存在写入放大(Write Amplification)问题,需优化磨损均衡(Wear Leveling)。

3.6.演进路线

MASK-ROM → PROM(一次性可编程) → EPROM(紫外线擦除) → EEPROM(电擦除按字节) → FLASH(电擦除按块)MASK-ROM → PROM(一次性可编程) → EPROM(紫外线擦除) → EEPROM(电擦除按字节) → FLASH(电擦除按块)

每一代技术通过改进擦写机制和成本控制,推动存储灵活性和容量不断提升

FLASH 作为主流,进一步分化为:

-

NOR Flash:侧重随机访问性能,适合代码执行(如 MCU 的启动代码)。

-

NAND Flash:侧重大容量存储,通过 3D 堆叠技术(如 TLC/QLC)突破容量极限。

4.RAM 芯片示例

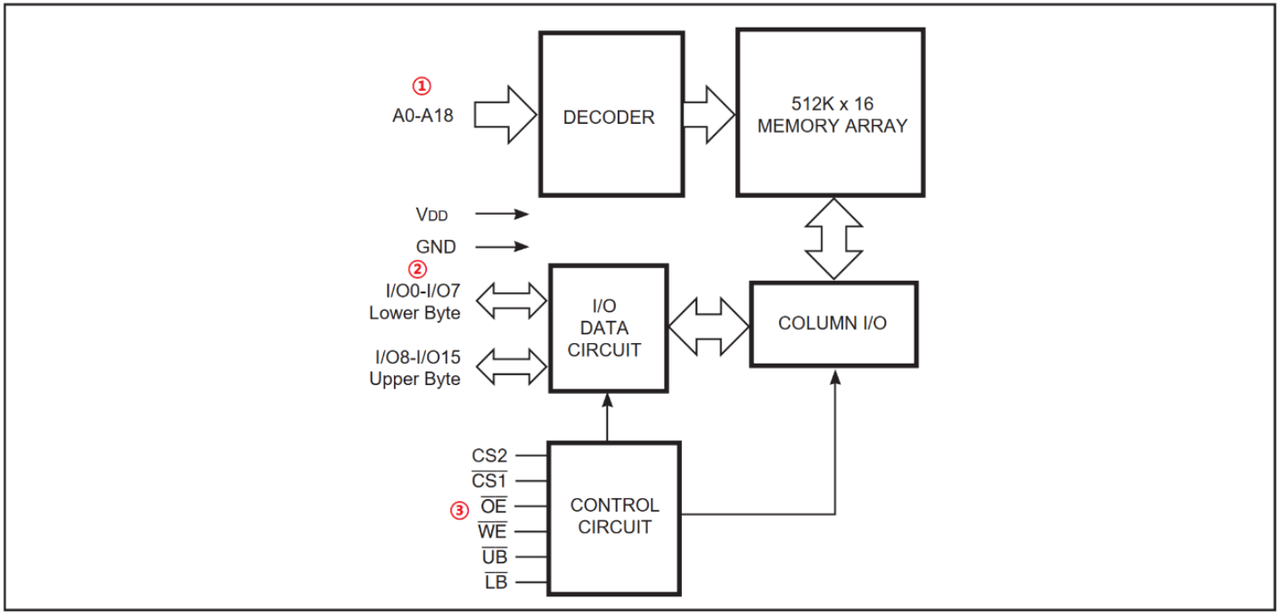

4.1.SRAM - IS62WV51216

SRAM 一般用作 SOC 内部的 RAM 或 Cache,以 STM32F103 开发板上的 IS62WV51216 SRAM 芯片为例,该芯片为 16 位宽(数据位为 16 位)、1MB 大小的 SRAM,芯片框图如下所示:

图中标号部分的作用如下:

-

地址线:

-

A0~A18 共 19 根地址线,因此可访问的地址大小为 2^19 = 524288 = 512KB;

-

IS62WV51216 数据宽度为 16 位,即一次访问 2 个字节,因此要对 512KB 乘 2,即 512KB * 2 = 1MB;

-

位宽可选择 8-bit / 16-bit / 32-bit,一般根据处理器的 SRAM 控制器位宽选择 SRAM 的位宽;

-

-

数据线:

-

数据线的数量根据 SRAM 位宽而定,例如,8-bit 位宽需要 8 根数据线,16-bit 位宽需要 16 根数据线等等,IS62WV51216 为 16-bit 位宽的 SRAM,因此有 16 根数据线,一次可访问 16bit 的数据,即 2 个字节,因此存在高字节和低字节数据之分,其中 IO0~IO7 为低字节数据,IO8~IO15 为高字节数据;

-

-

控制线:

-

CS2 和 CS1 为片选信号,低电平有效,一个系统中可能有多片 SRAM(为了扩展 SRAM 的大小或位宽),此时就需要 CS 信号选择当前使用哪片 SRAM,另外,有的 SRAM 内部其实是由两片 SRAM 拼接而成,因此就会提供两个片选信号;

-

OE 为输出使能信号,低电平有效,即主控从 SRAM 中读取数据;

-

WE 为写使能信号,低电平有效,即主控向 SRAM 写数据;

-

UB 和 LB 信号,IS62WV51216 为 16-bit 位宽的 SRAM,数据分为高字节和低字节,这两根控制线都是低电平有效,UB 为低电平时表示访问高字节,LB 为低电平时表示访问低字节;

-

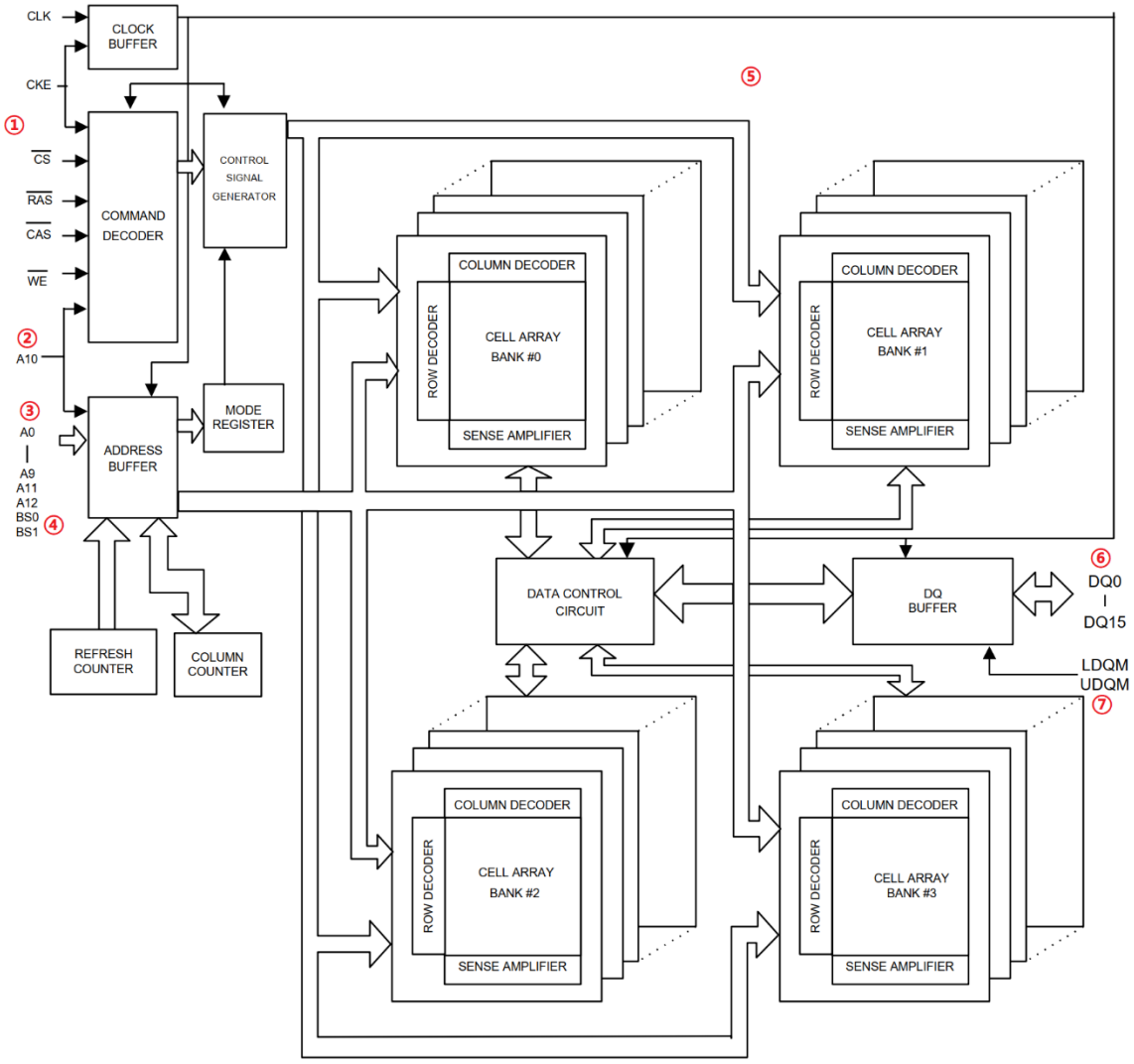

4.2.SDRAM - W9825G6KH

与 SRAM 相比,SDRAM 集成度高、功耗低、成本低、适合做大容量存储,但需要定时刷新来保证数据不会丢失,因此 SDRAM 一般用于内存条

SDRAM 目前已经发展到了第五代,分别为:SDRAM、DDR-SDRAM、DDR2-SDRAM、DDR3-SDRAM、DDR4-SDRAM、DDR5-SDRAM

W9825G6KH 是一款 16-bit 位宽(数据位宽度为 16-bit)、32MB 的 SDRAM,速度一般为 133MHz、166MHz 或 200MHz,W9825G6KH 芯片的结构框图如下图所示:

图中标号部分的作用如下:

-

控制线:

-

CLK:时钟线,SDRAM 为同步动态随机存储器,同步的意思是时钟同步,因此需要一根额外的时钟线,而SRAM 没有时钟线;

-

CKE:时钟使能信号线,SRAM 没有 CKE 信号;

-

CS:片选信号,和 SRAM 一样,都有片选信号;

-

RAS:行选通信号,低电平有效,表示将要发送行地址,SDRAM 和 SRAM 的寻址方式不同,SDRAM 按照行、 列确定某个具体的存储区域,因此有行地址和列地址之分,行地址和列地址共同复用同一组地址线,要访问某一个地址区域,必须要发送行地址和列地址,指定要访问哪一行、哪一列;

-

CAS:列选通信号,表示要发送列地址;

-

WE:写使能信号,低电平有效;

-

-

A10 地址线:

-

在所有地址线中,A10 地址线还有另外一个作用:控制 Auto-precharge,即预充电时间,SDRAM 芯片内部会分为多个 BANK,SDRAM 读写完成后,如果要对同一个 BANK 中的另一行进行寻址操作,就必须将原来有效的行关闭,然后发送新的行/列地址,关闭现在工作的行,准备打开新行的操作就成为预充电,一般 SDSRAM 都支持自动预充电的功能;

-

-

地址线:

-

W9825G6KH 有 A0~A12 共 13 根地址线,这 13 根地址线中包含行地址和列地址,不同的 SDRAM 芯片,根据位宽、容量等不同,行列地址数量不同,W9825G6KH 芯片的 A0~A8 为列地址,共 9 位,A0~A12 为行地址,共 13 位,因此可寻址范围为 2^9*2^13 = 4194304B = 4MB,W9825G6KH 的数据宽度为 16-bit(2 个字节),因此要对 4MB * 2,得到 4*2 = 8MB,8MB 为一个 BANK 的容量,W9825G6KH 共有 4 个 BANK,因此总容量为 32MB;

-

-

BANK 选择线:

-

BS0 和 BS1 为 BANK 选择信号线,在一片 SDRAM 中因为技术或成本等原因,无法做一个全容量的 BANK,同时,因为 SDRAM 的工作原理,单一的 BANK 会导致严重的寻址冲突,降低内存的访问效率,为此,在一片 SDRAM 中分割出多块 BANK,一般为 2^n 个,如 2、4、8 等,图中标号 ⑤ 的部分为 W9825G6KH 的 4 个 BANK 的示意图,SDRAM 数据手册中会标明 BANK 数量,前面计算出一个 BANK 的大小为 8MB,则四个 BANK 的总容量为 8MB*4 = 32MB,因为有 4 个 BANK,因此在访问时需要告诉 SDRAM,现在需要访问哪个 BANK, BS0 和 BS1 为 BANK 选择信号线,2 根线组成的位可访问 4 个 BANK,如果 BANK 数量为 8 则需要 3 根线(BS0~BS2),SRAM 没有 BANK 选择线;

-

-

BANK 区域:

-

W9825G6KH 的 4 个 BANK 区域;

-

-

数据线:

-

W9825G6KH 为 16-bit 位宽的 SDRAM,因此有 16 根数据线 DQ0~DQ15,位宽不同,数据线的数量不同;

-

-

高低字节选择:

-

W9825G6KH 为 16-bit 的 SDRAM,因此区分低字节数据和高字节数据,LDQM 和 UDQM 分别为低字节和高字节选择信号;

-

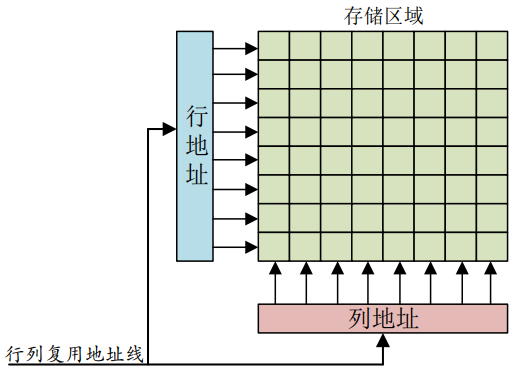

上面的功能描述中,行地址和列地址访问方式如下图所示:

4.3.DDR - NT5CC256M16EP-EK

DDR SDRAM(以下简称 DDR)是 SDRAM 的升级版本,本质上还是 SDRAM,DDR SDRAM 全称 Double Data Rate SDRAM,即双倍速率的 SDRAM

DDR 速率的提升不单单只依靠时钟频率的提升,最为关键的是使用了预取技术 Prefetch

DDR 在一个 CLK 周期传输两次数据,即在时钟信号的上升沿和下降沿各传输一次数据,这个概念称为预取 Prefetch,如果 DDR 预取为 2-bit,则速度翻倍,例如 SDRAM 的速度一般为 133~200MHz,对应的传输速度就是 133~200MT/s(MT/s 为每秒多少兆次数据传输),133MT/S 就是每秒 133M 次数据传输,则频率 133~200MHz 的SDRAM 和 DDR SDRAM,DDR 的传输速度变为 266~400MT/S(这也是 DDR 266、DDR 400 名称的由来)

DDR2 在 DDR 的基础上进一步增加预取值到 4-bit,相当于比 DDR 多读取一倍的数据,因此 DDR2 的数据传输速率为 533~800MT/s(这也是 DDR2 533,DDR2 800 名称的由来)

DDR3 在 DDR2 的基础上将预取值提高至 8-bit,因此在总线时钟频率为 266~400MHz 的情况下,DDR3 的传输速率为 1066~1600MT/S

I.MX6U 的 MMDC 外设用于连接 DDR,支持 LPDDR2、DDR3、DDR3L,最高支持 16-bit 数据位宽,总线速度为 400MHz(实际 396MHz),数据传输速率最大为 800MT/S

LPDDR3、DDR3 和 DDR3L 的区别:

-

LPDDR3 称为低功耗 DDR3,工作电压为 1.2V;

-

DDR3 称为标压 DDR3,工作电压为 1.5V,一般台式机使用标压内存条;

-

DDR3L 为低压 DDR3,工作电压为 1.35V,一般手机、嵌入式、笔记本等使用低压内存条;

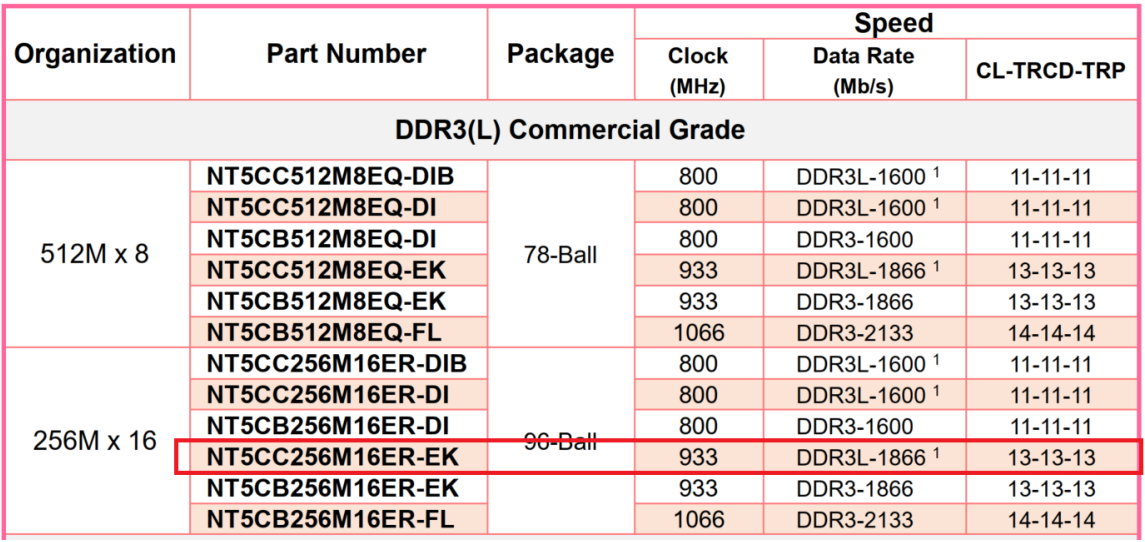

正点原子 I.MX6U-ALPHA 开发板上使用 256MB/512MB 的 DDR3L,16-bit 位宽,型号为 NT5CC128M16JR/MT5CC256M16EP,分为对应 256MB 和 512MB,EMMC 核心板使用的是 512MB 的 DDR3L,NAND 核心板使用的是 256MB 的 DDR3L

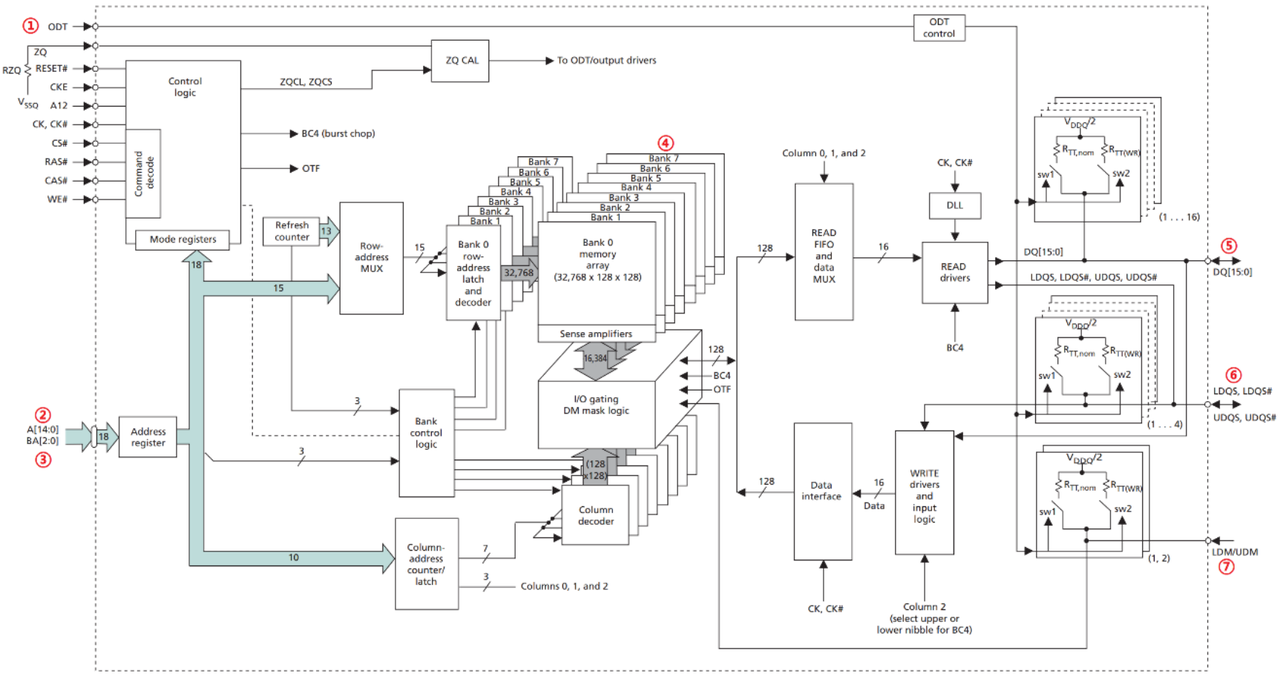

以 EMMC 核心板使用的 NT5CC256M16EP-EK 为例讲解 DDR3,其结构如下图所示:

其中标号部分的作用如下:

-

控制线:

-

ODT:片上终端使能,ODT 使能和禁止片内终端电阻;

-

ZQ:输出驱动校准的外部参考引脚,此引脚应该外接一个 240 欧的电阻到 VSSQ,一般直接接地;

-

RESET:复位引脚,低电平有效;

-

CKE:时钟使能引脚;

-

A12:地址引脚,但有另外一个功能,A12 会在 READ 和 WRITE 命令期间被采样,以决定 Burst Chop 是否会被执行,因此也称为 BC 引脚;

-

CK 和 CK#:时钟信号,DDR3 的时钟线为差分时钟线,所有控制和地址信号都会在 CK 的上升沿和 CK# 的下降沿交叉处被采集;

-

CS#:片选信号,低电平有效;

-

RAS#、CAS#、WE#:行选通信号、列选通信号和写使能信号;

-

-

地址线:

-

A0~A14 共 15 根地址线,根据 NT5CC256M16ER-EK 的数据手册可知,列地址为 A0~A9,共 10 根,行地址为 A0~A14,共 15 根,因此一个 BANK 的大小为 2^10*2^15*2 = 32MB*2 = 64MB,共有 8 个 BANK,因此 DDR3L 的容量为 64*8 = 512MB;

-

-

BANK 选择线 :

-

一片 DDR3 有 8 个 BANK,因此需要 3 根线才能实现 8 个 BANK 的选择,BA0~BA2 用于 BANK 选择;

-

-

BANK 区域:

-

DDR3 一般拥有 8 个 BANK 区域;

-

-

数据线:

-

DQ0~DQ15 共 16 根数据线(数据宽度为 16-bit);

-

-

数据选通:

-

DQS 和 DQS#:数据选通引脚(差分信号),读的时候为输出,写的时候为输入;

-

LDQS(有的称为 DQSL)和 LDQS#(有的称为 DQSL#)对应低字节,即 DQ0~DQ7,UDQS(有的称为 DQSU)和 UDQS#(有的称为 DQSU#)对应高字节,即 DQ8~DQ15;

-

-

数据输入屏蔽:

-

DM 为写数据输入屏蔽引脚;

-

5.DDR3 关键时间参数

5.1.传输速率

如 1066MT/S、1600MT/S、1866MT/S 等,该参数首要考虑,决定了 DDR3 内存的最高传输速率

5.2.tCL

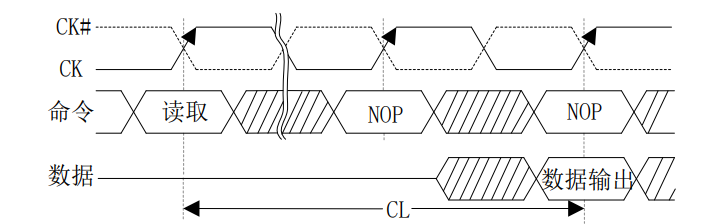

CAS Lantency Control (CL):内存读写操作前,列地址控制器的潜伏时间,单位为 tCK(单位时钟周期)

列地址信号发出后会触发数据传输,但数据从存储单元到内存芯片的 IO 接口还需要一段时间,这段时间称为列地址选通潜伏时间 CL,如下图所示:

CAS 控制从接受一个指令到指令执行之间的时间,对内存读写性能影响大

CAS 主要控制十六进制的地址(内存矩阵中的列地址),在保持稳定的前提下应尽可能设低

计算公式:tCL(ns) = (CL * 2000) / 内存频率,如:DDR3-1333-CL9,则其 tCAS = (9 * 2000) / 1333 = 13.5(ns)

NT5CC256M16EP-EK 的 CL 值为 13 个时钟周期,一般 tRCD 和 CL 大小一样

5.3.tRCD

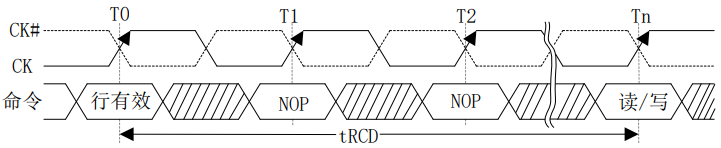

tRCD 全称 RAS-to-CAS Delay,即行寻址到列寻址之间的延迟

DDR 的寻址流程是先指定 BANK 地址,再指定行地址,然后指定列地址,最终确定要寻址的单元

BANK 地址确认信号和行地址确认信号同时发出,该命令称为行激活 Row Active,行激活后发送列地址和具体的操作命令(Read or Write),这两个信号同时发出,因此一般也用读/写命令表示列寻址,在行有效(行激活)命令到读写命令发出的这段时间间隔称为 tRCD,如下图所示:

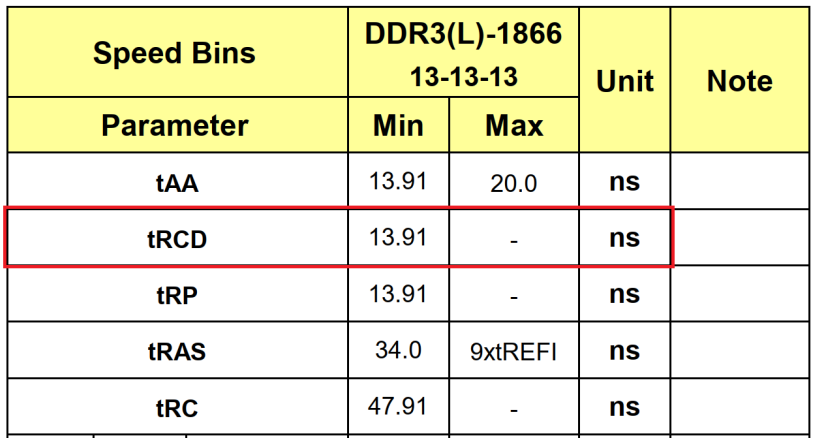

开发板使用的 NT5CC256M16EP-EK,其 tRCD 参数如下图所示:

从图中可以看出,tRCD 为 13.91ns,初始化 DDR3 时需要配置

5.4.tRP

Row Precharge Timing (tRP) 又称为 Precharge to Active,其为内存行地址控制器预充电时间,单位为 tCK(单位时间周期)

tRP 设定在另一行可以被激活前 RAS 需要的充电时间,tRP 时间太长会导致所有的行激活延迟,设置太短可能会导致行激活之前的数据丢失,从而导致内存控制器不能顺利地完成读写操作

5.5.tCL-tRCD-tRP

该参数即为常用于评估内存性能的时序,NT5CC256M16ER-EK 的时序为 13-13-13:

图中的 13 不是 ns 数,而是 CLK 时间数,表示 13 个 CLK 周期

5.5.tAL

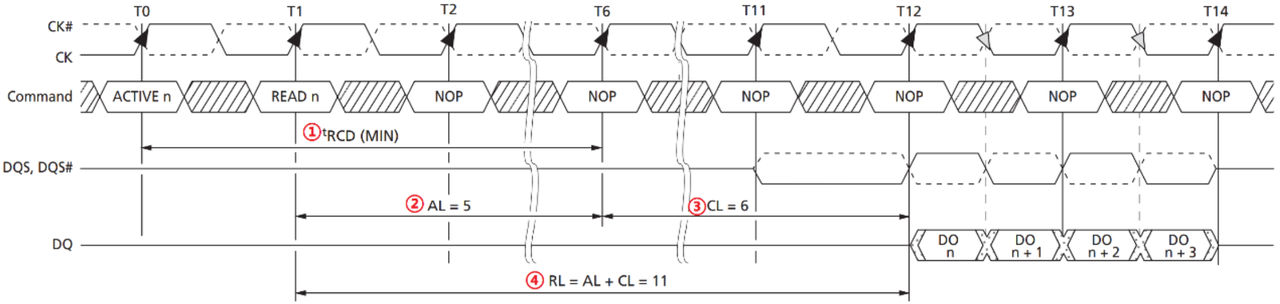

DDR 的发展中,提出了前置 CAS 的概念,目的是为了解决 DDR 中的指令冲突

前置 CAS 允许 CAS 信号紧随 RAS 发送,相当于将 DDR 中的 CAS 前置,但读/写操作并没有因此提前,依旧要保证足够的延迟/潜伏期,为此引入了 AL (Additive Latency) 参数,单位为时钟周期数,AL + CL 组成 RL (Read Latency)

从 DDR2 开始引入了写潜伏期 WL (Write Latency),WL 表示写命令发出后到第一笔数据写入的潜伏期,引入 AL 后的读时序如图所示:

5.6.tRC

tRC 是两个 ACTIVE 命令或 ACTIVE 命令到 REFRESH 命令间的周期,NT5CC256M16EP-EK 的 tRC 值为 47.91ns

5.7.tRAS

tRAS 是 ACTIVE 命令到 PRECHARGE 命令之间的最小时间,NT5CC256M16EP-EK 的 tRAS 值为 34ns

6.I.MX6U MMDC 控制器简介

MMDC(Multi Mode DDR Controller)为 I.MX6U 的内存控制器,它是一个多模的 DDR 控制器,可以连接 16-bit 位宽的 DDR3/DDR3L 或 16-bit 位宽的 LPDDR2

MMDC 外设包含内核(MMDC_CORE)和 PHY(MMDC_PHY)两部分,内核和 PHY 的功能如下:

-

MMDC_CORE:通过 AXI 接口与系统进行通信、DDR 命令生成、DDR 命令优化、设置读/写数据路径;

-

MMDC_PHY:负责时序调整和校准,使用特殊的校准机制以保障数据能被准确捕获;

MMDC 的主要特性如下:

-

支持 DDR3/DDR3L x16、支持 LPDDR2 x16,不支持 LPDDR1、MDDR 和 DDR2;

-

支持单片 256Mbit~8Gbit 容量的 DDR,列地址范围为 8-12 位,行地址范围为 11-16bit,2 个片选信号;

-

对于 DDR3,最大支持 8-bit 的突发访问;

-

对于 LPDDR2,最大支持 4-bit 的突发访问;

-

MMDC 最大输出频率为 400MHz,因此对应的数据速率为 800MT/s;

-

支持各种校准程序,可自动或手动运行,支持 ZQ 校准外部 DDR 设备,ZQ 校准 DDR I/O 引脚 以及 校准 DDR 驱动的能力;

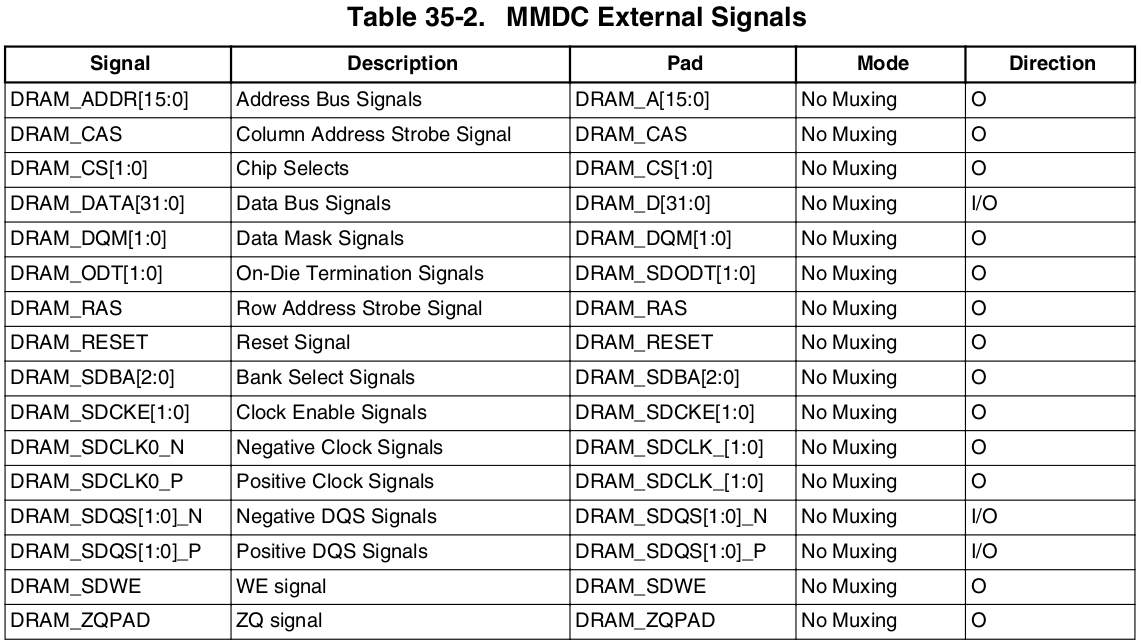

6.1.信号/引脚

因为 DDR 对硬件要求非常严格,因此 DDR 的引脚均为独立引脚,没有复用功能,I.MX6U 的 DDR 引脚(手册中称为信号)如下图所示:

注意:设置 DDR 引脚电气特性所使用的寄存器,和设置普通外设引脚电气特性的寄存器不同

6.2.时钟源

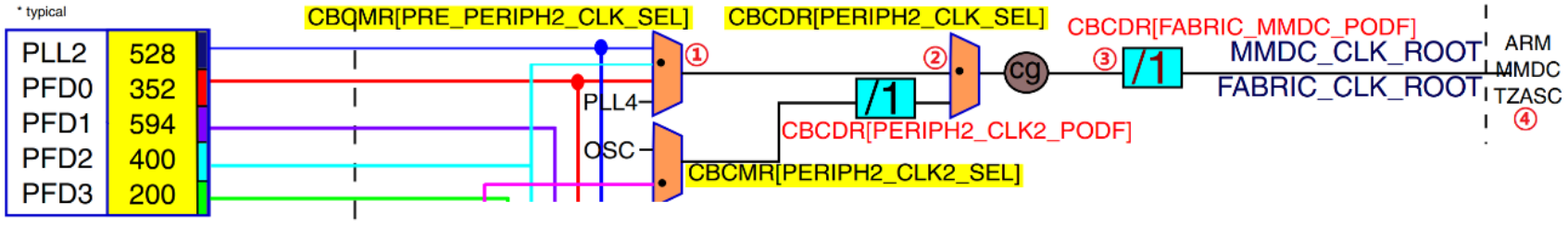

DDR 的时钟树节点如下图所示:

其重要分为四个部分,每个部分的作用如下:

-

时钟源选择器 1:CBCMR.PRE_PERIPH2_CLK_SEL[22:21] 配置 pre_periph2 的时钟源:

-

0b00:PLL2;

-

0b01:PLL2 PFD2;

-

0b10:PLL2 PFD0

-

0b11:PLL4;

-

I.MX6U 内部 boot rom 设置 PLL2_PFD2 作为 MMDC 的时钟源,因此 I.MX6U 的 DDR 频率为 400MHz;

-

-

时钟源选择器 2:CBCDR.PERIPH2_CLK_SEL[26] 配置 pre_periph2 的时钟源,为 0 时选择 pll2_main_clk 作为 periph2_clk 的时钟源,为 1 时选择 periph2_clk2_clk 作为 periph2_clk 的时钟源,将 PERIPH2_CLK_SEL 设置为 0,即选择 pll2_main_clk 作为 periph2_clk 的时钟源,因此 periph2_clk = PLL2_PFD0 = 396MHz;

-

分频器:CBCDR.FABRIC_MMDC_PODF[5:3] 设置分频系数,可设置 0~7,分别对应 1~8 分频,要配置 MMDC 的时钟源为 396MHz,则应该设置为 1 分频,因此 FABRIC_MMDC_PODF = 0;

6.3.注意事项

使用 USB 启动时,将拨码器设置为 USB 启动后,一定要将 SD 从开发板上拔出,否则电脑无法识别到设备

958

958

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?