目录

System Generator是一个Xilinx公司的工具,用于设计数字信号处理系统。Black Box是System Generator中的一个block,可以将其他HDL文件以黑盒的形式封装到System Generator设计中,在仿真时使用Simulink+Vivado Simulator(或ModelSim)协同仿真的方法,在Simulink环境中完成设计的仿真测试,即使用verilog代码进行编写,并在system generator中完成调用。参考:[R1],[R2]

下面开始实际操作演示~

1. 实际操作流程

1.1 Verilog 代码编写

简单编写一个通过计数器timer_cnt来控制4个LED灯的亮灭

module led(

input clk ,

input rst_n ,

input ce ,//使用Block box时,时钟clk和时钟使能ce是必须要包含的,同时命名要满足规范

output reg[3:0] led //四个LED灯

);

reg[31:0] timer_cnt;

always@ (posedge clk or negedge rst_n)

begin

if(!rst_n)//复位:初始化

begin

led <= 4'd0;

timer_cnt <= 32'd0;

end

else if(timer_cnt >= 32'd49) //每过50个clk周期

begin

led <= led + 4'd1; //每过50个时钟周期,LED灯依此亮灭(LED亮灭频率由timer_cnt决定)

timer_cnt <= 32'd0;//计数器清零

end

else

begin

led <= led;

timer_cnt <= timer_cnt + 32'd1;//计数过程

end

end

endmodule1.2 system generator操作

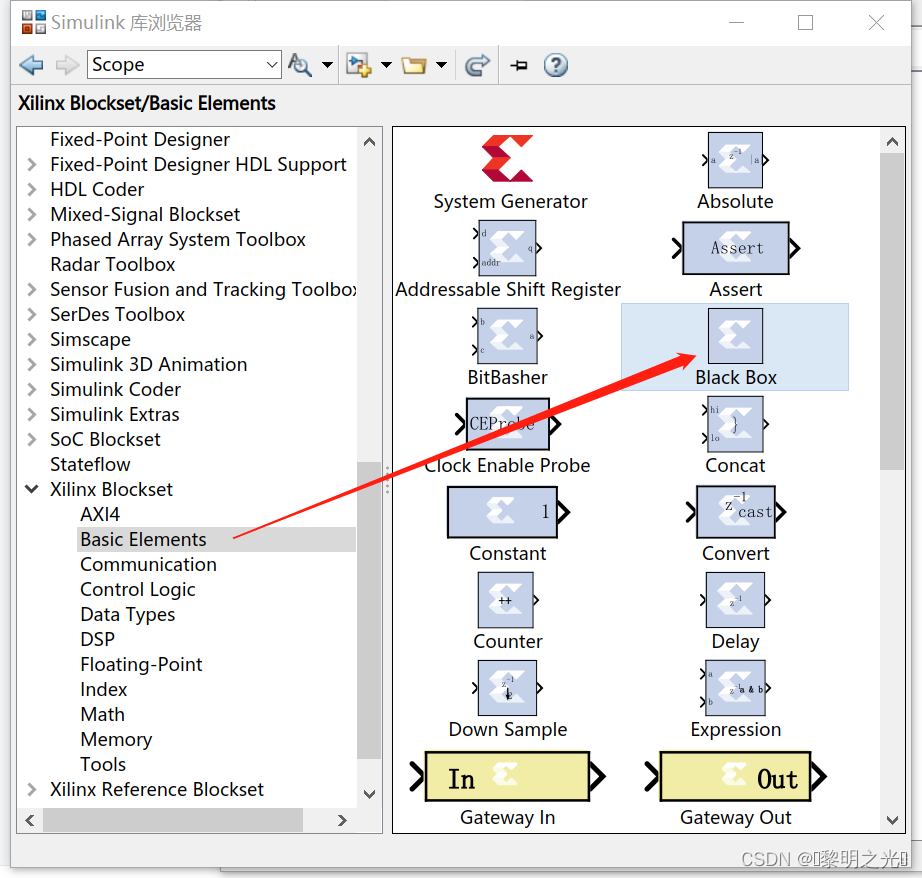

1.2.1 Black box模块

通过system generator打开matlab,并打开simulink界面,首先将空白模型保存,我的保存路径为:

E:\FPGA\FPGA_DSP\Black_box\simulink\blackbox_demo.slx然后在空白模型中调用black box模块

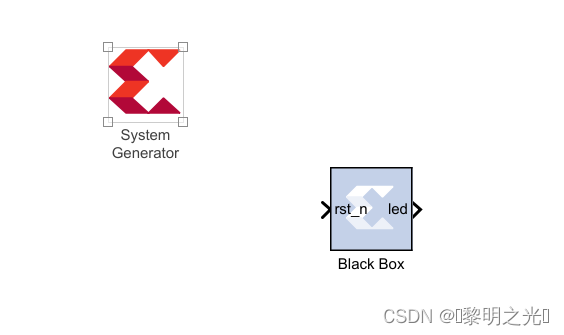

并在该模块中添加我们的led.v代码,如下图所示,输入仅为rst_n和led引脚,clk和ce引脚没有显示

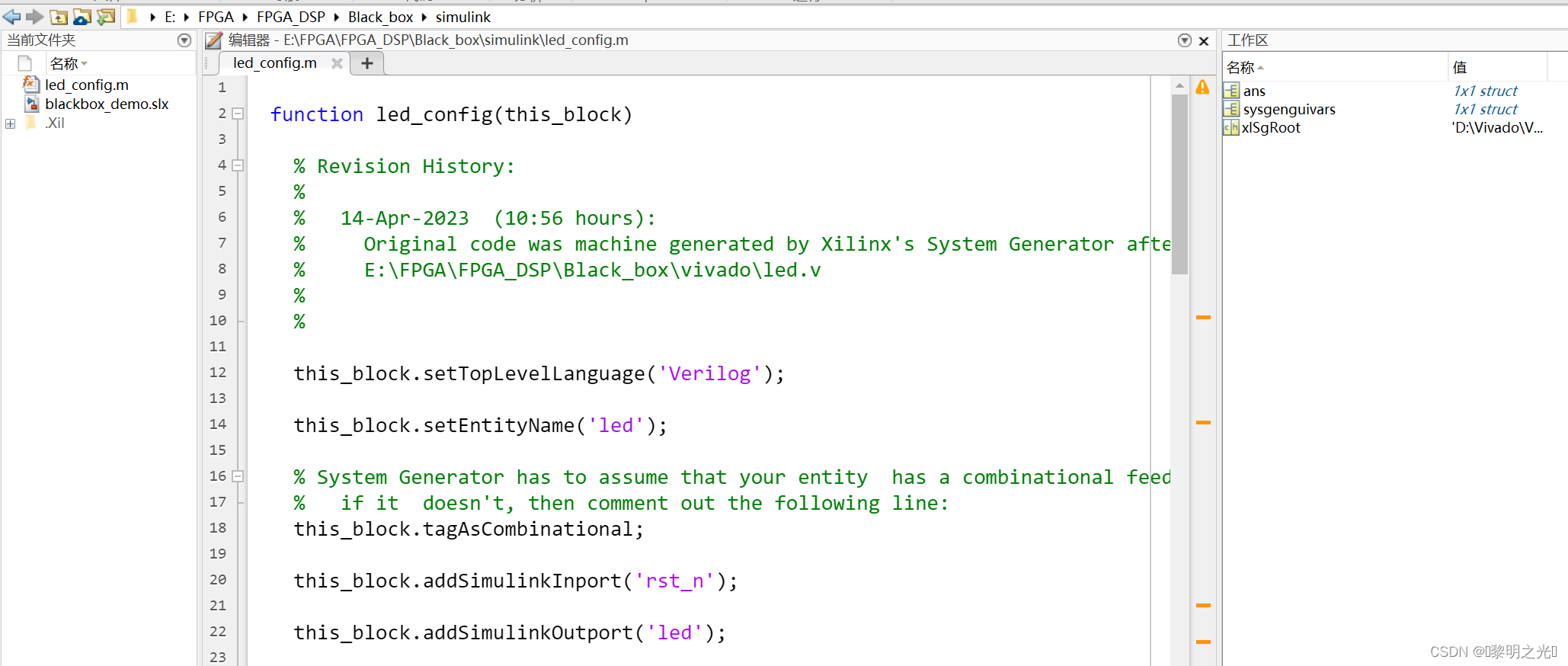

当我们添加好代码之后,可以看到在matlab中会自动生成对应的config配置文件

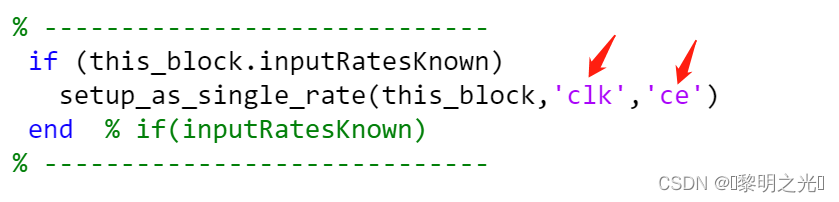

在该配置文件中,clk和ce被特别声明,引脚被隐藏,在内部已经被链接,这就是为什么在simulink的black box模块中没有显示的原因

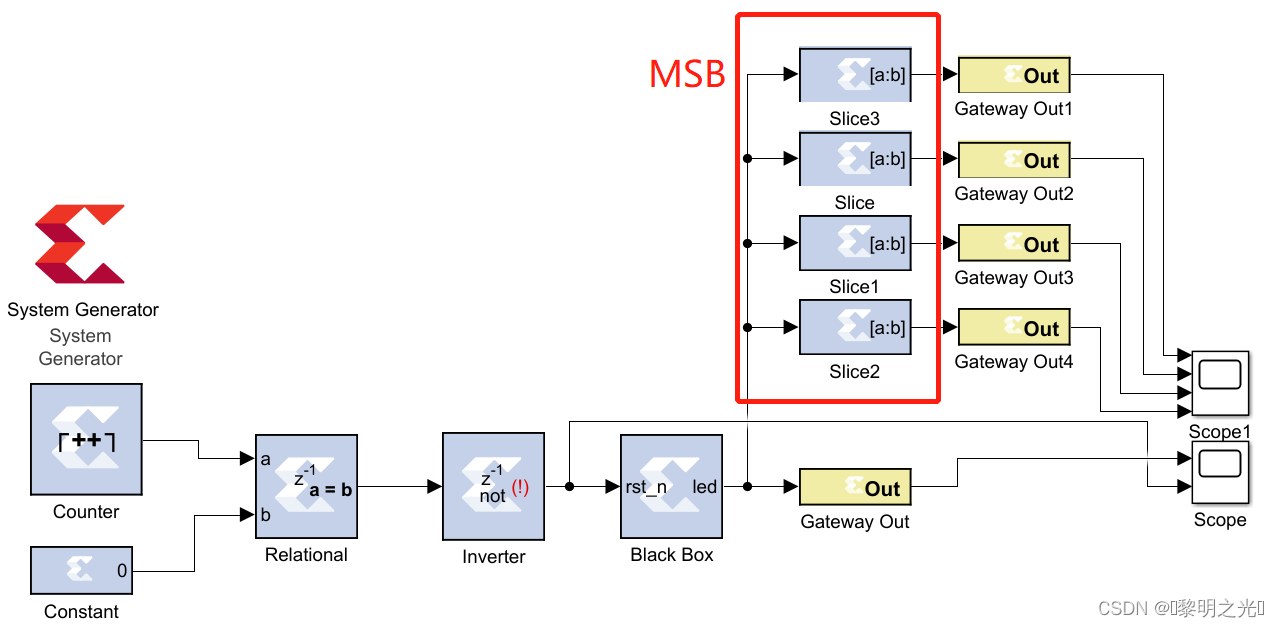

接下来开始我们的simulink模块搭建

1.2.2 Simulink 搭建

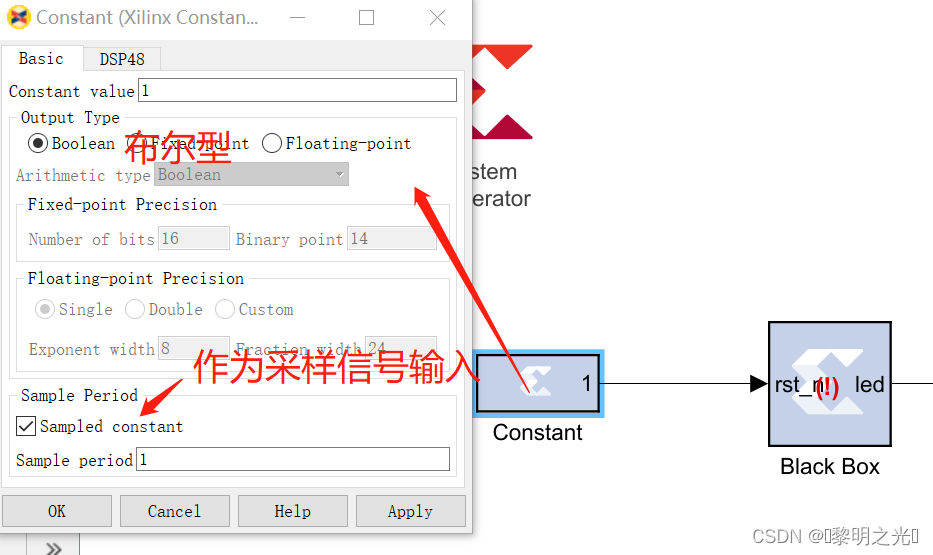

- rst_n输入

由于rst_n输出只有0、1两种(真假),因此用布尔型表示

- led输出

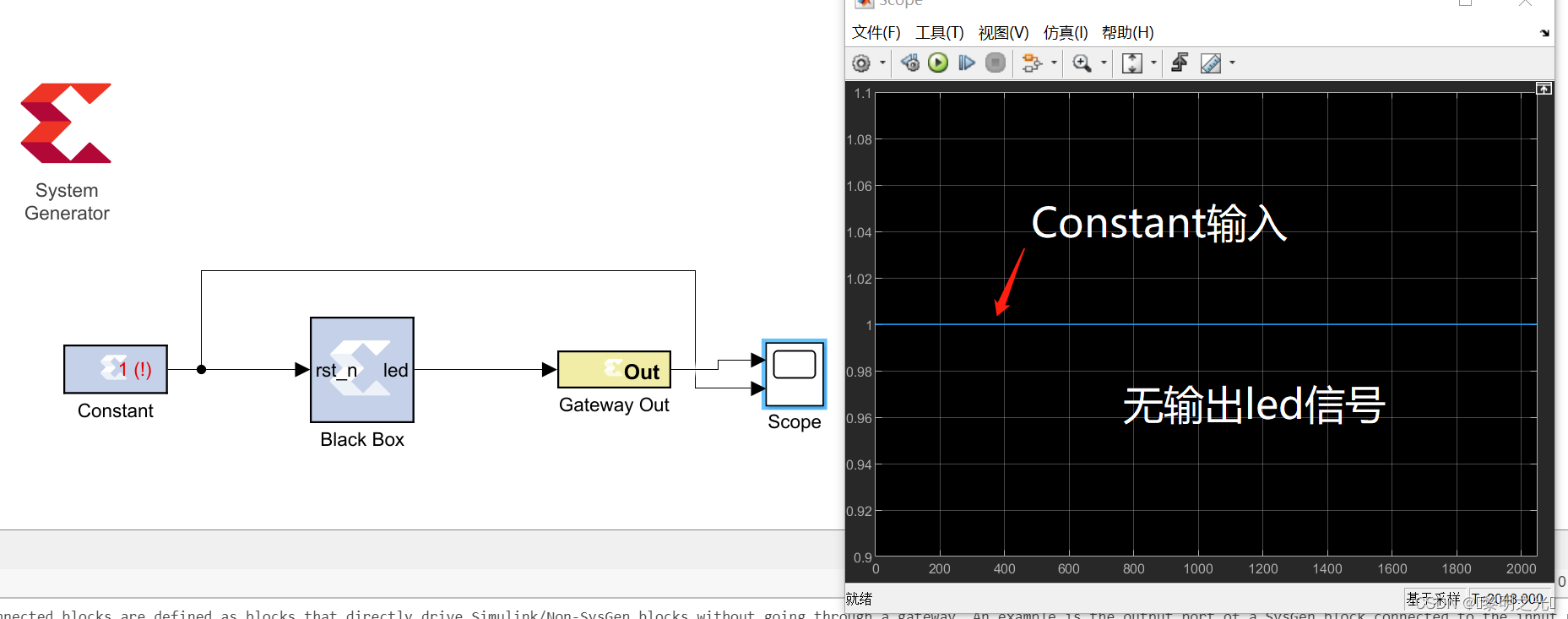

注意:我们基于上图直接运行的话,示波器是没有任何显示的。原因是因为在开始运行的时候并未进行初始化,没有初始化寄存器,即没有进行复位操作,led寄存器就会没有输出

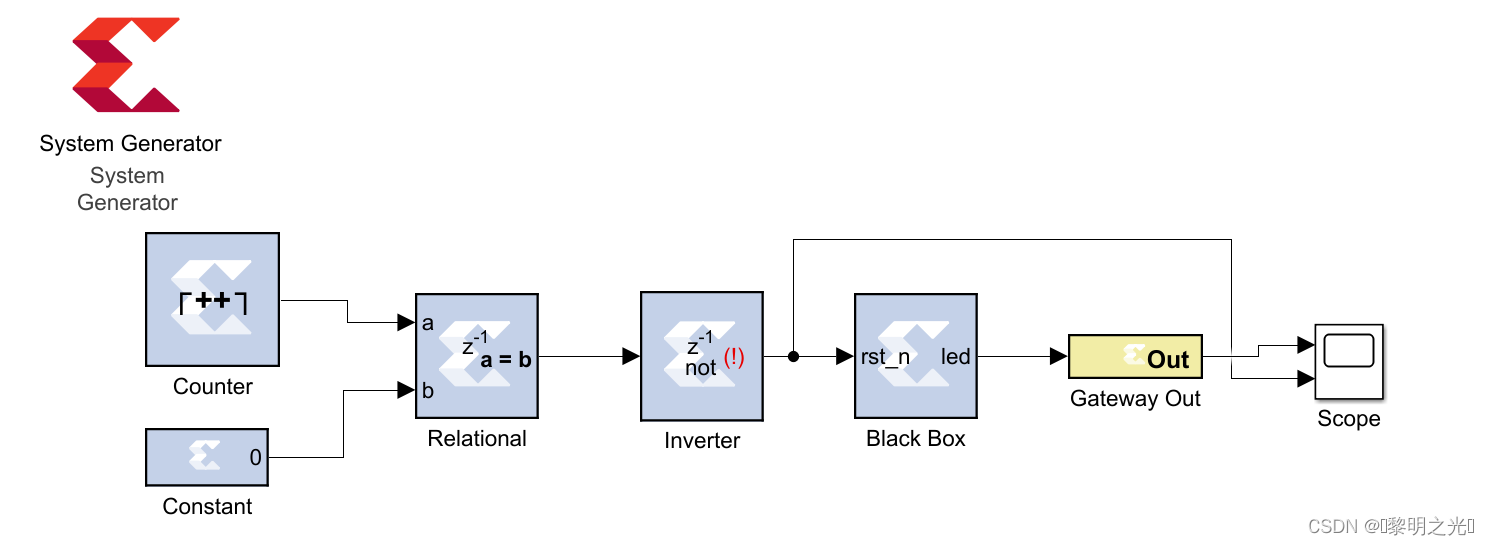

- 复位信号设置

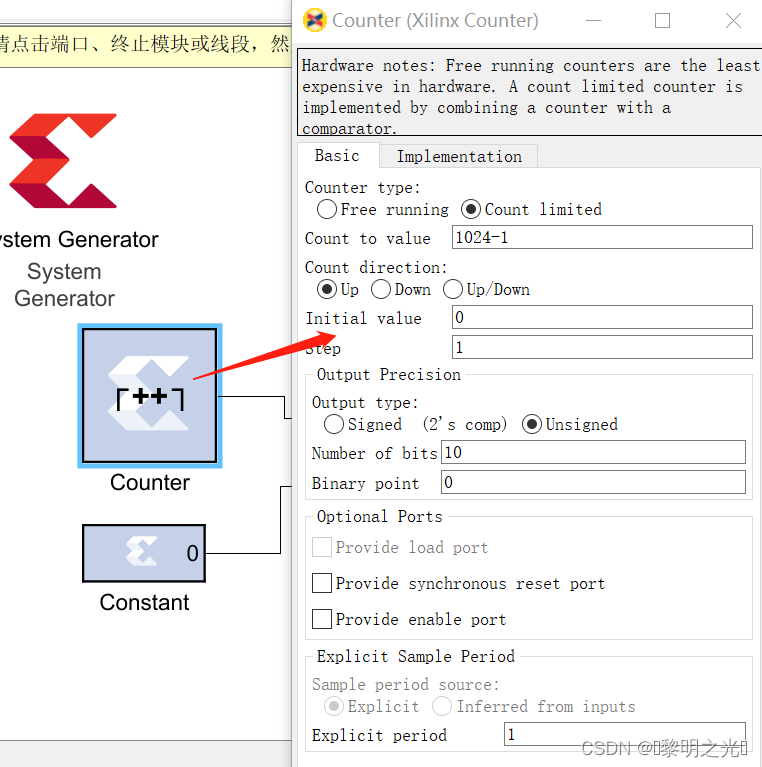

通过将计数器,比较器,常数模块相结合来构造复位信号

| 计数器 | 常数模块 |

|  |

模型构建分析:计数器从0~1023,一共1024个时钟周期归零一次,常数模块恒定为0,通过比较器将二者相比较,当计数器与常数模块相等(Counter=Constant=0)时,比较器模块输出为1(真),然而计数器每过1024个时钟周期归0一次,因此每隔1024个时钟周期比较器输出1,其余均输出0,然而blackbox模块为低电平复位,因此我们将比较器的输出取反,即可实现每隔1024个时钟周期复位一次。

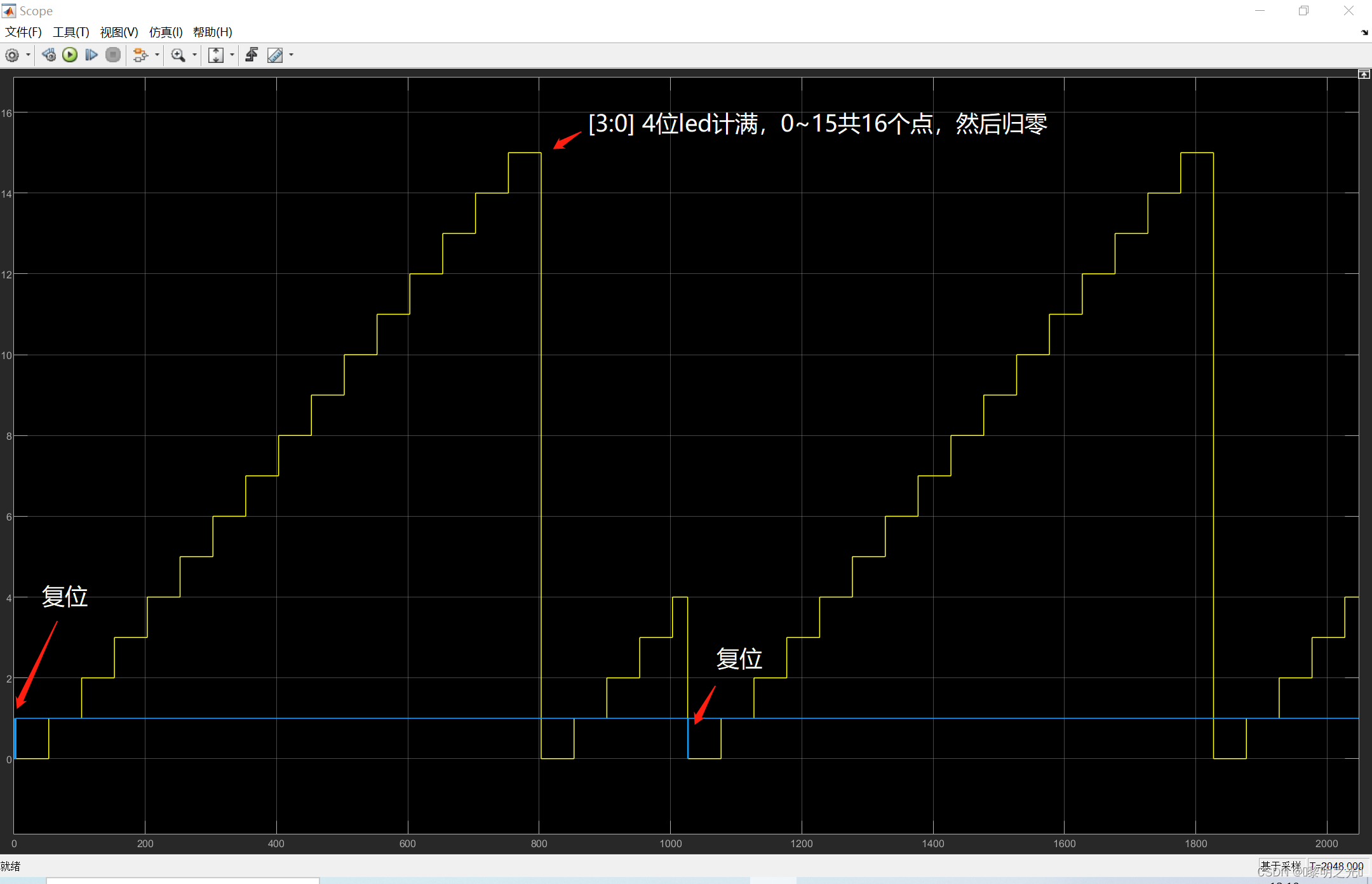

结果如下图所示:

从上图可以看出示波器现实的led输出结果并不是我们期望的看到的结果,虽然上图现实的结果是正确的,但是不能与实际led的亮灭相对应,因此下面将使用一个额外模块来将输出结果与我们的led实际状态相对应

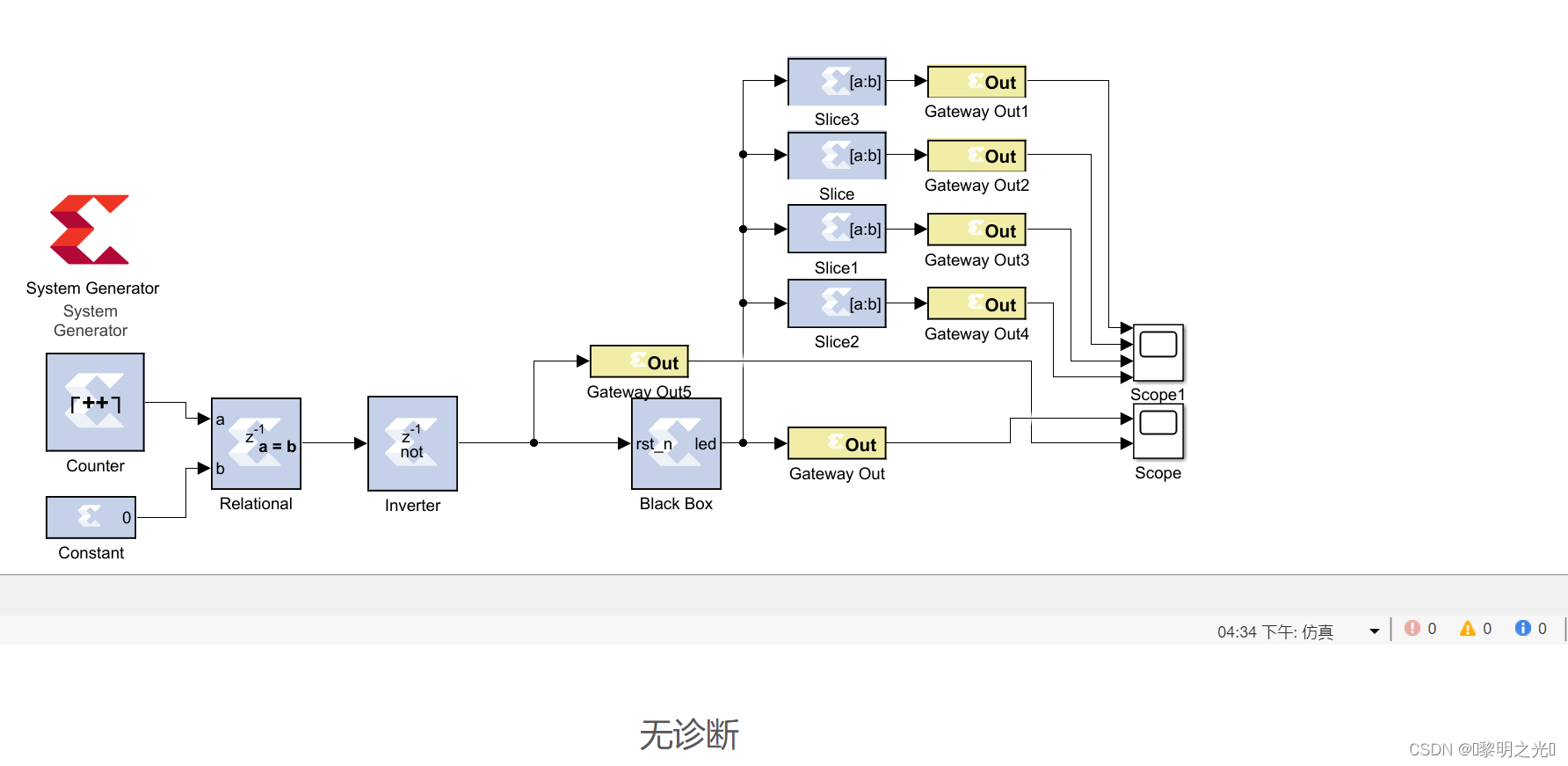

2. Simulink模型优化

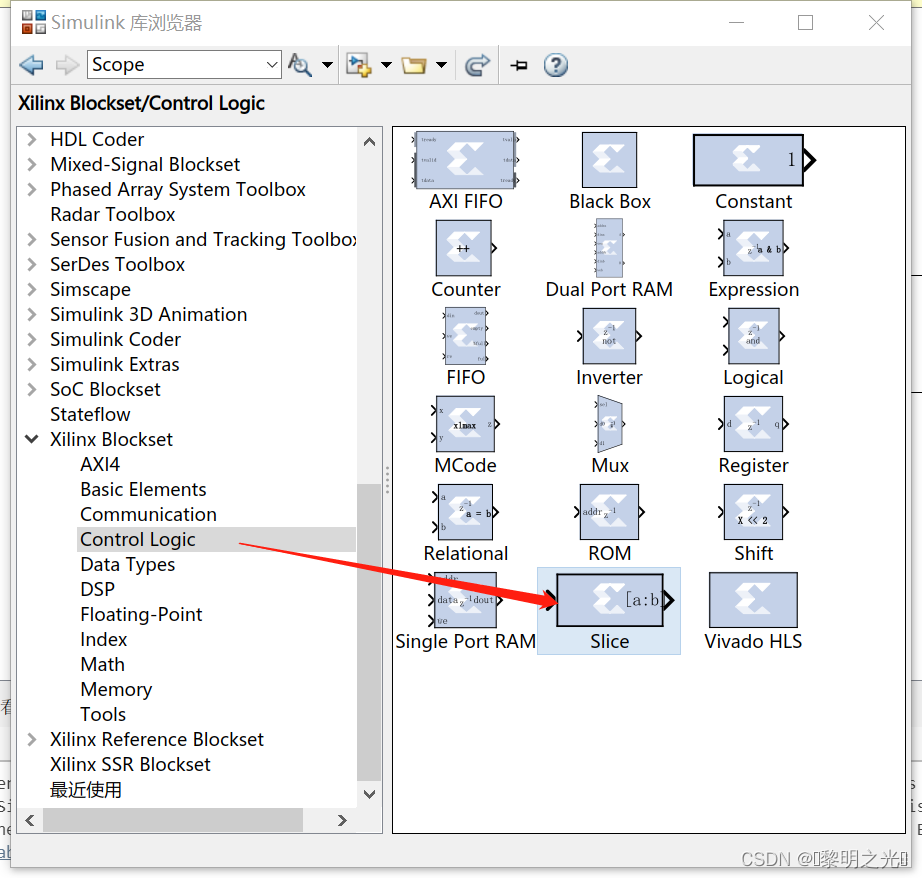

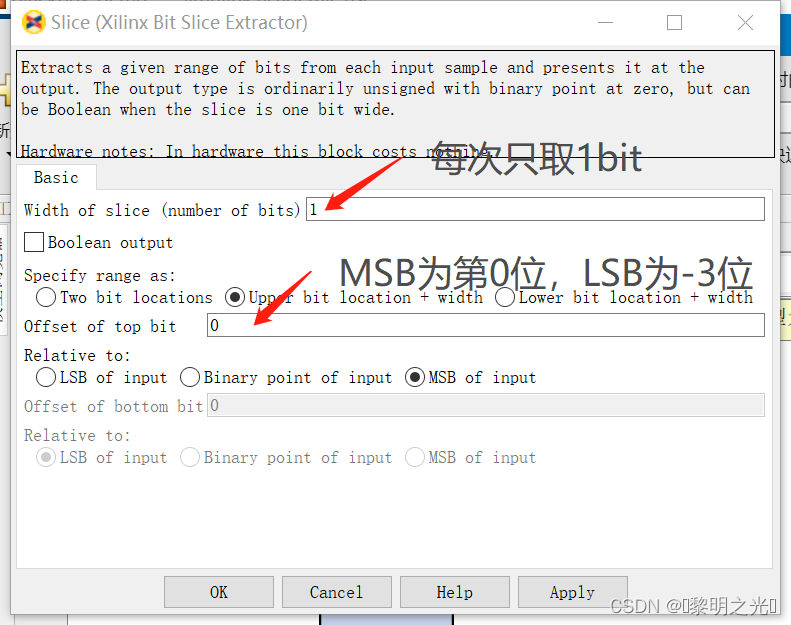

我们知道上述的4位led输出可以表示0~15共16个不同值,如上图结果所示,但是这样不能直观地与led的亮灭相结合,因此我们需要将led的四bit按位输出,每一位就可以表示不同led灯的状态。

| 模块所在位置 | 模块配置 |

|  |

由于我们要依此取出4bit,因此offset of top bit选项需要从0一次填写到-3,其中0代表MSB,-3代表LSB

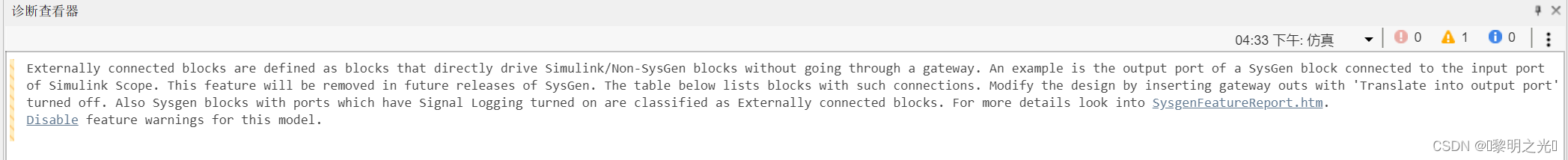

注意:FPGA模块最好不要与simulink中的模块(Scope)直连,需要经过input/output getway将FPGA的数据格式转化为matlab所需格式,从图中可以看出,我们的black box模块输出到matlab的scope时就没有经过output getway因此该模块上面会显示感叹号,Simulink报错如下

意思是:外部连接块定义为不经过网关直接驱动Simulink/非sysgen块的块。例如,SysGen块的输出端口连接到Simulink Scope的输入端口。这个特性将在SysGen的未来版本中被移除。下表列出了具有这种连接的块。修改设计,插入网关,并关闭“转换成输出端口”。同时,带有打开信号记录的端口的Sysgen块被归类为外部连接块。有关更多详细信息,请参阅sysgenfeatuereport .htm。

意思是:外部连接块定义为不经过网关直接驱动Simulink/非sysgen块的块。例如,SysGen块的输出端口连接到Simulink Scope的输入端口。这个特性将在SysGen的未来版本中被移除。下表列出了具有这种连接的块。修改设计,插入网关,并关闭“转换成输出端口”。同时,带有打开信号记录的端口的Sysgen块被归类为外部连接块。有关更多详细信息,请参阅sysgenfeatuereport .htm。

禁用此模型的特性警告。 所以我们需要添加一个output getway即可

添加好之后可以发现再也没有报错了,完美~

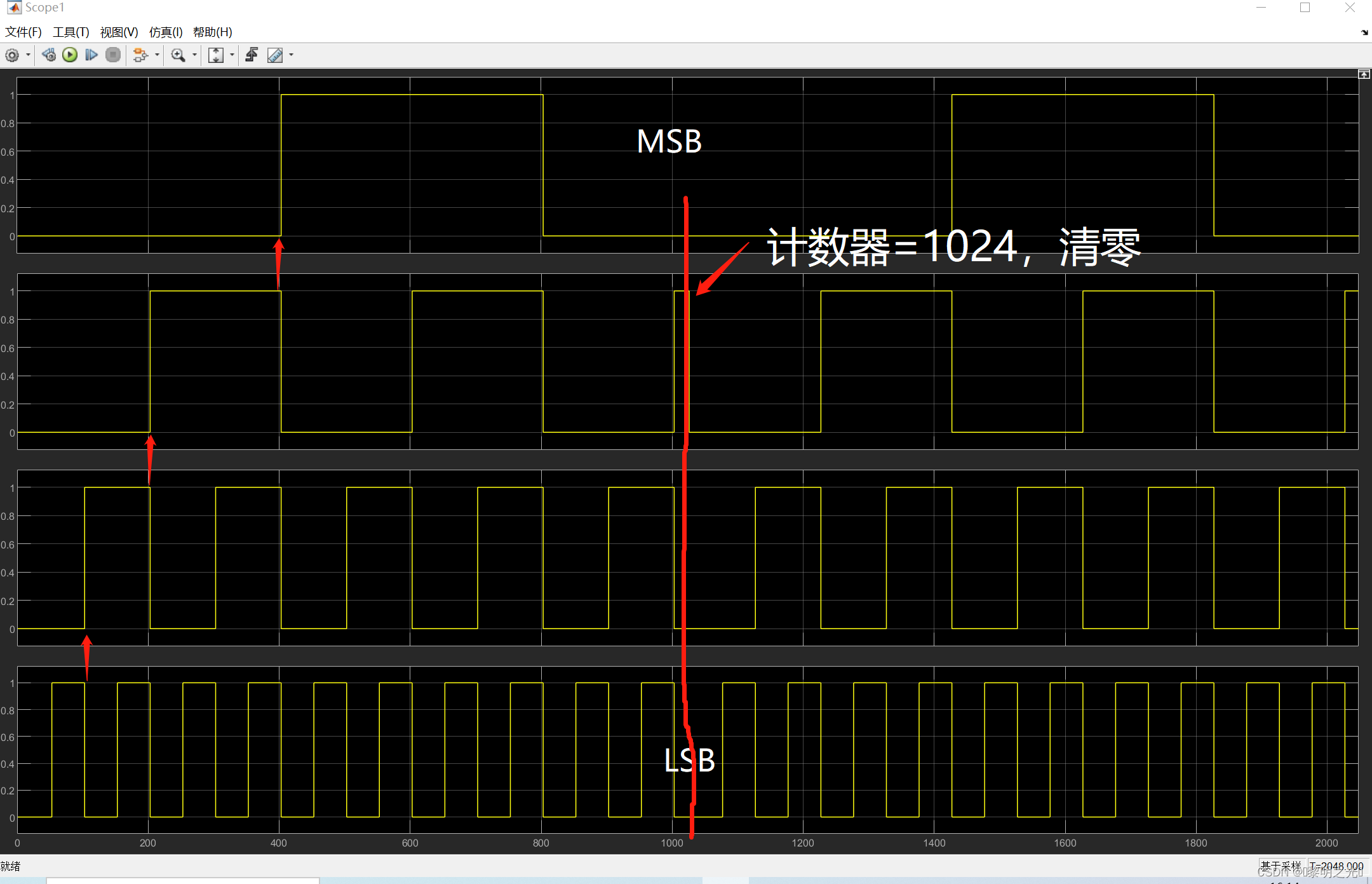

示波器输出结果如下所示:

结果正确! 在1024个采样点处rst_n = 0,清零。

7687

7687

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?