有限状态机

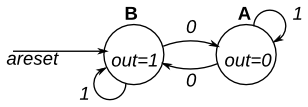

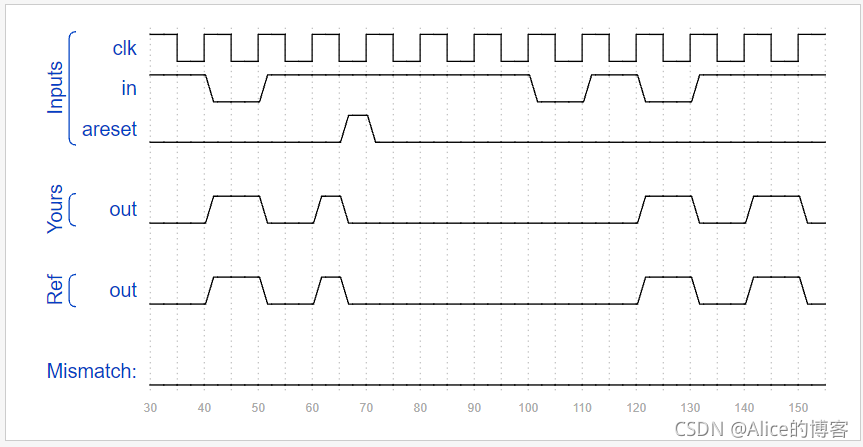

1、简单 FSM1(异步复位)

实现下图所示的摩尔状态机,复位为异步复位。

代码实现:

module top_module(

input clk,

input areset, // Asynchronous reset to state B

input in,

output out);//

parameter A=0, B=1;

reg state, next_state;

always @(*) begin // This is a combinational always block

case(state) // State transition logic

A:begin

if( in == 1'b1 )

next_state <= A;

else

next_state <= B;

end

B:begin

if( in == 1'b1 )

next_state <= B;

else

next_state <= A;

end

endcase

end

always @(posedge clk, posedge areset) begin // This is a sequential always block

if(areset)

state <= B;

else

state <= next_state;// State flip-flops with asynchronous reset

end

// Output logic

assign out = (state == B);

endmodule

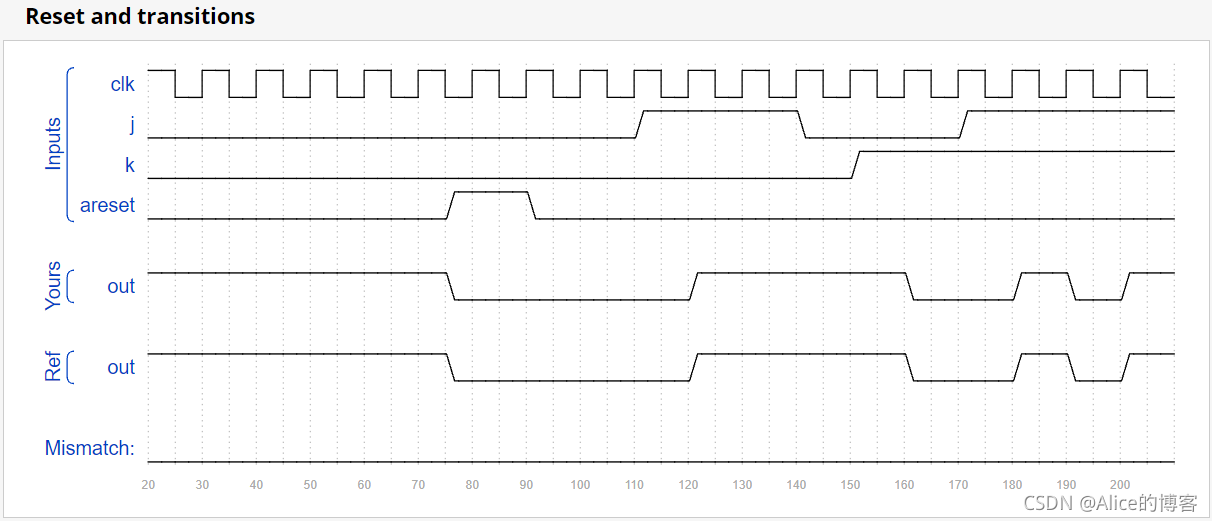

验证结果:

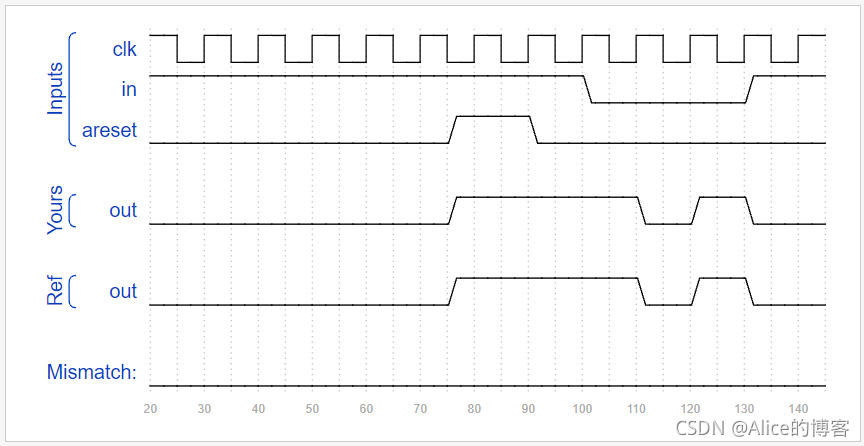

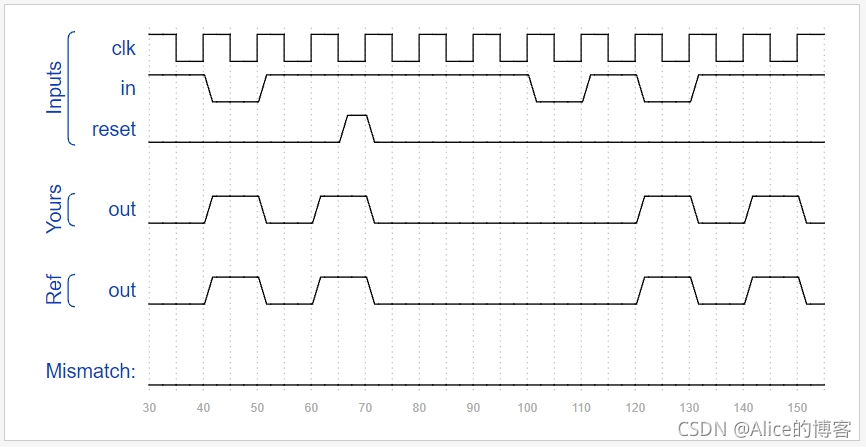

2、简单 FSM1(同步复位)

实现下图所示的摩尔状态机,复位为同步复位。

代码实现:

module top_module(clk, reset, in, out);

input clk;

input reset; // Synchronous reset to state B

input in;

output out;//

reg out;

// Fill in state name declarations

parameter A=0, B=1;

reg state, next_state;

always @(*) begin // This is a combinational always block

case(state) // State transition logic

A:begin

if( in == 1'b1 )

next_state <= A;

else

next_state <= B;

end

B:begin

if( in == 1'b1 )

next_state <= B;

else

next_state <= A;

end

endcase

end

always @(posedge clk) begin // This is a sequential always block

if(reset)

state <= B;

else

state <= next_state;// State flip-flops with asynchronous reset

end

// Output logic

assign out = (state == B);

endmodule

验证结果:

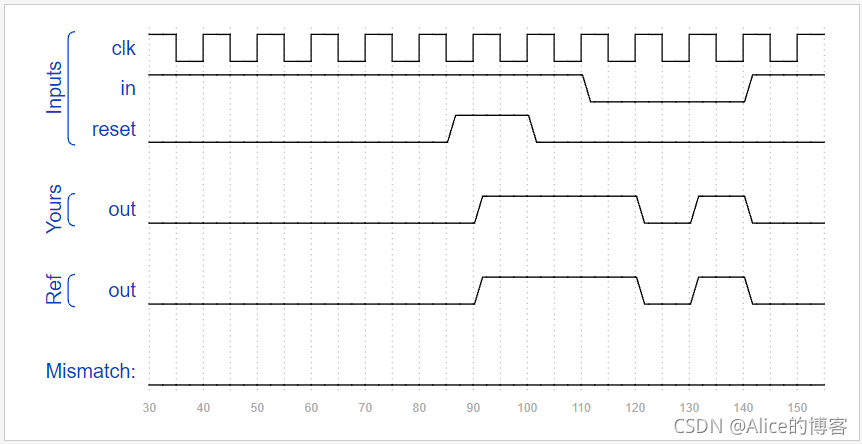

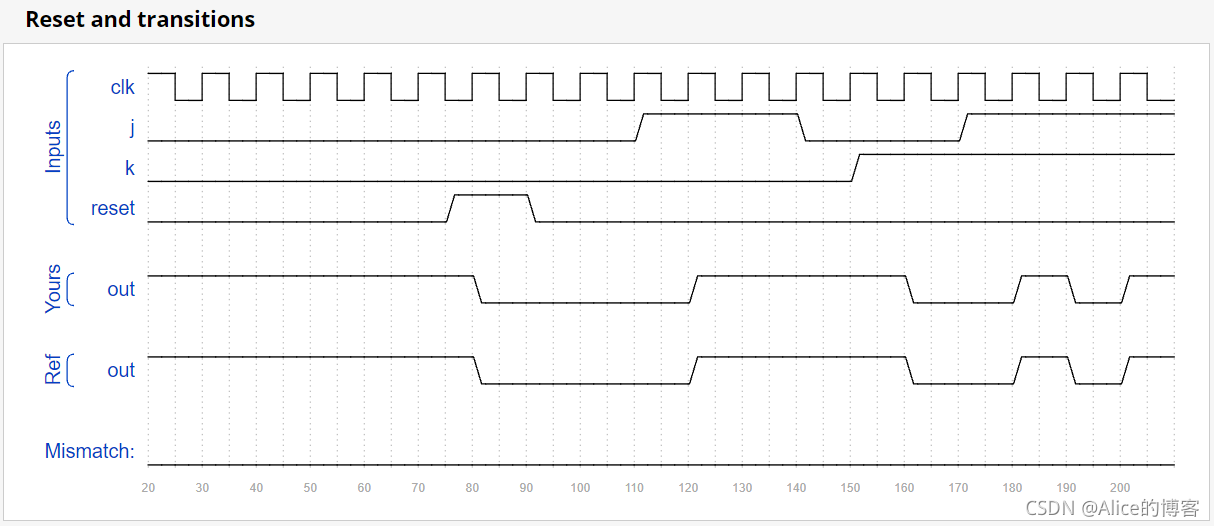

3、简单 FSM2(异步复位)

2个输入1个输出,异步复位状态机,如下图所示。

代码实现:

module top_module(

input clk,

input areset, // Asynchronous reset to OFF

input j,

input k,

output out); //

parameter OFF=0, ON=1;

reg state, next_state;

always @(*) begin

case(state) // State transition logic

OFF:begin

if( j == 1'b1 )

next_state <= ON;

else

next_state <= OFF;

end

ON:begin

if( k == 1'b1 )

next_state <= OFF;

else

next_state <= ON;

end

endcase

end

always @(posedge clk, posedge areset) begin

if(areset)

state <= OFF;

else

state <= next_state;// State flip-flops with asynchronous reset

end

// Output logic

assign out = (state == ON);

endmodule

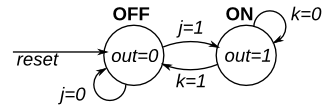

验证结果:

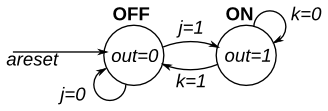

4、简单 FSM2(同步复位)

2个输入1个输出,同步复位状态机,如下图所示。

代码实现:

module top_module(

input clk,

input reset, // Synchronous reset to OFF

input j,

input k,

output out); //

parameter OFF=0, ON=1;

reg state, next_state;

always @(*) begin

case(state) // State transition logic

OFF:begin

if( j == 1'b1 )

next_state <= ON;

else

next_state <= OFF;

end

ON:begin

if( k == 1'b1 )

next_state <= OFF;

else

next_state <= ON;

end

endcase

end

always @(posedge clk) begin

if(reset)

state <= OFF;

else

state <= next_state;// State flip-flops with asynchronous reset

end

// Output logic

assign out = (state == ON);

endmodule

验证结果:

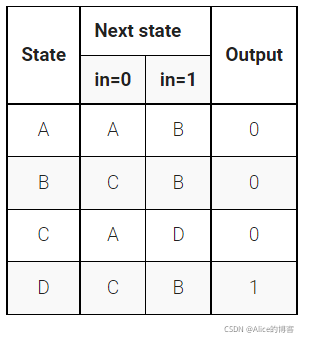

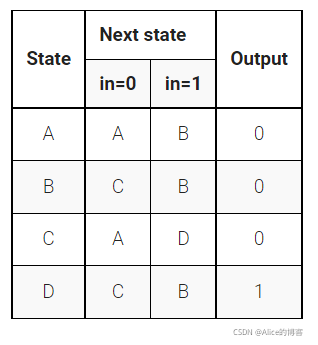

5、简单的状态转换3

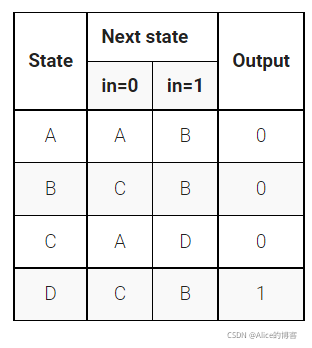

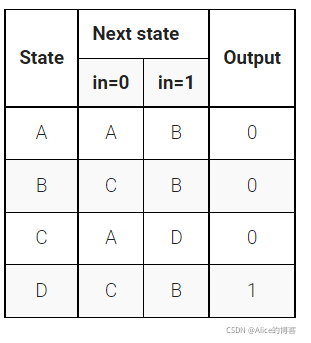

实现下面的摩尔状态机,下表是状态转移图,1输入1输出4状态。

使用以下状态编码:A=2’b00、B=2’b01、C=2’b10、D=2’b11。

代码实现:

module top_module(

input in,

input [1:0] state,

output [1:0] next_state,

output out); //

parameter A=0, B=1, C=2, D=3;

always @(*) begin

case(state) // State transition logic

2'b00:begin

if( in == 1'b1 )

next_state <= B;

else

next_state <= A;

end

2'b01:begin

if( in == 1'b1 )

next_state <= B;

else

next_state <= C;

end

2'b10:begin

if( in == 1'b1 )

next_state <= D;

else

next_state <= A;

end

2'b11:begin

if( in == 1'b1 )

next_state <= B;

else

next_state <= C;

end

endcase

end

// State transition logic: next_state = f(state, in)

// Output logic: out = f(state) for a Moore state machine

assign out = (state == D);

endmodule

验证结果:

6、简单的one-hot状态转换3

实现下面的摩尔状态机,下表是状态转移图,一输入一输出四状态。使用以下 one-hot 状态编码:A=4’b0001, B=4’b0010, C=4’b0100, D=4’b1000。

代码实现:

module top_module(

input in,

input [3:0] state,

output [3:0] next_state,

output out); //

parameter A=0, B=1, C=2, D=3;

// State transition logic: Derive an equation for each state flip-flop.

assign next_state[A] = (state[A]&~in) | (state[C]&~in);

assign next_state[B] = (state[A]&in) | (state[B]&in) | (state[D]&in);

assign next_state[C] = (state[B]&~in) | (state[D]&~in);

assign next_state[D] = state[C]∈

// Output logic:

assign out = state[D];

endmodule

验证结果:

7、简单 FSM3(异步复位)

实现下面的摩尔状态机,下表是状态转移图,一输入一输出四状态。

代码实现:

module top_module(

input clk,

input in,

input areset,

output out); //

parameter A=2'd0, B=2'd1, C=2'd2, D=2'd3;

reg [1:0] state,next_state;

always @(*) begin

case(state) // State transition logic

A:begin

if( in == 1'b1 )

next_state <= B;

else

next_state <= A;

end

B:begin

if( in == 1'b1 )

next_state <= B;

else

next_state <= C;

end

C:begin

if( in == 1'b1 )

next_state <= D;

else

next_state <= A;

end

D:begin

if( in == 1'b1 )

next_state <= B;

else

next_state <= C;

end

endcase

end

always @(posedge clk, posedge areset) begin

if(areset)

state <= A;

else

state <= next_state;// State flip-flops with asynchronous reset

end

// Output logic

assign out = (state == D);

endmodule

验证结果:

8、简单 FSM3(同步复位)

实现下面的摩尔状态机,下表是状态转移图,一输入一输出四状态。

代码实现:

module top_module(

input clk,

input in,

input reset,

output out); //

parameter A=2'd0, B=2'd1, C=2'd2, D=2'd3;

reg [1:0] state,next_state;

always @(*) begin

case(state) // State transition logic

A:begin

if( in == 1'b1 )

next_state <= B;

else

next_state <= A;

end

B:begin

if( in == 1'b1 )

next_state <= B;

else

next_state <= C;

end

C:begin

if( in == 1'b1 )

next_state <= D;

else

next_state <= A;

end

D:begin

if( in == 1'b1 )

next_state <= B;

else

next_state <= C;

end

endcase

end

always @(posedge clk) begin

if(reset)

state <= A;

else

state <= next_state;// State flip-flops with asynchronous reset

end

// Output logic

assign out = (state == D);

endmodule

验证结果:

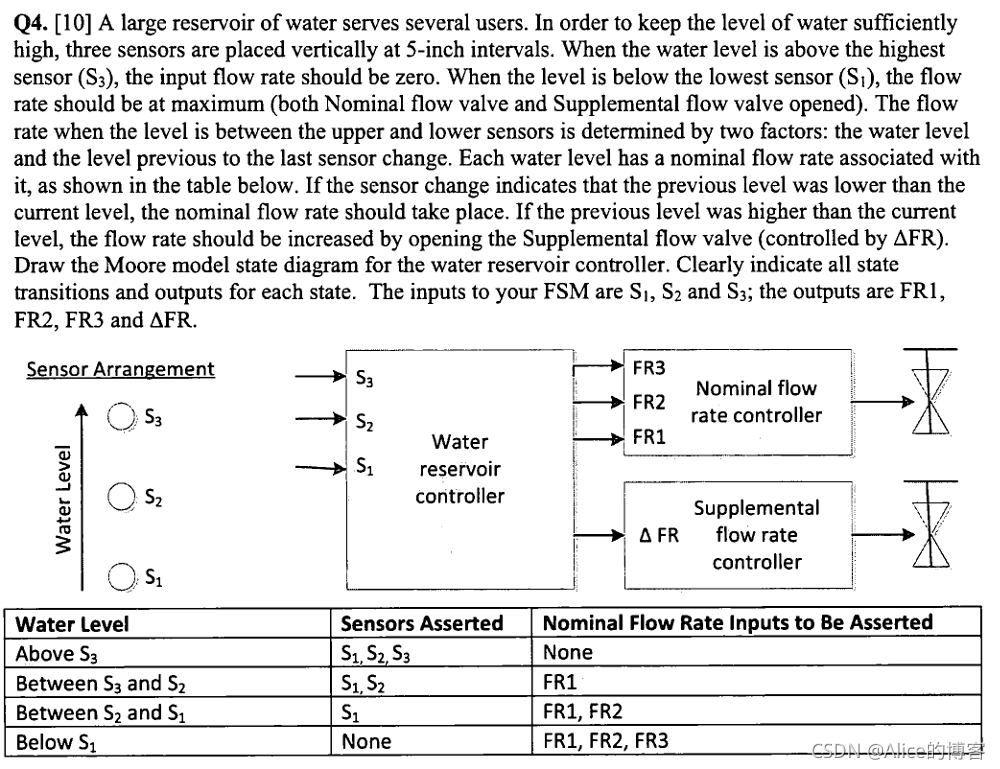

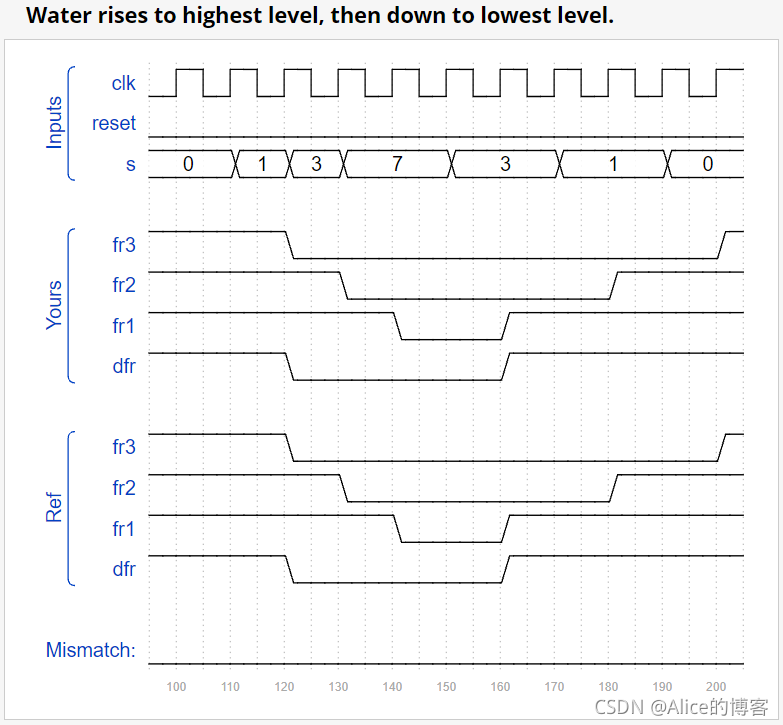

9、设计摩尔状态机

还包括一个高电平有效同步复位,该复位将状态机复位到相当于水位长时间处于低位状态。

代码实现:

module top_module (

input clk,

input reset,

input [3:1] s,

output fr3,

output fr2,

output fr1,

output dfr

);

parameter A2=3'd0,B1=3'd1,B2=3'd2,C1=3'd3,C2=3'd4,D1=3'd5;

reg [2:0] state,next_state;

always @(*)begin

case(state)

A2:next_state <= s[1]?B1:A2;

B1:next_state <= s[2]?C1:(s[1]?B1:A2);

B2:next_state <= s[2]?C1:(s[1]?B2:A2);

C1:next_state <= s[3]?D1:(s[2]?C1:B2);

C2:next_state <= s[3]?D1:(s[2]?C2:B2);

D1:next_state <= s[3]?D1:C2;

default:next_state <= 'x;

endcase

end

always @(posedge clk)begin

if(reset)begin

state <= A2;

end

else begin

state <= next_state;

end

end

always @(*)begin

case(state)

A2:{fr3,fr2,fr1,dfr} = 4'b1111;

B1:{fr3,fr2,fr1,dfr} = 4'b0110;

B2:{fr3,fr2,fr1,dfr} = 4'b0111;

C1:{fr3,fr2,fr1,dfr} = 4'b0010;

C2:{fr3,fr2,fr1,dfr} = 4'b0011;

D1:{fr3,fr2,fr1,dfr} = 4'b0000;

default:{fr3,fr2,fr1,dfr} = 'x;

endcase

end

endmodule

验证结果:

参考资料: Verilog有限状态机(2).

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?