不小心陷入狼叔的文章,这里来学习一下这三篇关于内存的文章。

更多精彩的文章建议大家近狼叔主页看一下:

https://zhuanlan.zhihu.com/p/26255460

https://zhuanlan.zhihu.com/p/26387396

内存系列一:快速读懂内存条标签

内存是我们平常接触最频繁的计算机硬件之一,内存的大小、多寡和型号和我们计算机、手机等性能密切相关。内存系列计划通过三篇文章由浅入深介绍内存的软硬件特性以及与固件的关系。这是第一篇,以一个生活情景给读者介绍内存的背景知识,为后面打下基础。

1-情景

小张有一定的计算机背景知识,最近他在京东上买了两条DDR3的内存,打算把笔记本升级成8G。可是一拆开包装到就傻眼了:

4GB看起来很好,两根刚好8GB。2Rx8是啥,PC3又是啥,10600似乎和他想买的1333的差好远,后面那串数字又代表什么呢?

小张找到了我,让我帮忙给他说说这些字母和数字都代表什么。我最是好为人师,于是开始了我们今天的介绍。

1-什么是DIMM?

在80286时代,内存颗粒(Chip)是直接插在主板上的,叫做DIP(Dual In-line Package)。

到了80386时代,换成1片焊有内存颗粒的电路板,叫做SIMM(Single-Inline Memory Module)。

由阵脚形态变化成电路板带来了很多好处:模块化,安装便利等等,由此DIY市场才有可能产生。

当时SIMM的位宽是32bit,即一个周期读取4个字节,到了奔腾时,位宽变为64bit,即8个字节,于是SIMM就顺势变为DIMM(Double-Inline Memory Module)。

这种形态一直延续至今,也是内存条的基本形态。

说到这里,小张着急了:”这和我的内存有啥关系?“。

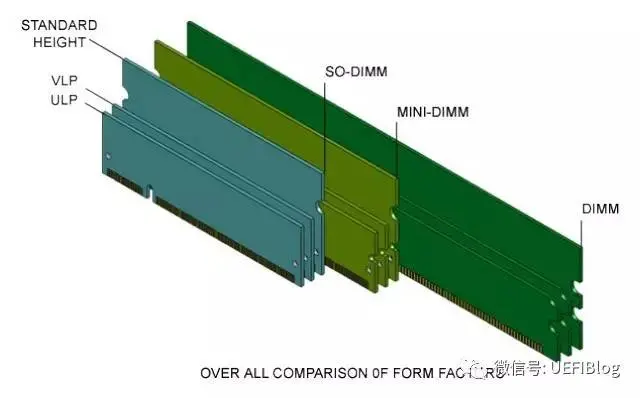

当然有关系,就是和10600S的S有关,现在DIMM分为很多种:

-

RDIMM: 全称(Registered DIMM),寄存型模组,主要用在服务器上,为了增加内存的容量和稳定性分有ECC和无ECC两种,但市场上几乎都是ECC的。

-

UDIMM:全称(Unbuffered DIMM),无缓冲型模组,这是我们平时所用到的标准台式电脑DIMM,分有ECC和无ECC两种,一般是无ECC的。

-

SO-DIMM:全称(Small Outline DIMM),小外型DIMM,笔记本电脑中所使用的DIMM,分ECC和无ECC两种。

-

Mini-DIMM:DDR2时代新出现的模组类型,它是Registered DIMM的缩小版本,用于刀片式服务器等对体积要求苛刻的高端领域。

一般内存长度 133.35mm,SO-DIMM为了适应笔记本内狭小的空间,缩短为67.6mm而且一般为侧式插入。

高度也有些变种,一般的内存条高度为30mm,VLP(Very Low Profile)降低为18.3mm,而ULP(Ultra Low Profile)更是矮化到17.8mm,主要是为了放入1U的刀片服务器中。

小张这下知道10600S中S代表了SO-DIMM,看来大小没错。不过速度呢?

2-DDR到DDR4

为了照顾小张的急性子,我就跳过了SDRAM后DDR和Rambus/RDRAM争天下的故事。

DDR SDRAM全称为Double Data Rate SDRAM,中文名为“双倍数据流SDRAM”。

DDR SDRAM在原有的SDRAM的基础上改进而来。也正因为如此,DDR能够凭借着转产成本优势来打败昔日的对手RDRAM,成为当今的主流。顾名思义,和原本的SDRAM相比,DDR SDRAM一个时钟周期要传输两次数据:

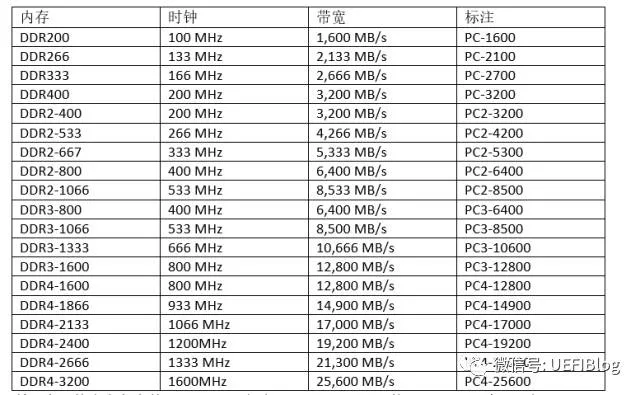

从DDR到DDR4主要的区别是在于传输速率的不同,随着时钟周期的不断降低,传输率也不断提高。

还有电压也越来越低。

有趣的是命名规则,大部分台式机DIMM厂商都会标注DDRx-yyy,x代表第几代,yyy代表数据传输率。

而大部分的SO-DIMM和RDIMM等则标注PCx-zzzz,x还代表第几代,zzzz则代表最大带宽。因为DDR位宽为64位,8个字节,所以zzzz=yyy * 8,而yyy又是时钟的两倍。下面这张表是主要的各代DDR内存的速度:

所以小张的内存条上的PC3-10600S代表DDR3,1333MHz的SO-DIMM。小张又问,那2R*8啥意思呢?

1325*8=10600

3-RANK和BANK

其实从外观上就可以看出来小张的内存条由很多海力士的内存颗粒组成。

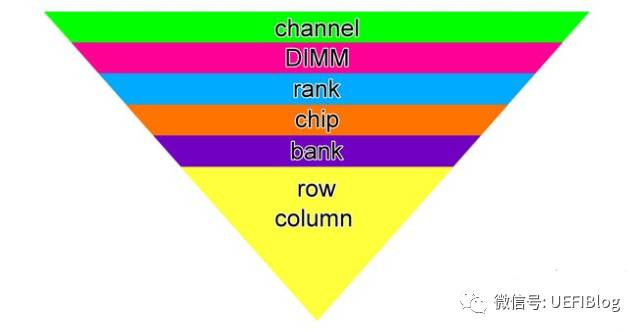

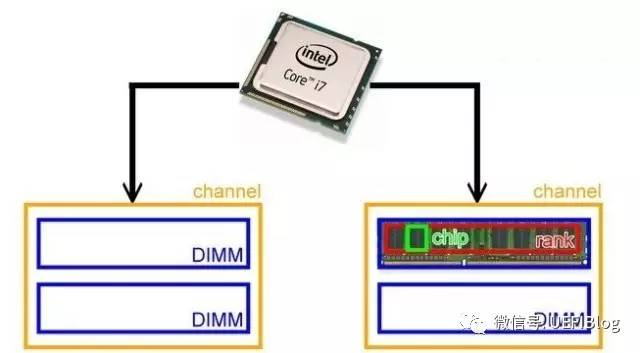

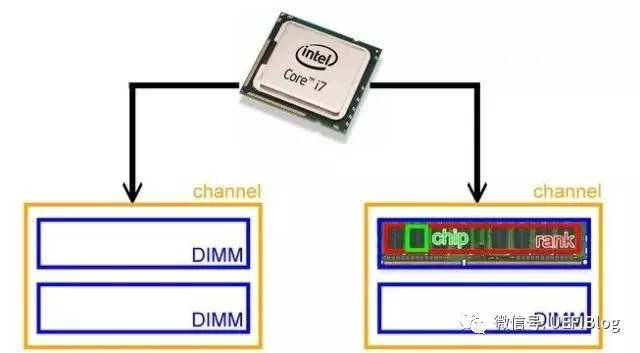

从内存控制器到内存颗粒内部逻辑,笼统上讲从大到小为:channel>DIMM>rank>chip>bank>row/column,如下图:

一个现实的例子是:

在这个例子中,

- 一个i7 CPU支持两个Channel(双通道),

- 每个Channel上可以插俩个DIMM,

- 而每个DIMM由两个rank构成,

- 8个chip组成一个rank。由于现在多数内存颗粒的位宽是8bit,而CPU带宽是64bit,所以经常是8个颗粒可以组成一个rank。

所以小张的内存条2R X 8的意思是由2个rank组成,每个rank八个内存颗粒(为啥我们以后讲)。

由于整个内存是4GB,我们可以算出单个内存颗粒是256MB。

3-后记

小张这下放心了,不过他提起看到过不少内存条上都有很多数字标记,如:

这些是什么呢?其实,这是内存颗粒的时延(Latency)数据,如4-4-4-8, 5-5-5-15, 7-7-7-21, 或9-9-9-24,分别代表 CL-tRCD-tRP-tRAS的数据,越小越好。具体这些都是什么,就需要更深入的知识了,我们将会在下一篇硬件原理中讲到,而且我们还会在UEFI的memory reference code(MRC)部分再详细深入说明这些参数的具体使用。

如果你和小张一样意犹未尽,在下一篇文章之前大家可以思考下面几个问题:

每一代内存条宽度都一样,会不会插错呢?

从前面各代内存速度表可以看出,每一代和前一代带宽都有部分重复,这是为什么?

前一代和下一代如果带宽一样,那个performance更好呢?

文章中说2Rx8 表示2个Rank,每个Rank有八个内存颗粒。那怎么我之前的老笔记本上的DDR2 南亚内存写着 PC2-5300S 512MB 2Rx16 667。可是这个内存条每一面只有4个内存颗粒啊?

“所以小张的内存条2R X 8的意思是由2个rank组成,每个rank八个内存颗粒”,这里说每个RANK八个内存颗粒应该是在 每个chip是8bit 的情况下成立的。因为如果是每个chip为8bit的位宽(即×8),那么就可以得出每个rank 可以支持8个chip(即每个rank八个内存颗粒),2R即支持16个chip。 如果是2R×16,就是每个rank支持4个chip。所以原话中的容易被误解为×N就代表每个RANK N个内存颗粒,其实不是这样的。×8指的是CHIP的位宽,这里只是在数值上正好等于了每个rank的内存颗粒数。

内存系列二:深入理解硬件原理

本篇文章承接上文继续介绍DDR内存的硬件原理,包括如何寻址,时序和时延以及可以为提高内存的效能可以有哪些方法。

上次虽然解决了小张的问题,却引发了他对内存原理的兴趣。这不他又来找我了,说我还欠他一个解释。这次我们约在一个咖啡馆见面,这次内容有点深入,我带了些图片,小张也点了一大杯美式,计划大干一场。看着他认真的样子,我也决定毁人不倦,把他也带入IT工程师的不归路。。。

1-寻址(addressing)

为了了解前几天说的几个延迟参数,不得不介绍下DIMM的寻址方式。

也许你发现了上次介绍Rank和chip的关系时,有个Bank/Column/row我们没有讲到,它们和如何寻址密切相关。还记得上次的图片吗?

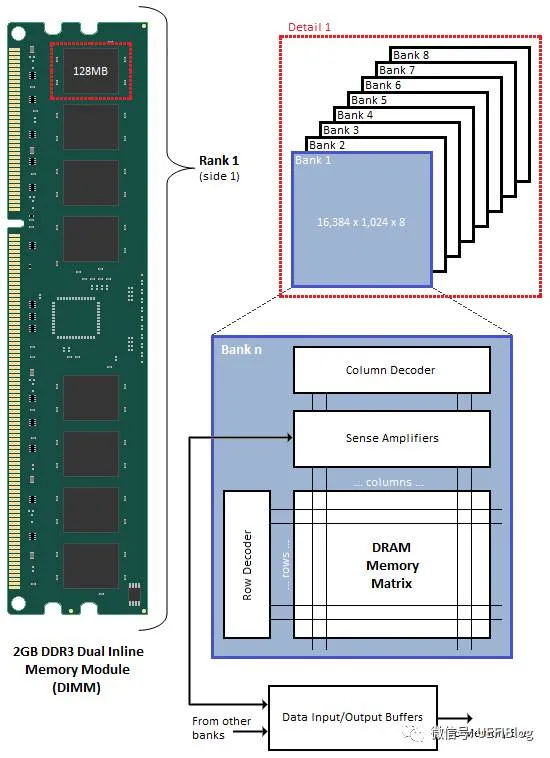

这次我们来看看rank和Chip里面有什么,如下图:

这是个DDR3一个Rank的示意图。我们把左边128MB Chip拆开来看,它是由8个Bank组成,每个Bank核心是个一个存储矩阵,就像一个大方格子阵。这个格子阵有很多列(Column)和很多行(Row),这样我们想存取某个格子,只需要告知是哪一行哪一列就行了,这也是为什么内存可以随机存取而硬盘等则是按块存取的原因。

说到这里,小张来了兴致:“我知道,我知道,大学学过,计算机组成原理里面讲过,这是存储单元的行地址线和列地址线,中间那个格子里面是一个Bit!”。小张掌握的知识还不少呢! 但是这里只是有些类似,可以这么想象,但不尽然,CAS#和RAS#只有一根信号线。

实际上每个格子的存储宽度是内存颗粒(Chip)的位宽,在这里由8个Chip组成一个Rank,而CPU寻址宽度是64bit,所以64/8=8bit,即每个格子是1个字节。

选择每个格子也不是简单的两组信号,是由一系列信号组成,以这个2GB DDR3为例:

-

- 片选(Chip Select)信号,S0#和S1#,每个用于选择是哪个Rank。

-

- Bank地址线,BA0-BA2, 2^3=8,可以选择8个Bank

-

- 列选 (Column Address Select), CAS#,用于指示现在要选通列地址。

-

- 行选(Row Address Select),RAS#用于指示现在要选通行地址。

-

- 地址线,A0-A13,用于行和列的地址选择(可并不都用于地址,本处忽略)。

-

- 数据线,DQ0-DQ63,用于提供全64bit的数据。

-

- 命令,COMMAND,用于传输命令,如读或者写等等。

注意这里没有内存颗粒的选择信号线,只有Rank的选择信号。在Rank选择好后,8个内存颗粒一起被选中,共提供64bit的数据。

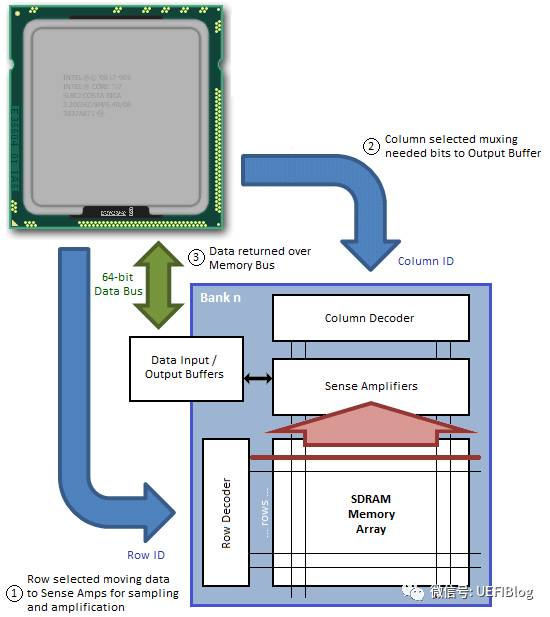

读取和写入数据也稍微复杂点,简单来说分为以下三步:

-

- 行有效。RAS#低电平,CAS#高电平。意味着现在行地址有效,同时在A0-A13传送地址信号,即2^13个Row可以选择。

-

- 列有效。RAS#高电平,CAS#低电平。意味着列地址有效,这时在A0-A13上传送的是列地址。没错,A0-A13是行列共用的,所以每个格子选择需要有1和2两步才能唯一确定。

-

- 数据读出或写入。根据COMMAND进行读取或者写入。在选定好小方格后,就已经确定了具体的存储单元,剩下的事情就是数据通过数据I/O通道(DQ)输出到内存总线上了。

这里只介绍随机访问, Burst模式这里略过。下图是个简单的图示:

2-时序(Timing)

一气说了这么多,我不禁口干舌燥,停下来喝了一大口咖啡。小张以为我说完了,着急的问我:“我好像听懂了,不过那好几个数字还没讲呢。”。别着急啊,且听我慢慢道来。正因为访问一个数据需要大致三步,为了保证信号的完整性,步骤直接要有区隔,一起发出来会造成错乱,间隔太近也会为采样带来难度,容易引入噪音。所以时序非常重要,

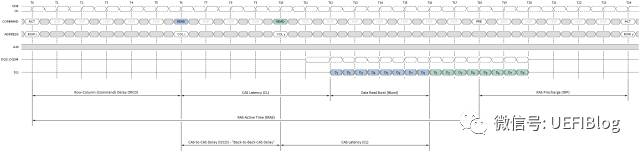

下面是个背对背(back-to-back)读写的时序图:

3-时延(Latency)

小张一看到这个图,不禁大叫:”太复杂了,看得我都犯密集恐惧症了,看不懂!“。没关系,我们拆开了一个个看。

-

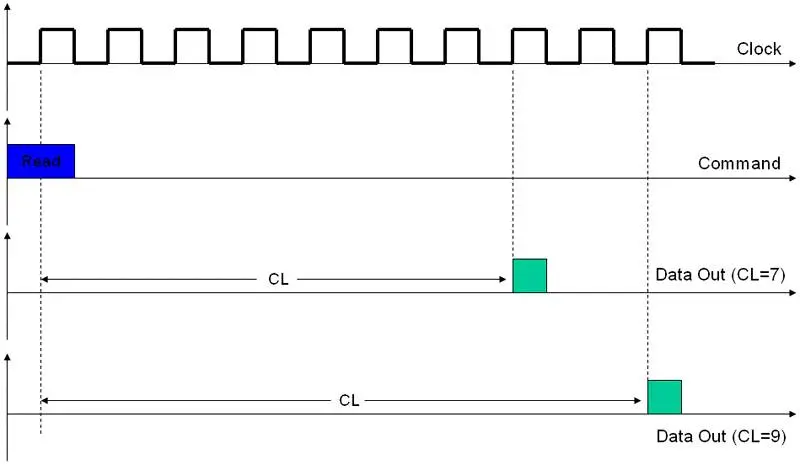

- CL: CAS Latency。 CL是指CAS发出之后,仍要经过一定的时间才能有数据输出,从CAS与读取命令发出到第一笔数据输出的这段时间,被定义为CL(CAS Latency,CAS时延)。由于CL只在读取时出现,所以CL又被称为读取时延(RL,Read Latency)。也就是我们上面第3步读取时需要的时间。CL是延迟里面最重要的参数,有时会单独在内存标签上标出如CLx。它告诉我们多少个时钟周期后我们才能拿到数据,CL7的内存会延迟7个周期才能给我们数据,CL9的则要等9个。所以越小我们越能更快的拿到数据。注意这里的周期是真正的周期而不是标注的DDR3 1333MHz的周期,因为一个周期传输两次,真正的周期只是1/2,这里是666MHz。如下图,是CL7和CL9的例子:

如果相同频率的内存,CL7可以比CL9有22%的效能提高。

- CL: CAS Latency。 CL是指CAS发出之后,仍要经过一定的时间才能有数据输出,从CAS与读取命令发出到第一笔数据输出的这段时间,被定义为CL(CAS Latency,CAS时延)。由于CL只在读取时出现,所以CL又被称为读取时延(RL,Read Latency)。也就是我们上面第3步读取时需要的时间。CL是延迟里面最重要的参数,有时会单独在内存标签上标出如CLx。它告诉我们多少个时钟周期后我们才能拿到数据,CL7的内存会延迟7个周期才能给我们数据,CL9的则要等9个。所以越小我们越能更快的拿到数据。注意这里的周期是真正的周期而不是标注的DDR3 1333MHz的周期,因为一个周期传输两次,真正的周期只是1/2,这里是666MHz。如下图,是CL7和CL9的例子:

-

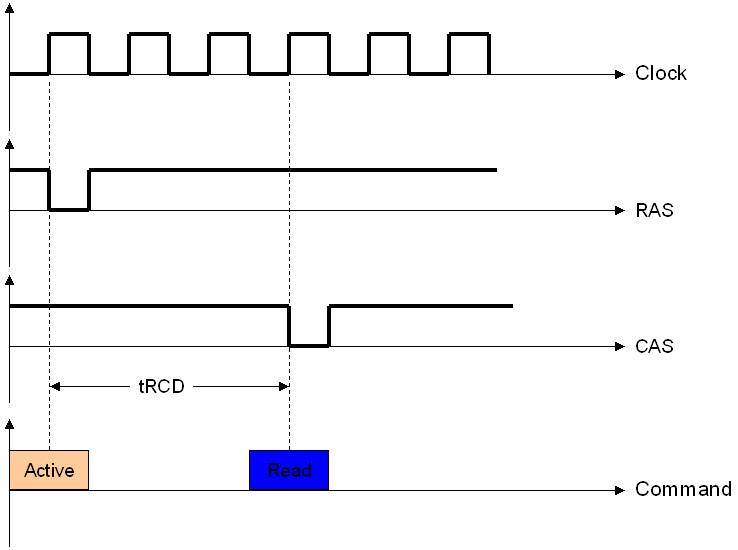

- tRCD:RAS到CAS时延。 在发送列读写命令时必须要与行有效命令有一个间隔,这是根据芯片存储阵列电子元件响应时间所制定的延迟。即步骤1和2要间隔的时间。这个间隔当然也是越快越好了,下面是个tRCD=3的例子:

你也可以看出这个时间也是激活命令和读命令的间隔。

-

- tRP: 预充电有效周期(Precharge command Period)。在上一次传输完成后到下一次行激活前有个预充电过程,要经过一段充电时间才能允许发送RAS。也就是步骤1的准备工作要做多久。下面是个例子:

还有两个类似的时延tRAS和CMD,我看到小张都快睡着了就不讲了。总之,所有这些时延共同构成了整体时延,而时延是越小越好。

4-SPD

说了这么多,小张总算搞懂内存标签条上的4-4-4-8, 5-5-5-15, 所代表的 CL-tRCD-tRP-tRAS-CMD都是啥意思了。不过小张有点搞不懂,这些数据印在纸上消费者是看懂了(实际上似乎没多少人了解),可电脑又没长眼睛,它是怎么知道的呢?

其实,每个DIMM在板子上都有块小的存储芯片(EEPROM),上面详细记录了包括这些的很多参数,还有生产厂家的代码等等,这也是BIOS为什么能知道我们插了哪种内存的原因。在小张的内存条上,我指给了他看:

实际上随着DDR的一步步进化,这些延迟的时钟周期个数也在步步提高,但由于频率的加快,实际上是在时间是在慢慢的减少的。

5-效能提高的其他手段

看时间还早,我和小张聊起了除了提高频率,还有什么办法能够提高内存存取速度。

1。多通道(Channel)

现代内存控制器都从北桥移入CPU内部,而且内存控制器都可以同时操作多个通道。典型的台式机和笔记本CPU很早就支持双通道,现在还加入了三通道。如果数据分布在插在不同的通道上的内存条上,内存控制器可以不管上面这些延迟啊时序啊,同时可以读取他们,速度可以翻倍甚至三倍!小张听了跳了起来:”我也要翻倍!”。别急,要启用多通道,首先要插对插槽。现在主板制造商为了让小白用户插对内存条,通常用颜色标识内存通道。注意同一个通道颜色不同!所以要把内存插在颜色相同的内存插槽里,才能让内存占据不同的通道。最好有主板手册检查一下,插好后进入BIOS里面看看现在内存状态是不是多通道模式。

一、位置不同

北桥芯片就是主板上离CPU最近的芯片,以CPU插座为北的话,靠近CPU插座的一个起连接作用的芯片称为“北桥芯片;

南桥芯片(South Bridge)是主板芯片组的重要组成部分,一般位于主板上离CPU插槽较远的下方,PCI的前面,即靠主机箱前的一面。

二、作用不同

北桥主要负责CPU与内存之间的数据交换,主要控制 CPU内存显卡等高速设备;

南桥主要是负责I/O接口等一些外设接口的控制、IDE设备的控制及附加功能等等。

三、发展方向不同

北桥芯片的数据处理量非常大,发热量也越来越大,所以现在的北桥芯片都覆盖着散热片用来加强北桥芯片的散热,有些主板的北桥芯片还会配合风扇进行散热;

南桥芯片的发展方向主要是集成更多的功能,例如网卡、RAID、IEEE1394、甚至WI-FI无线网络等等。

2。Interleave

看着小张跃跃欲试的样子,我不禁给他泼了盆冷水。幻想美妙,现实残酷。多通道在很多时候用处并不明显!因为程序的局部性,一个程序并不会把数据放到各个地方,从而落入另一个DIMM里,往往程序和数据都在一个DIMM里,加上CPU的Cache本身就会把数据帮你预取出来,这个提高就个不明显了。除非你运行很多巨型任务才行。

“啊,我都是开一个游戏打,对我来说没啥用处啊,简直是鸡肋!”,小张说。也不尽然,还有种办法,就是让同一块内存分布到不同的通道中去,这种技术叫做Interleaving。这样无论Cache命中与否都可以同时存取,多通道的技术才能发挥更大的用处。“太好了,要怎么才能开启这个interleave呢?”,我不禁呵呵了,这个功能一般只有服务器CPU才有,你的i5要是有了,谁去买几千上万的服务器CPU呢?

3。Overclock

“你这不是废话吗,我要怎么样才能搭建个发烧机才配有的高速内存呢?”。其实小张可以购买发烧级的内存条。这些内存条DDR3标注达到2133以上!但是要注意,如果我们把这些内存插入一般主板,很有可能会运行在1333或者1600上面,因为这是DDR3规定的最高频率。好马配好鞍,要有个能支持超频内存的主板,在主板BIOS里面升压升频才能真正用好这些发烧内存条。

6-尾声

时间差不多了,我向小张保证下次还会介绍神秘的BIOS如何初始化内存,正要离去。小张拉住了我,说:“你上次挖的坑还没填呢!”“什么坑?”也许是我挖坑太多,记不住了。“就是上次你让我回去想的三个问题。第一个我知道了,DIMM有防呆口,几代DDR防呆口位置不同,插不进去,我在网上google过了,后面两个实在想不出来”。

每一代内存条宽度都一样,会不会插错呢?

从前面各代内存速度表可以看出,每一代和前一代带宽都有部分重复,这是为什么?

前一代和下一代如果带宽一样,那个performance更好呢?

好吧,那我们长话短说,实际上两个问题可以一起回答,今天我们知道DDR每代的各种时延参数是上升的,所以如果两代一样的频率,实际上性能有可能还会下降! 譬如DDR2 800在很多时候比DDR3 800的时延要小。我们可以认为每代的起点比前一代的低,有一段重合期,在频率上去后会弥补时延的时钟个数差异,比较时延是clock个数,而不是时间,clock快了,有可能时延会更小。而这段重合期,也为不同的商业策略留下了空间。(这个部分还是需要体会一下!!!!)

小张还是抓住我,他不知道从哪里查了些名词,什么预取个数每代增加,而内核频率不同于外部频率等等。我希望他能自己找找资料看看,也顺便挖了个新坑:

-

为什么每代DDR要升级,不直接把频率向上提高就行了,为什么没有DDR2 3200的内存?

-

DDR的内存还是并行的数据,串行似乎可以更高速,比格更高,为什么不弄个串行访问的内存呢?

小张陷入了沉思,我也暗喜又骗到一顿咖啡下午茶。不过回去还要准备些材料才能继续混吃混喝,下次介绍完内存的BIOS部分,还有啥题目可以继续吸引小张呢?

内存系列三:内存初始化浅析

本篇承接上两篇文章,继续介绍DDR内存在固件中如何初始化,以及如何提高初始化的效率等等。

小张上次回去后,好久都没来找我,我以为他对内存知识已经不感兴趣了,没想到他今天又约我见面。我来到上次的咖啡馆,他已经等我好久了。原来他上次回去后,找了好久资料,虽然对硬件知识有了个整体的把握,但看的越深入就有越多的疑问。他知道我对固件了解比较深入,想问问我关于软件方面的问题。我不禁被小张对知识的渴求所打动,点了一杯美式咖啡,开始了今天的介绍。

1-内存初始化

小张开门见山,直奔主题:“内存硬件结构这么复杂,我平时写程序怎么从来都没有用过,是不是操作系统把什么寻址啊、延迟啊都自己搞定了?”。

这就不对了,操作系统对内存的了解只到了段页管理那一层,也就是到了物理地址那里。你可以看看我的博客,上面有介绍段页管理。物理地址到Rank,Bank等的寻址,都是内存控制器完成的。”我喝了一口咖啡,开始津津有味的介绍起来。

自Intel/AMD把北桥取消后,内存控制器都被集成进了CPU,毕竟摆脱了FSB,延迟大大减小,而带宽可以大大增加,同时主板的成本也降低了。(前端总线——Front Side Bus(FSB),是将CPU连接到北桥芯片的总线。)

初始化内存控制器和内存是固件的一项重要任务,可以说是主要任务之一。也许你看过前面关于UEFI的介绍,就会明白,内存初始化是在PEI阶段完成的。一般来说我们把内存初始化分成三个阶段:

1。准备阶段

这个阶段主要是为了内存training做好准备。它要完成:

-

A. 初始化内存控制器寄存器。

-

B. 读取SPD内容。通过SMBUS读取SPD的内容,对各个延迟记录在案,下个阶段会用到。各个DIMM的SMBUS地址不同,一般是A0/A1/A2/A3,和主板走线有关。这个步骤也可以检查出来内存插槽上有没有插DIMM。 在有些嵌入式主板上内存颗粒是直接焊到主板上的,这时很可能没有SPD。 这时就需要固件工程师根据实际的内存颗粒的硬件手册,将延迟信息硬编码到代码中了。

2。内存Training

看到Training也许你会感到奇怪,人工智能是要训练,内存也要训练吗?

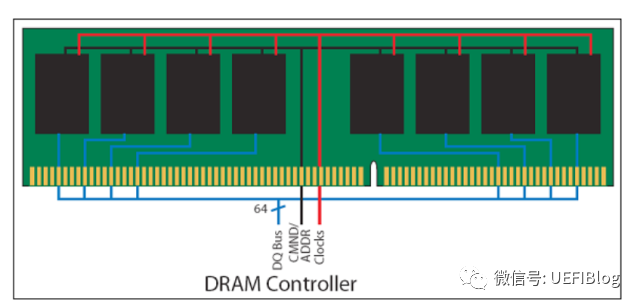

从DDR2到DDR3,一个很大的改动是信号线的连接方式。一个典型的DDR2的连接方式如图:

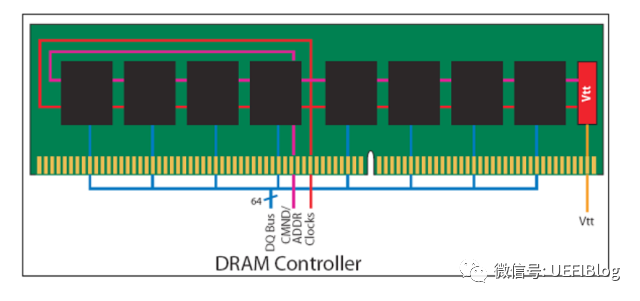

而DDR3变成:

(请问下ddr3示意图右边为什么要特意标注Vt? 看上去与clk addr是连起来的。

ddr3采用fly by布局形式,后面vtt是为了保证cmd clk 信号完整性而给终端电阻提供的电压)

这种菊花链式的方式,DDR标准的制定者JEDEC对它有个专门的叫法——“Fly-by”。

这种设计大大减小DIMM厂商的硬件制造难度。同时由于CLK/CLK#、DQS、AD和CMD信号不需要同时传递,改善了信号完整性,使更高频率成为可能。

世界上没有免费的午餐,它也带了不少麻烦,一个很大的问题是内存控制器的时序协调难度变大了很多。

菊花链的连接方式也意味着信号在各个内存颗粒之间传递有个时间差。第一个内存颗粒和第二个颗粒也许延迟不大,但到了第八个就相当可观了。

回忆一下我们上次的介绍,在行有效和列有效后,过了CL的时间第一颗chip把数据放在数据线DQ相应位上,而要过了很久第八颗Chip才把数据准备好,内存控制器要何时才能采集数据呢?

现在每个内存通道一般都有两个内存插槽,情况会更加复杂。火上浇油的是,DDR标准是JEDEC制定的,内存颗粒和DIMM厂商是个生态圈,里面鱼龙混杂,内存颗粒和DIMM的延迟千奇百怪。

这和ARM做的嵌入式平台只需要支持固定的内存颗粒完全不同,所有主板厂商都希望支持市面上更多的内存条。有时这就像踩钢丝,对内存A很好的时序,也许对内存B就不行。

如果在启动阶段就发现时序错误还好,错误或者过激的时序如果躲过了BIOS的内存检测,到了操作系统运行的时候会造成更大的麻烦。

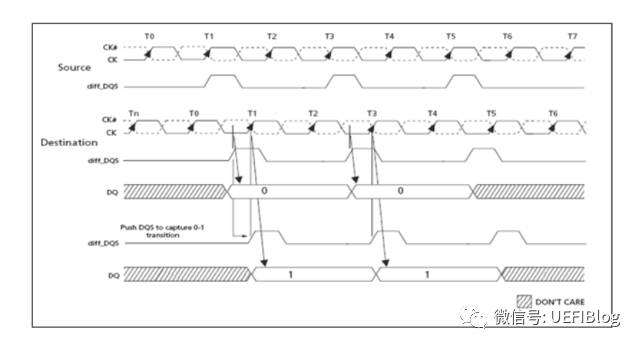

如何才能准确的设定时序呢?所幸JEDEC提供了标准做法,叫做Write Leveling Coarse。简单来说,就是内存控制器不停的发送不同时延的DQS 信号,内存 颗粒在DQS-DQS#的上升沿采样CK 的状态,并通过DQ 线反馈给DDR3 控制器(一组01010101的数据)。

控制器端反复的调整DQS-DQS#的延时,直到控制器端检测到DQ 线上0 到1 的跳变控制器就锁住此时的延时值,此时便完成了一个Write leveling过程。如下图:

它结合其他的如on-die termination (ODT)和调节Vref电压等一起完成了内存的Training。这是个不断找到平衡点的过程,也是个训练内存控制器了解DIMM的Timing和电压的过程。

3。扫尾阶段

假定上个阶段成功的发现并设置了参数,下面就比较简单了。主要是设置Channel和Interleave,将结果报告给固件的其他部分了。

这里有许多信息比较有趣,有内存的厂家、具体型号、数量多寡、内存条和内存插槽的配合情况,多CPU还有内存的亲缘性关系等等,这些信息会被放入HOB中以备以后调用。

2-其他

滔滔不绝讲了半天,心想这些够小张喝一壶了吧。我满意的喝了口咖啡,没想到小张从口袋里拿出来个A4纸,上面密密麻麻好多问题。好小子,前面装傻,在这里等着我呢。没关系,兵来将挡,水来土掩,尽管放马过来吧!

1。如何得到源码

“听了半天,似乎听懂了,有没有代码看看呢? Talk is cheap, show me the code!”。内存初始化代码一般由芯片厂商提供,Intel管它叫MRC(memory reference code)。因为其中涉及大量的寄存器操作,一般采取授权访问的方式提供给IBV和OEM而不是open source。

所幸Intel的开源硬件平台伽利略(Galileo)开放了SOC Quark的所有源代码,包括MRC代码,它在:

tianocore/edk2:https://github.com/tianocore/edk2-archive/tree/master/QuarkSocPkg/QuarkNorthCluster/MemoryInit/Pei

有兴趣的同学可以去学习一下。

2。CAR

“我看内存初始化之前,UEFI已经在执行c程序了。这时堆栈在哪里呢?”。

好问题,在内存准备好之前。**UEFI固件一般把cache初始化为内存(CAR, Cache As Ram)。**不但如此,我们还可以把一部分cache拿来继续做cache用,缓存数据和代码,而且被用作内存的cache还可以执行代码!Cache可真是强大啊!

3。Fast boot/S3

“内存初始化要训练,感觉很慢,有没有办法加速呢?”。有的,如果我们没有更换内存条,我们其实没有必要每次都从头开始训练。我们可以把第一次开机训练的内存数据存储下来,以后用前面的数据就行了,这就是很多BIOS内存部分的Fast Boot。

“那我要是换了内存呢,会死机吗?“。不会的,主板有个GPIO连接到机箱开关上,我们打开机箱,BIOS会捕捉到这个信息(叫做Intrude)。利用这个信号,我们可以认为用户做了些改变配置的事,我们在从头训练就好了。有的MRC还会在SPD信息改变后自动重新训练。

“能讲讲休眠模式下内存的设置吗?”。S3,也就是Sleep to memory,是ACPI规定的一种休眠模式,具体我们以后再讲(再挖个坑有没有?)。这里我就简单说下内存的状态。**一般SDRAM都要刷新,这是由它的设计决定的,它有个特殊的模式,叫做自刷新,**在这个模式下,内存内容不会消失而且耗电极小。我们的S3就是把内存设置成这种状态。

4。如何设置各种延迟

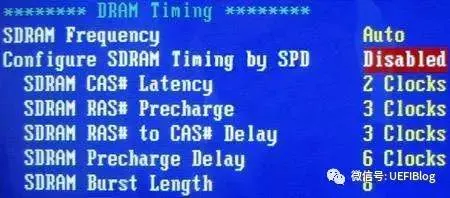

“我能改变上次说的那些延迟参数吗?”。BIOS一般会根据SPD自动设置各种延迟,我们也可以在BIOS设置中自行设置这些参数,如下图:

但是设置要小心,错误的改动有可能会造成启动不了,确定你改动这些设置之前知道怎么清除CMOS或者重置BIOS。

3-尾声

时间不早了,我也该和小张告别了,希望这三次的介绍能让小张有所收获。

小结

以前对于内存的认识都是只到了映射、页表这个层级,今天进一步的了解到了硬件层面的东西。后续希望自己有天能对这个虚拟地址映射到物理地址,再到物理地址的访问,整个端到端的串起来,那可真的太酷啦。

感谢狼叔的文章,干活太多了!!!

1782

1782

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?