一、ADC基本原理

AD转换过程:

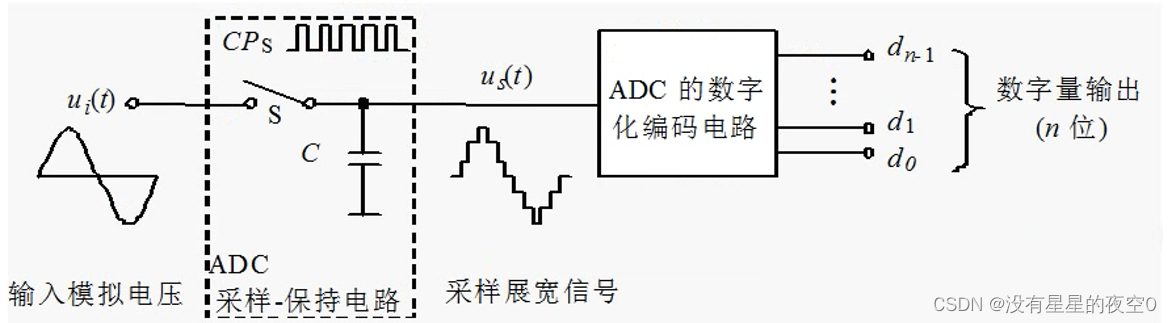

1、采样保持:

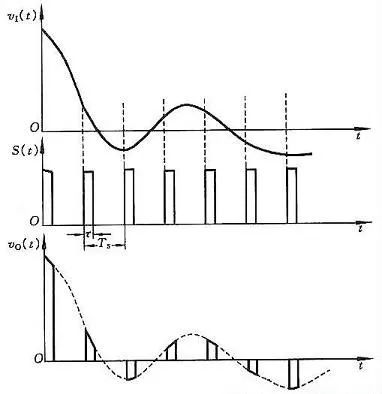

采样:将一个时间上连续变化的模拟量转化为时间上离散变化的模拟量。

保持:采样电路所取得的模拟信号转化为数字信号都需要一定的时间(不能做到实时转换),为了给后续的量化编码过程提供一个稳定值,每次取得的模拟信号必须通过保持电路保持一段时间。

2、量化:为将模拟信号转换为数字量,在A/D转换过程中,还必须将采样-保持电路的输出电压,按某种近似方式归化到相应的离散电平上,这一转化过程称为数值量化,简称量化

3、编码:量化后的数值最后还需通过编码过程用一个代码表示出来。经编码后得到的代码就是A/D转换器输出的数字量。

ADC原理图解

采样电路中的波形

采样保持电路波形

-

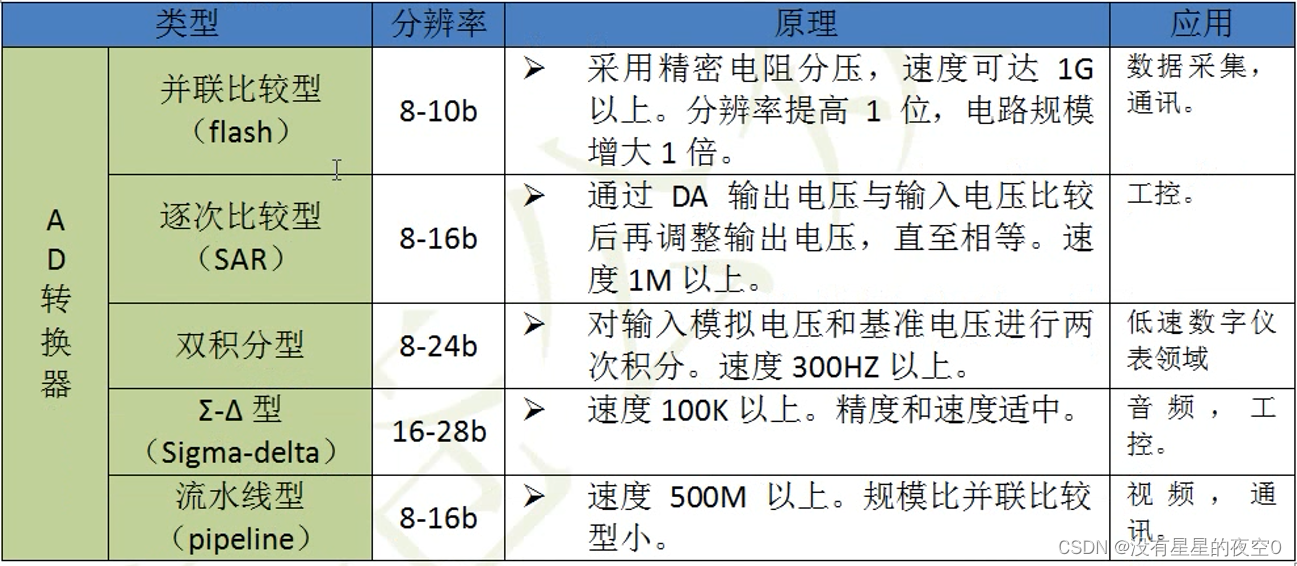

二、ADC几种常见类型

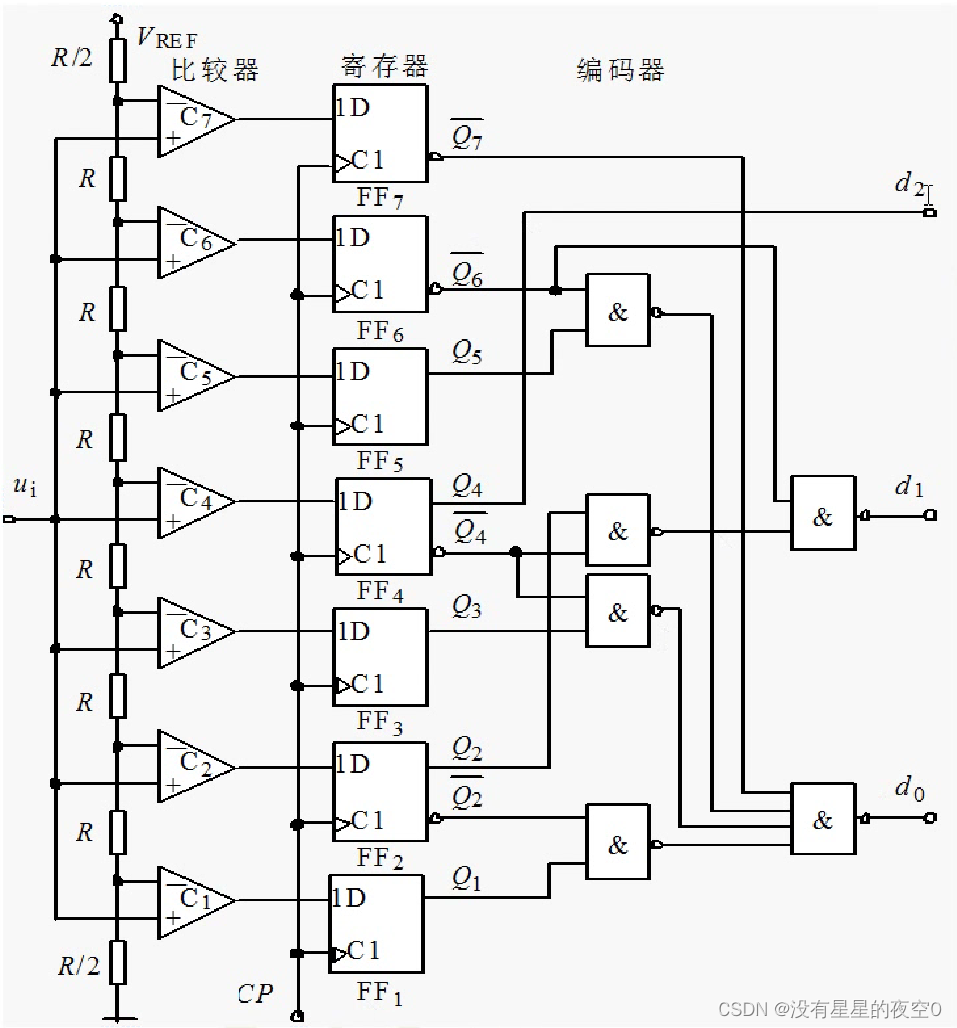

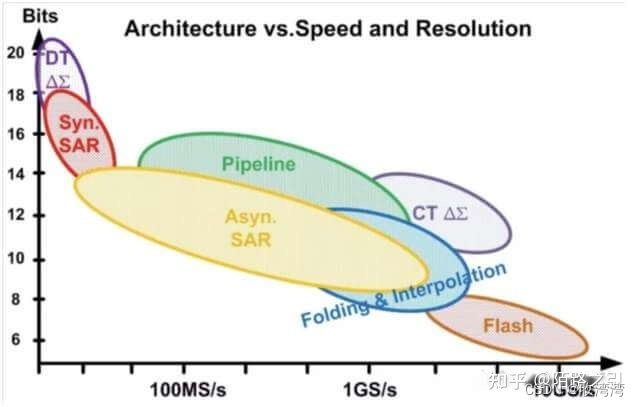

1、并联比较型(Flash)

原理:FLASH ADC是一种基于比较器和多个参考电压的模拟信号转换器。它使用一个线性电压阶梯和每个阶梯上的比较器来将输入电压与连续的参考电压进行比较。

原理:FLASH ADC是一种基于比较器和多个参考电压的模拟信号转换器。它使用一个线性电压阶梯和每个阶梯上的比较器来将输入电压与连续的参考电压进行比较。

优点:转换速度快、精度高等优点。

缺点:电路结构复杂,电路设计难度大。

运用:常用于需要高速数字处理的应用场合,例如高速数据采集系统、高速通信网络和超高清视频等领域

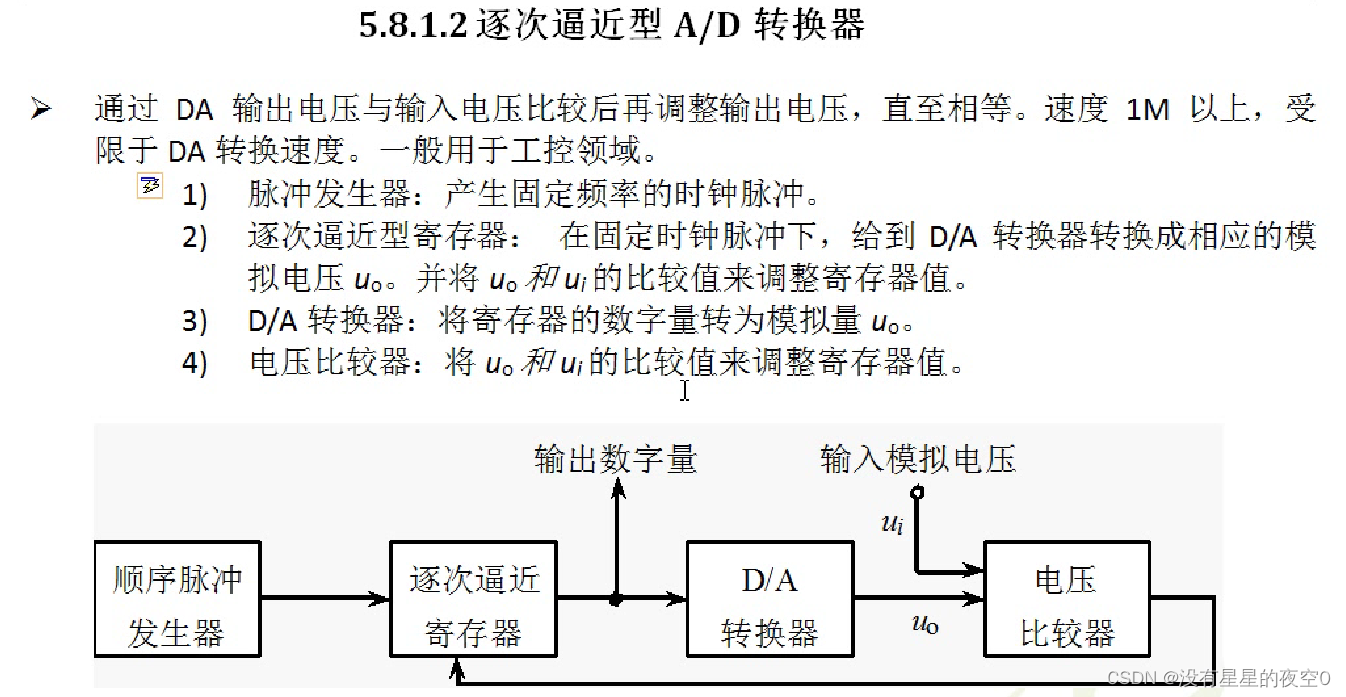

2、逐次逼近型(SAR ADC)

转换过程:它首先将输入信号与一个参考电压进行比较,然后将比较结果与参考电压的一半进行比较,再根据比较结果确定下一步比较的阈值。通过不断重复此过程,逼近输出的精度越来越高,最终得到目标的数字化结果,这个比较的次数正好是ADC的量化深度,也就是位数。

优点:结构简单,转换速度快,且精度高,在数字信号处理中广泛应用。

缺点:由于其需要逐步逼近,所以处理不稳定、干扰较大的信号可能出现误差,导致收敛慢、精度下降等问题。

运用:STM32的ADC属于是SAR ADC

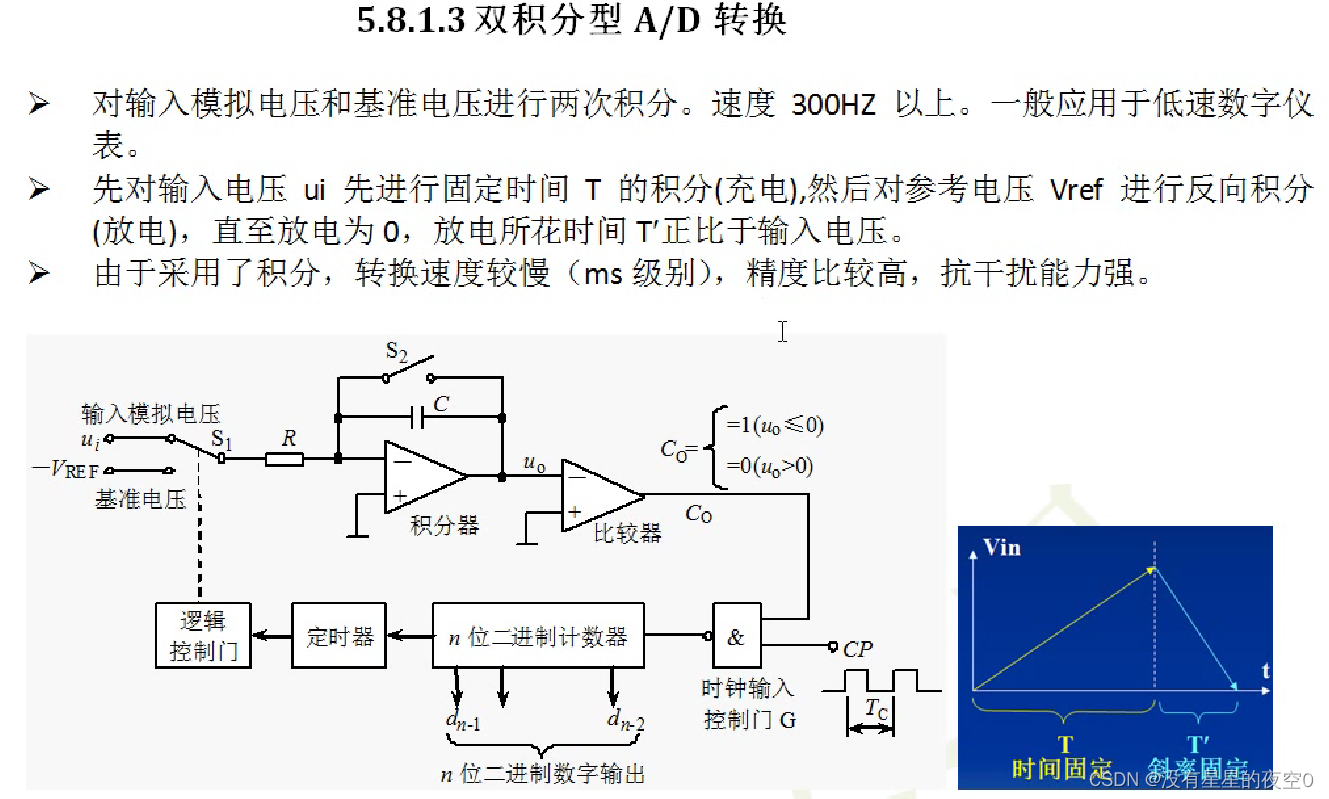

3、双积分型

基本原理:是将输入电压变换成与其平均值成正比的时间间隔,再把时间间隔转换成数字量,属于间接转换。

转换过程:先将开关接通待转换的模拟量Vi,Vi采样输入到积分器,积分器从零开始固定时间T的正向积分,时间T到后,开关再接通与Vi极性相反的基准电压Vref,将Vref输入到积分器进行反向积分,直到输出位0V时停止积分。Vi越大,积分器输出电压越大,反向积分时间也越长。计数器在反向积分时间内所计的数值,就是模拟电压Vi所对应的数字量,实现了A/D转换。

优点:精度比较高,抗干扰能力强。

缺点:由于需要积分,所以转换速度较慢(ms级别)。

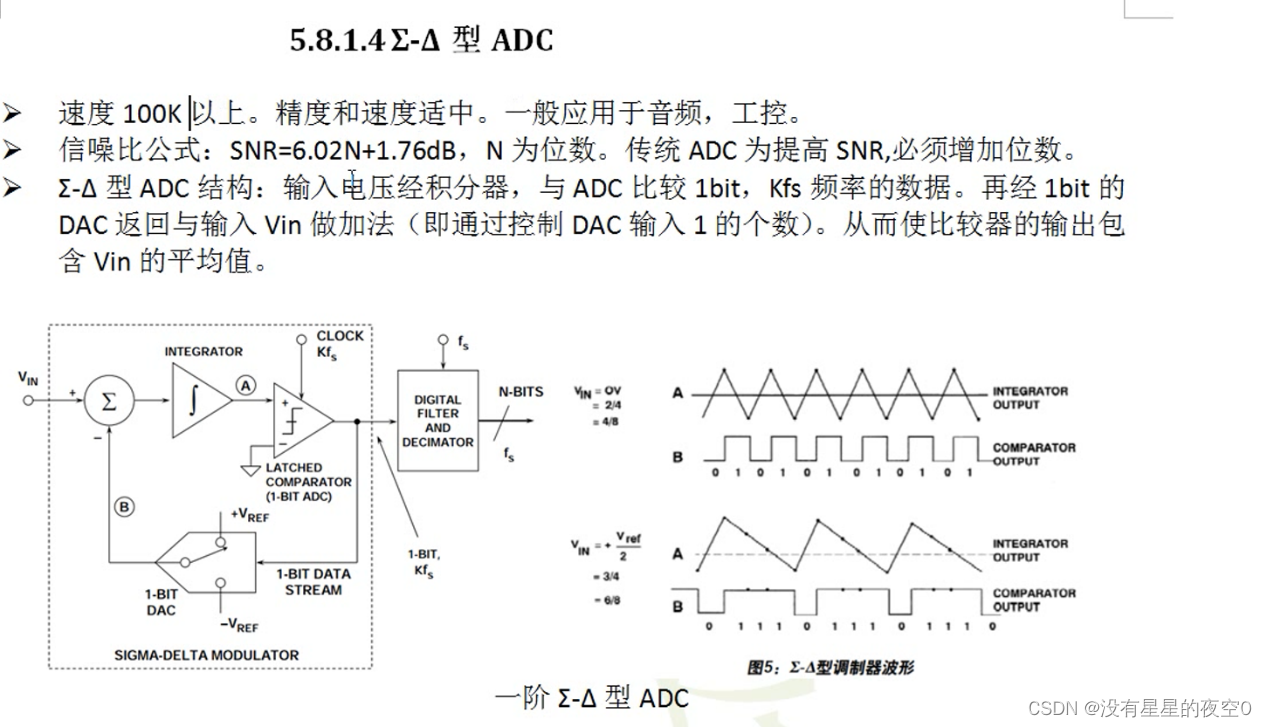

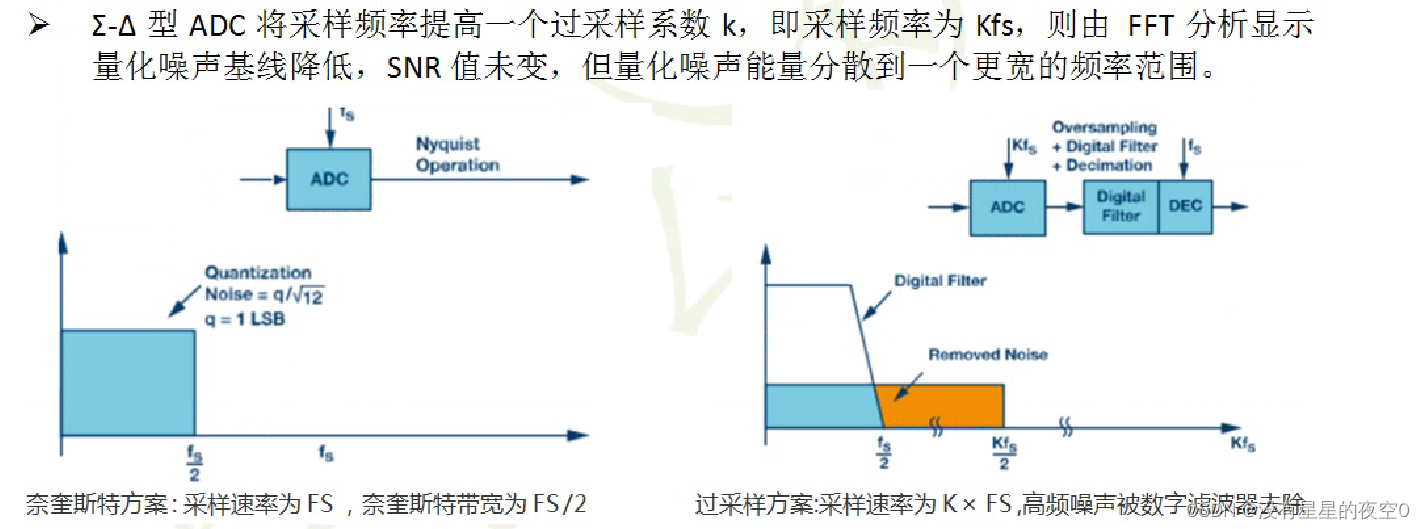

4、Σ-Δ 型(Delta-Sigma ADC)

原理:Sigma-delta ADC的工作原理是将输入信号连续地通过一个Σ-Δ(sigma-delta)调制器进行调制,再通过数字滤波器把高频调制噪声滤除,最后通过一个采样保持电路进行采样,实现模拟信号到数字信号的转换。

优点:可在较低分辨率下获得高精度的结果。

缺点:转换速度慢,需要更高的时钟频率和更高的系统性能。

运用:用于音频、视频、加速度计以及温度测量等领域。

实际上,对于Sigma-delta ADC的理解可以通俗的认为是多次采样进行平均以达到更高的精度,比如我们采样1V的电压,可能当前的12bit精度不够,但是我们可以采样1000次,这样累加的电压1000V进行量化,然后在平均获得的精度会更高。

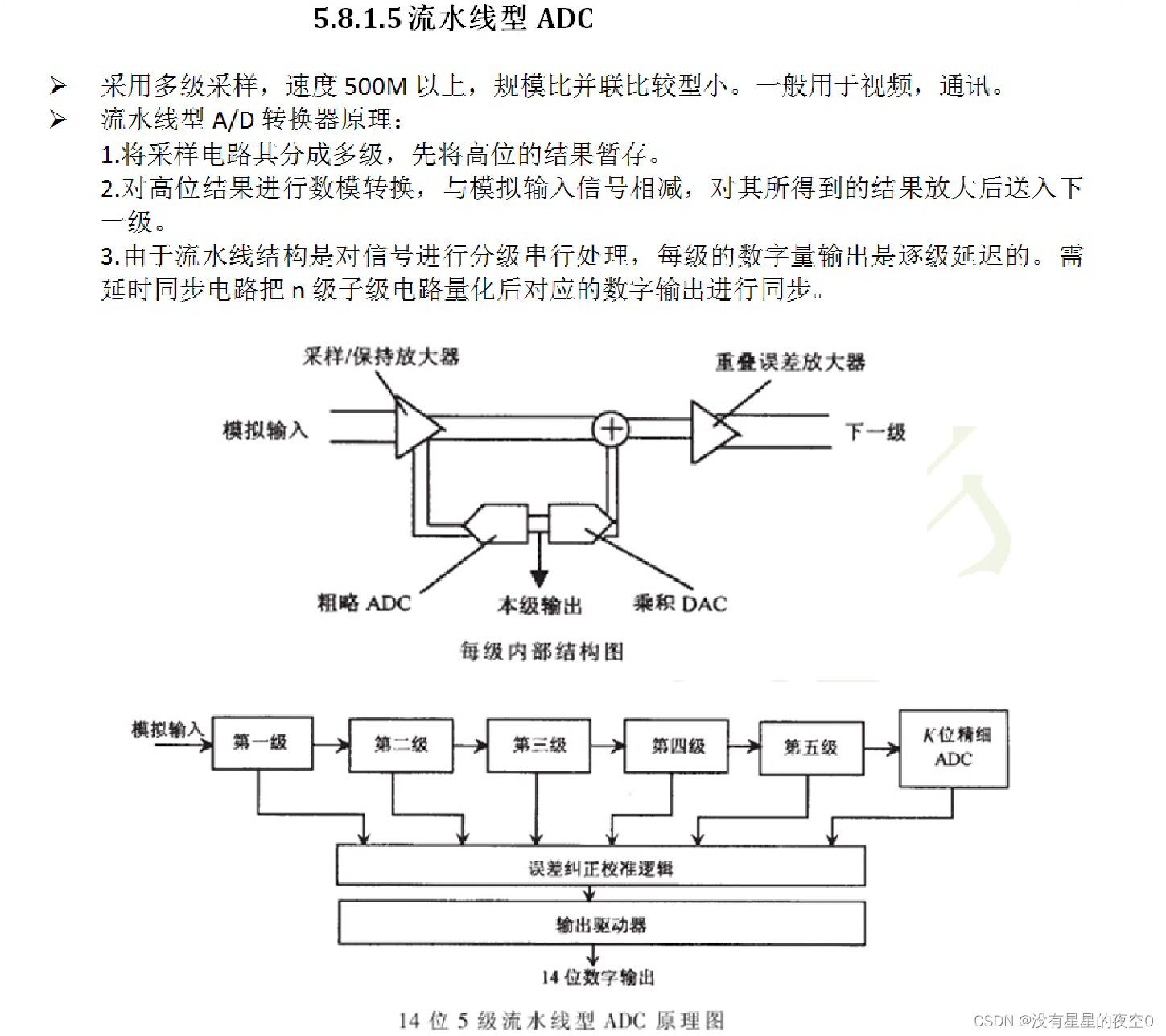

5、流水线型(Pipeline ADC)

原理:Pipeline ADC是一种高速ADC,它采用多级管线结构,将整个ADC转换过程分为多个单元阶段,每个单元阶段负责对前一级的输出进行处理和采样,并输出到后一级。由于每个单元阶段只需要处理部分位数,因此可以大幅提高转换速度。

优点:高精度、高速的模拟信号转换。

缺点: Pipeline ADC在设计实现时较为复杂,而且由于多级采样和量化误差噪声的传递,最终输出的数字化信号可能会受到比较强的噪声干扰,因此需要进一步处理这些干扰以实现更高的信噪比。

运用:工业、通信系统、医疗电子、航空航天等领域得到广泛应用

三、ADC基本规格参数

快速参考数据:

1、量程(full-scale range,FSR)

ADC量程指的是允许输入的模拟信号范围。

ADC选型前需要明确被测信号的量程范围,根据需求选择合适的ADC。如果被测信号幅值范围过大或者包含负压,需要根据情况考虑在ADC前级增加运放电路调整量程范围或者增加偏置。实际使用时,最好使被测信号位于ADC量程中央。

2、分辨率(Resolution)

分辨率是ADC最基本的参数,可以用表示每个模拟信号值的位数(二进制)来表示。一个4位ADC能表示16个不同的模拟信号值,因为2的4次方是16。位数越多,转换的精度越高,分辨率也就越大。注意,ADC的精度并不仅仅取决于分辨率。分辨率和精度不成正比,主要受失真和噪声的影响。

有效分辨率:如规格手册上表示可以达到12位,但受限于噪声有效位数可能只有11位。所以实际选型时,需要对规格书所声明的分辨率进行降额。

分辨率和传输速度成反比。

ADC常见的分辨率有8位、10位、12位、16位、24位等。

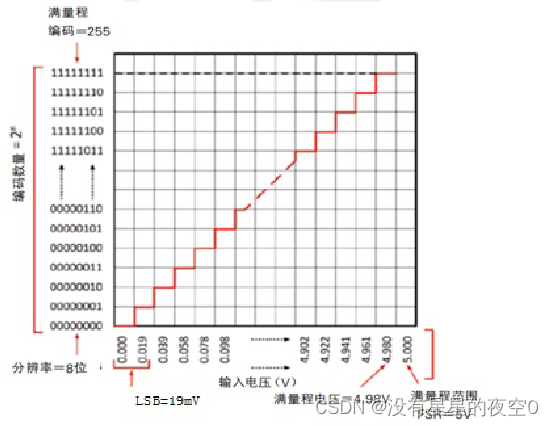

3、最低有效位(One least significant bit,LSB)

又称最小分辨率,满量程值除以ADC的分辨率就是LSB。

LSB=FSR/2N

![]()

其中:FSR为量程范围,N为分辨率位数。

比如说一个4位的ADC,数字量最高可以表示2的4次方也就是16,假设满量程5V,那么最小的分辨率就是5/16=0.31V,也就是说这个ADC最小辨认的电压是0.31V,可以用数字量0001表示0.31V这个模拟量。LSB越小表明ADC的精度越高。

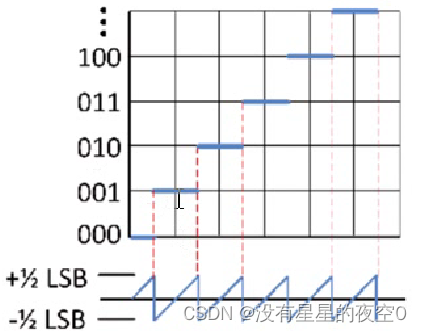

下图纵坐标是数字量编码,横坐标每一个台阶就代表LSB。

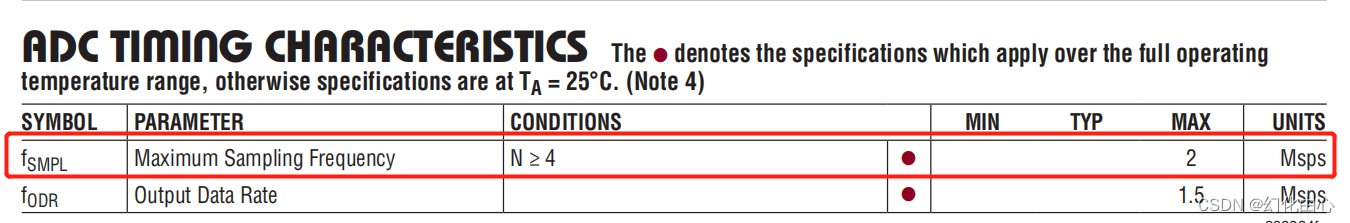

4、采样率(Sampling Frequency)

这里说的采样速率就是我们最高的ADC采样频率,也就是数据手册中的Maximum Sampling Frequency。ADC的采样速率选型时常用单位是 ksps 和 Msps,表示每秒 采样千/百万次(kilo / Million Samples per Second)。

根据奈奎斯特采样定理,ADC采样频率必须位被测信号频率的两倍;在一般实际应用中应保证采样频率为信号频率的2.46~4倍;如果想采集到比较完整的波形,ADC采样频率最好在被测信号的5~10倍。

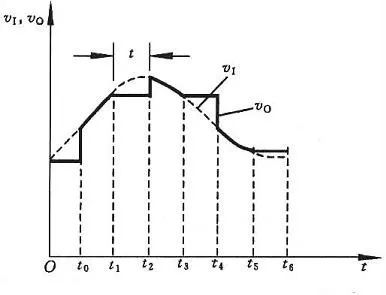

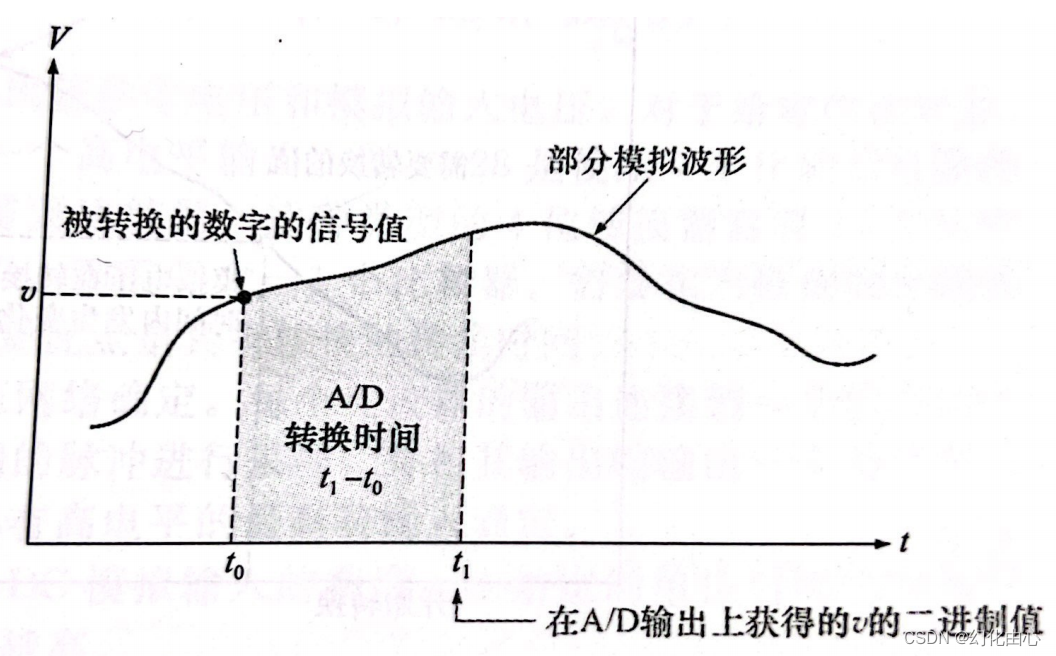

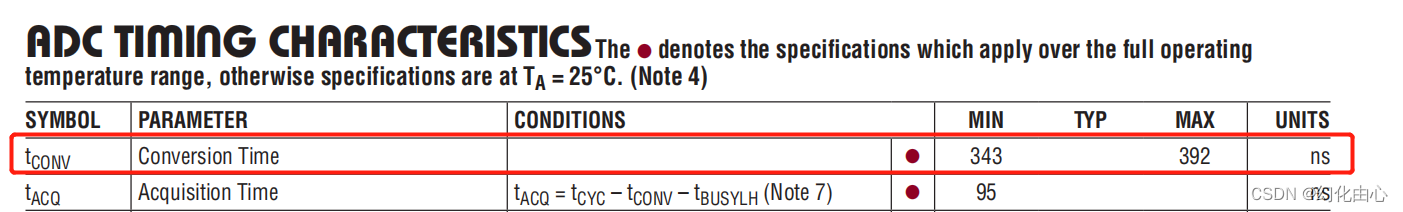

5、转换时间(Conversion Time)

转换时间的导数就是转换速率。因为将一个模拟信号值转换成一个数字量不能瞬间完成,这个过程需要一定的时间。为了保证转换的正确完成,ADC的采样速率必须小于转换速率。

下图说明了转化时间的基本概念,在t0时刻进行模拟电压值的转换,但是直到t1时刻才完成转换。

积分型 AD 的转换时间是毫秒级属低速 AD,逐次比较型 AD 是微秒级属中速 AD,全并行/ 串并行型 AD 可达到纳秒级。转换时间是衡量一个ADC是不是高速的主要指标,高速ADC转换时间小于1us,低速ADC转换时间大于300us。

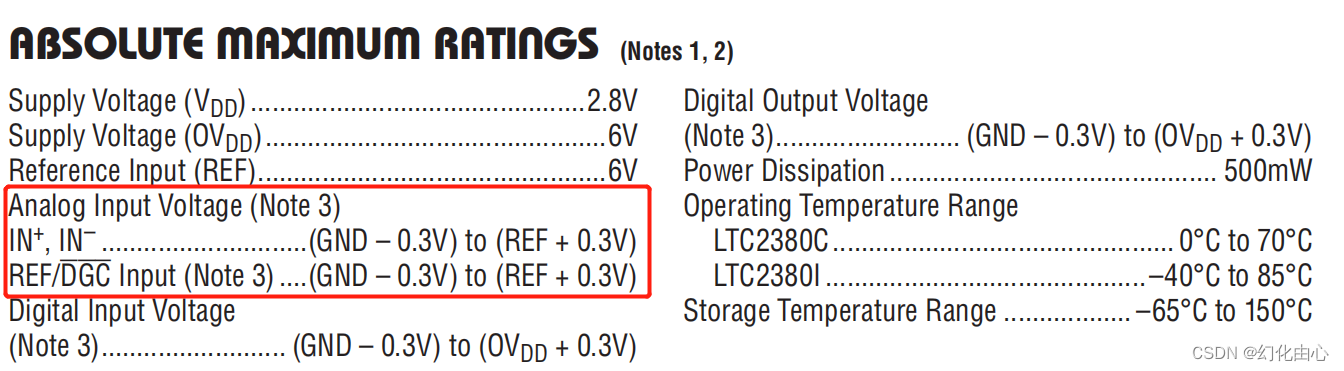

6、参考电平(Vref)

基准电压有内、外基准和单、双基准之分,需要根据精度、温飘等需求来选择。

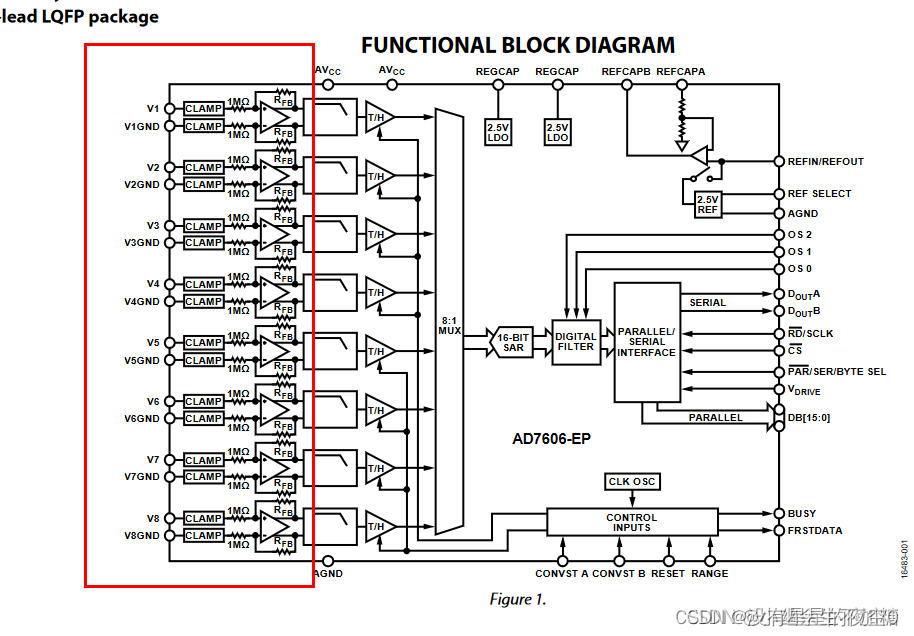

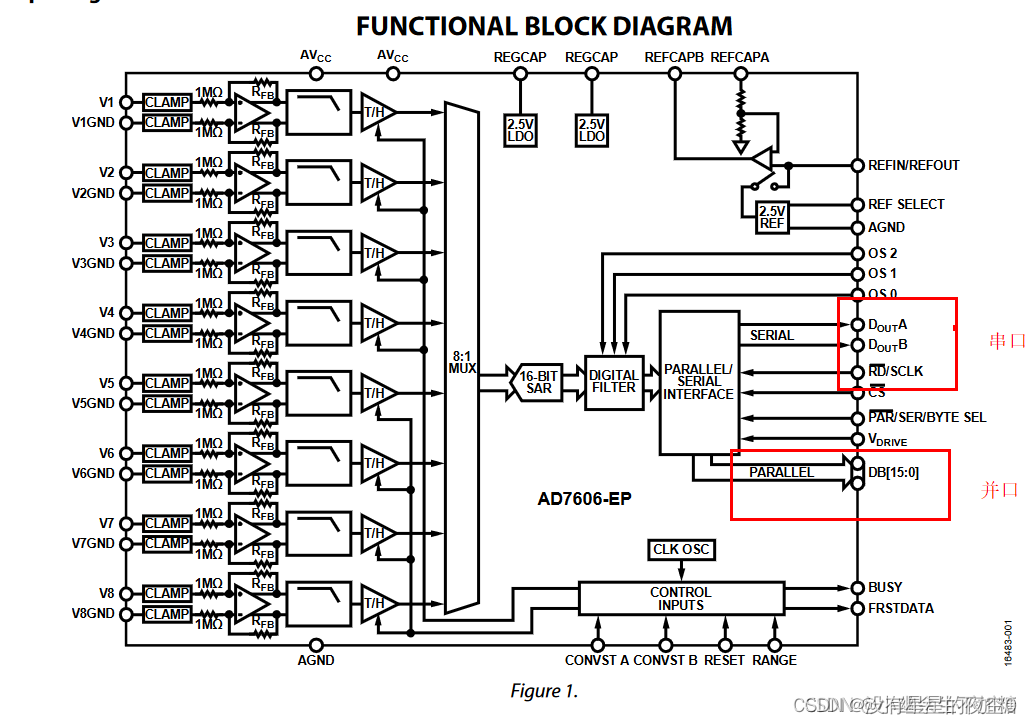

7、通道数和接口

通道数:同时允许多少通道进行转换。

实际使用时不仅要考虑通道数,还要考虑是单端通道还是差分通道:如果是多个通道,是同步采样吗;如果是差分通道,是否可以互换,另一通道是否可以接地;除此之外,还需要根据被测信号数量、成本、应用场景等进行综合考虑选择。

接口:接口类型有三种,串口,并口、高速并口。串口有一般是SPI、I2C等不同标准。那么如何选择呢,并口软件开发简单,软件开发成本小一些,但是占IO口多,占用大量MCU资源,所以在IO资源紧缺的情况下尽量避免选择并口的ADC芯片;串口开发成本高一点,但是占用IO资源少,IO资源不足的情况下,可以考虑选择串口通讯的ADC芯片。

现在市面上大多部分ADC芯片串口和并口的通讯方式都集成了,那可以根据项目实际的需求选择合适的通信方式。

其他指标:

一、静态指标

1、误差

1.1量化误差(Quantizing Error)

由于AD的有限分辨率而引起的误差,即有限分辨率 AD 的阶梯状转移特性曲线与无限分辨率 AD(理想 AD)的转移特性曲线(直线)之间的最大偏差。 通常是一个或半个最小数字量的模拟变化量,表示为1LSB、½LSB。量化误差属原理误差,它是无法消除的。A/D 转换器的位数越多,各离散电平之间的差值越小,量化误差越小。

1.2偏移误差(offset error)

偏移误差又叫做失调误差,是输出编码为0时的理想输入模拟量与实际输入模拟量的偏差。

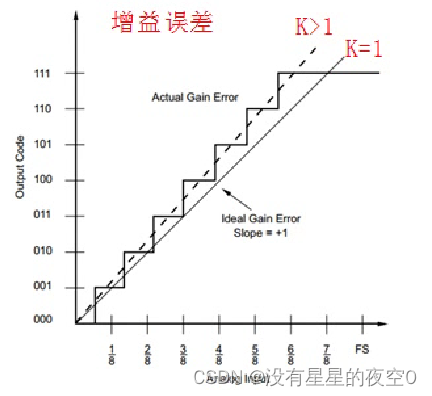

1.3增益误差(gain error)

增益误差是指输出量化阶梯曲线的直线斜率与理想输出之间的误差。

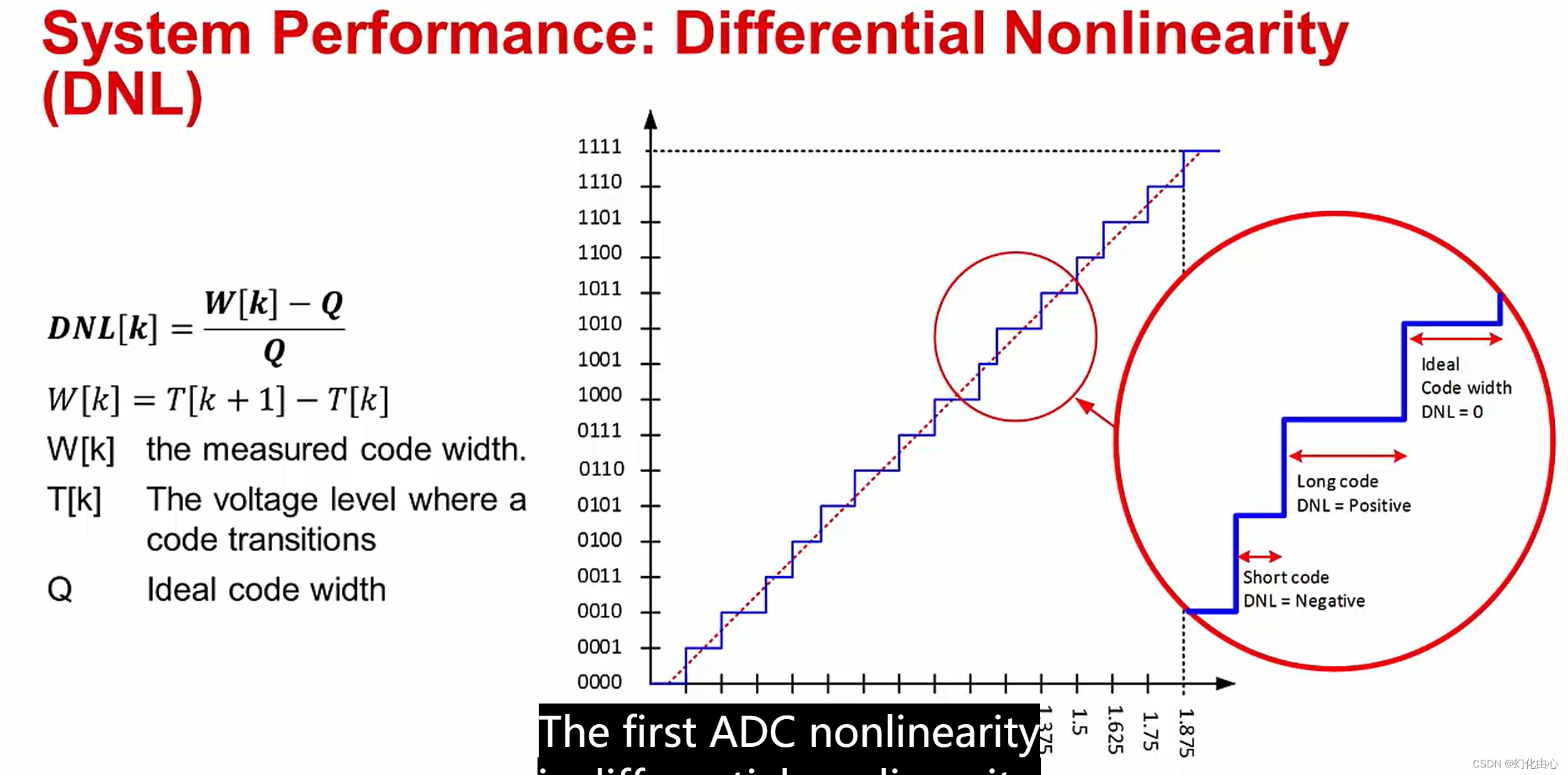

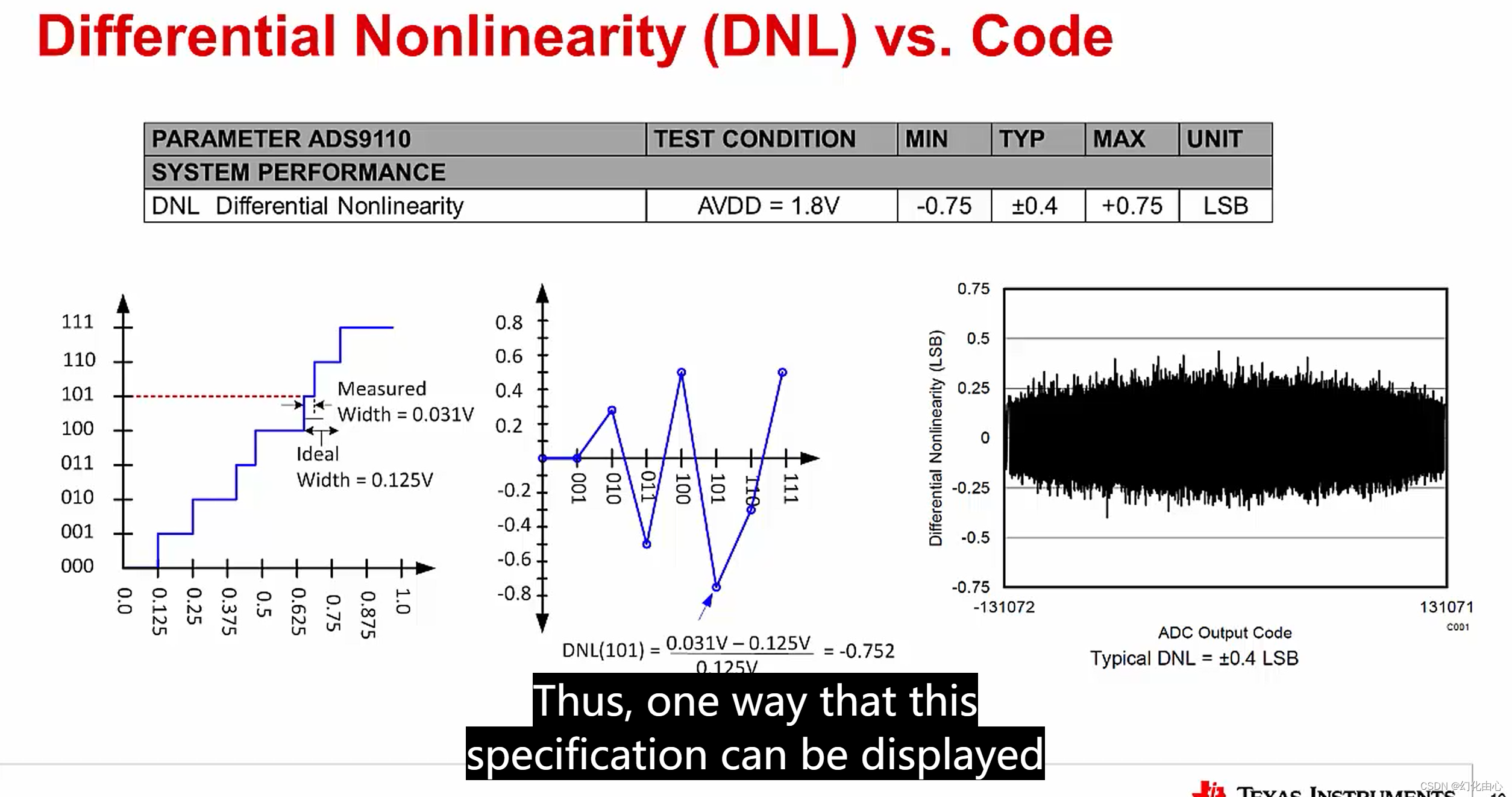

2、差分非线性度(Differential nonlinearity,DNL)

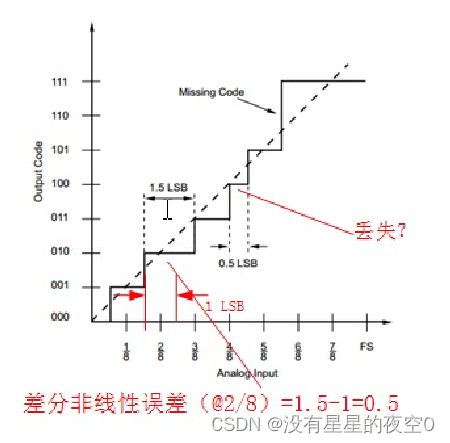

对于ADC,触发任意两个连续输出编码的模拟输入电平之差(即ADC相邻刻度)应为1 LSB (DNL = 0),实际电平差相对于1 LSB的偏差被定义为DNL。(局部非线性)。

用通俗易懂的语言来描述这个DNL特性就是说,理论上我们用数字量的台阶去给模拟电压值进行编码的时候,台阶的宽度应该都是一样的,也就是说当ADC输入和输出是呈线性关系的时候,每次模拟输入按照最小分辨率LSB进行步进的时候,数字输出就增加1,也就是0000变成0001的一个过程。但是由于DNL,导致可能当数字输出由1000变成1001的时候,模拟值的变化却不是按照LSB进行增长的,可能会多一点也可能少一点,下图描述了这种现象。

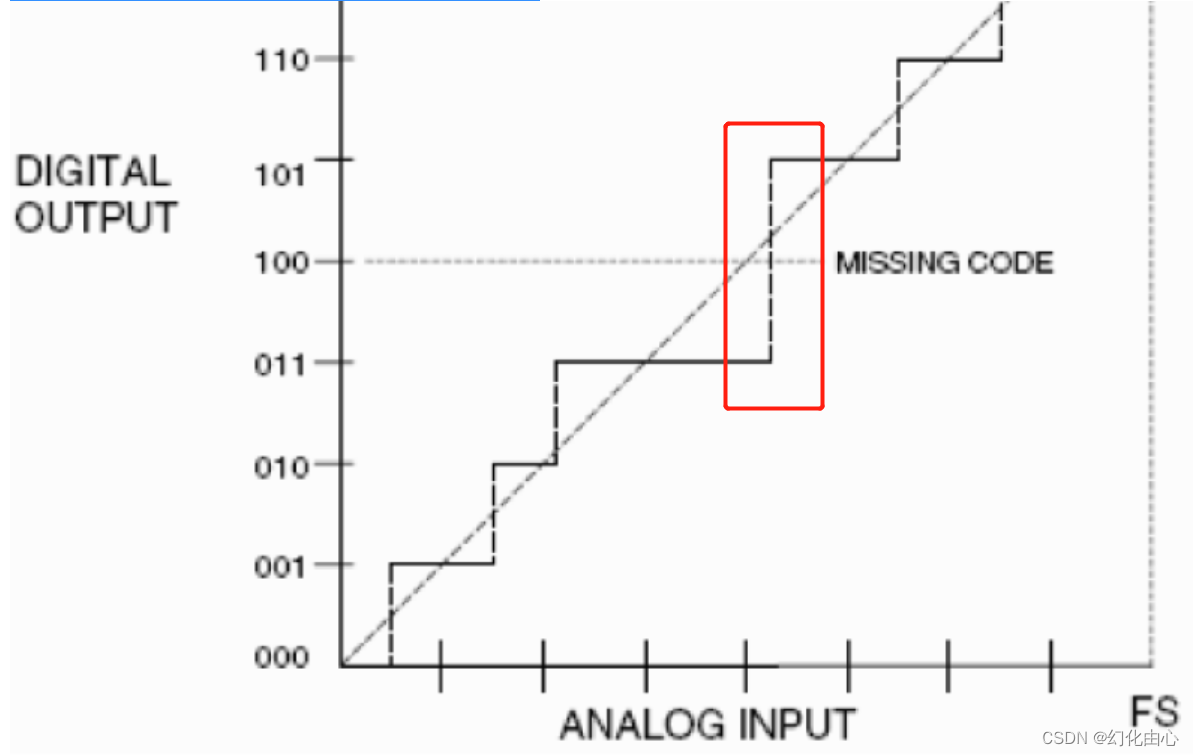

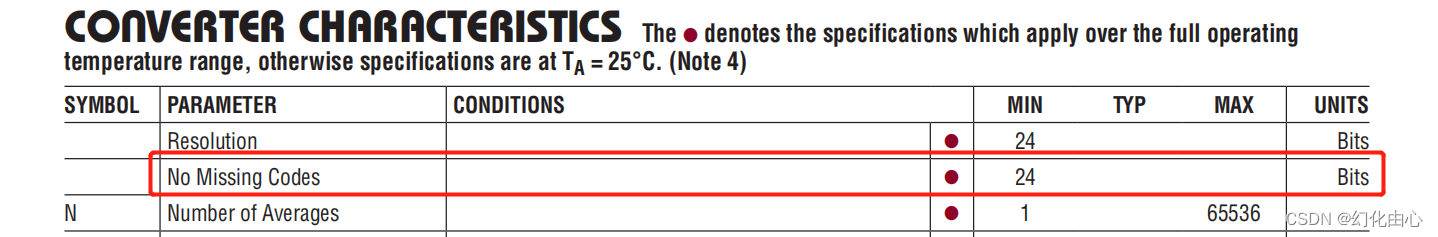

3、无丢码(no missing code)

ADC在实际情况下能够输出量程范围内的所有输出编码。

根据DNL的特性,我们来假设一下最坏的情况,就是某一时刻由于DNL误差导致正向多了0.5LSB,下一个时刻负向少了0.5LSB,可能会导致编码时丢码,如下图所示。

那么很多的ADC都会有一个NMC参数(No Missing Codes)就是不丢码的范围,保证不会出现DNL这种导致丢码的极限情况。

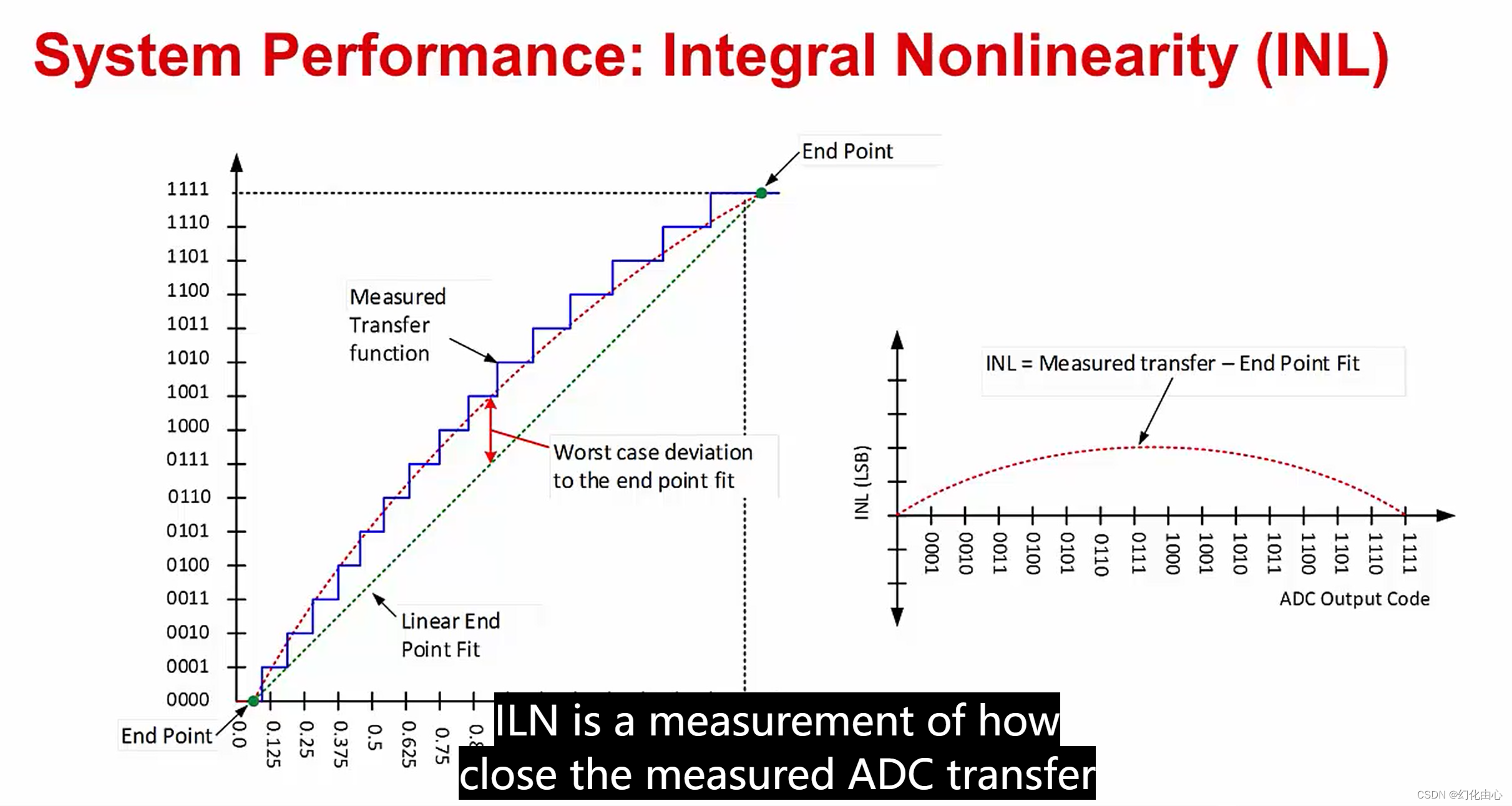

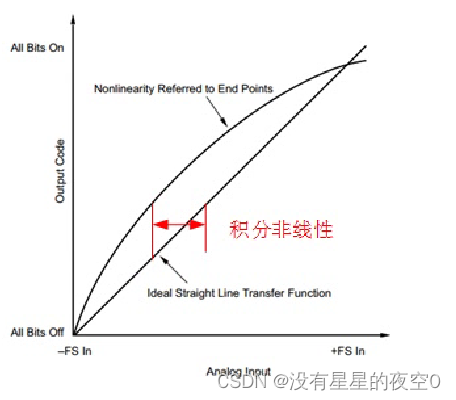

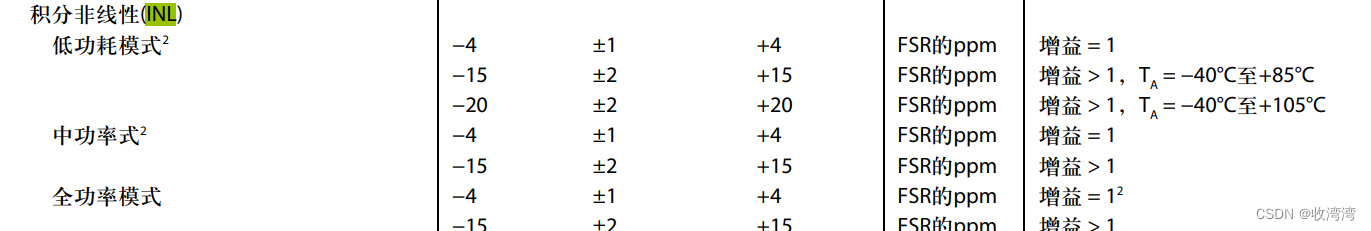

4、积分非线性度(INL)

积分非线性度是差分非线性度的代数和,即输出数值偏离线性最大的距离(累积,整体非线性)。

积分大多跟累计误差有关,根据实际的模拟出一条曲线。INL是指ADC器件在所有的数值点上对应的模拟值和真实值之间误差最大的那一点的误差值,表示测量值的绝对误差。下图绿色虚线所示用的表示理想曲线方法是两点法,就是把头和尾用直线连起来。红色虚线是根据实际的情况模拟出的曲线,找到两个曲线纵坐标差距最大的点。

积分非线性的参数表示如下图所示:

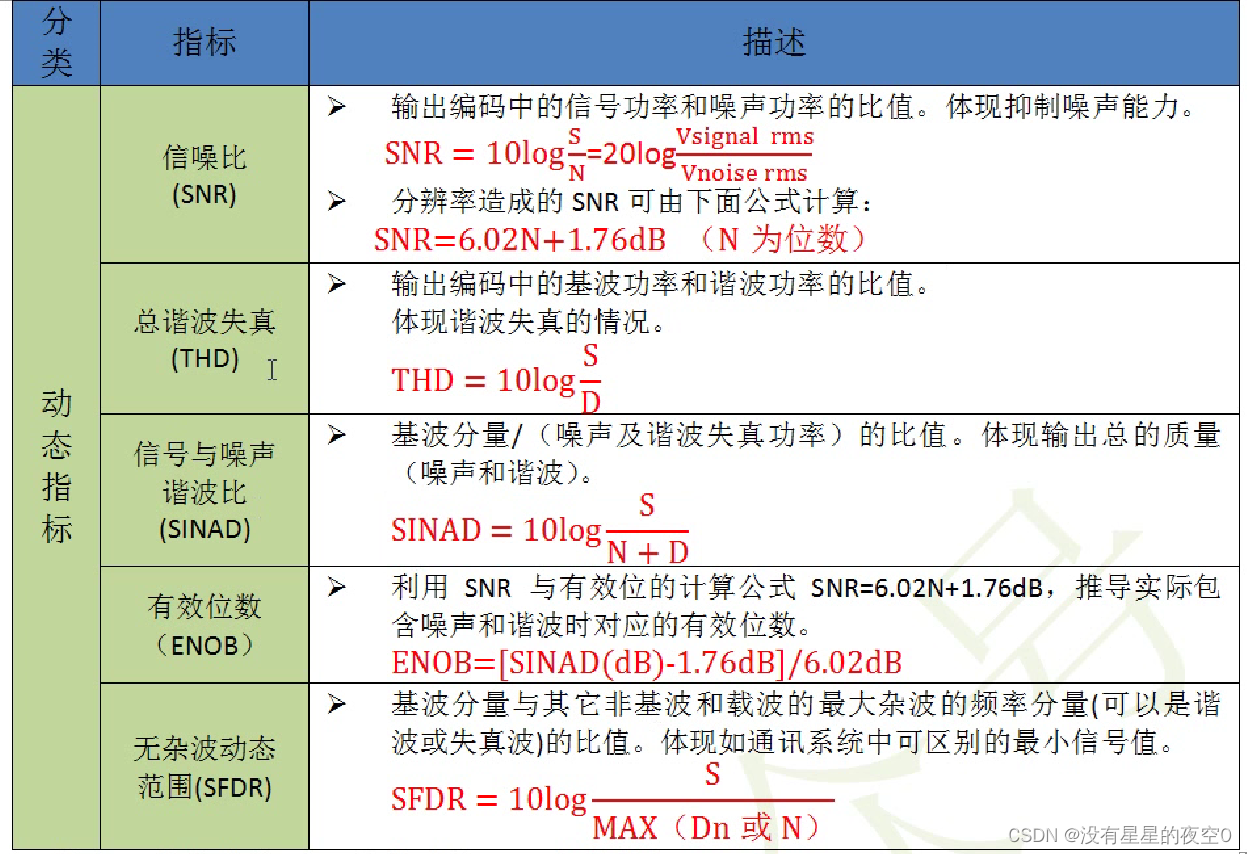

二、动态指标

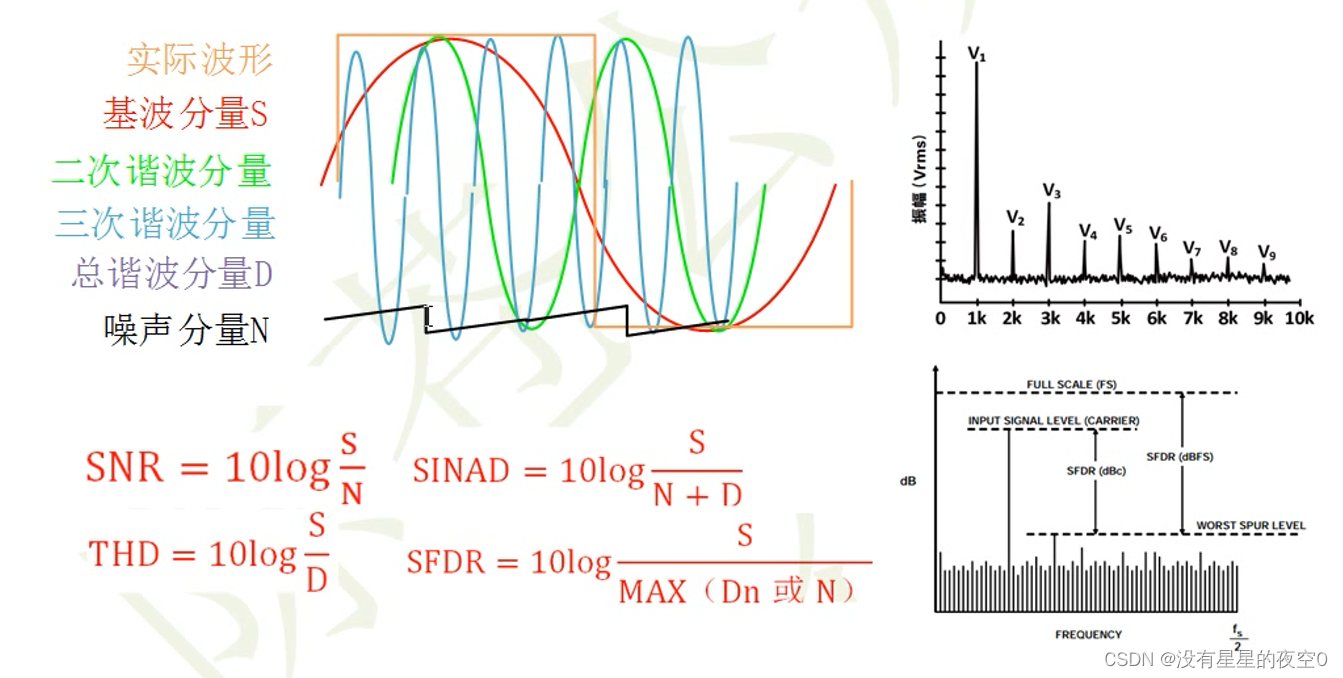

1、信噪比(SNR)

输出编码中的信号功率和噪声功率的比值。体现抑制噪声能力。

SNR=10logS/N=20log Vsignal rms / Vnoise rms

![]()

分辨率造成的SNR可由下面公式计算:

SNR=6.02N+1.76dB

![]()

上式中N为位数。

ADC的SNR受许多因素影响,包括分辨率(Resolution),线性度(Linearity)和精度(Accuracy)(量化级别与真实模拟信号的匹配程度),混叠(Aliasing)和抖动(Jitter)。ADC的SNR通常通过有效位数(ENOB)来表示,理想的ADC的ENOB等于其分辨率。量化误差的存在限制了理想ADC的SNR。一般认为,若ADC的SNR超过输入信号的SNR,则可认为输出的数字信号是对模拟输入信号的无失真数字表示。

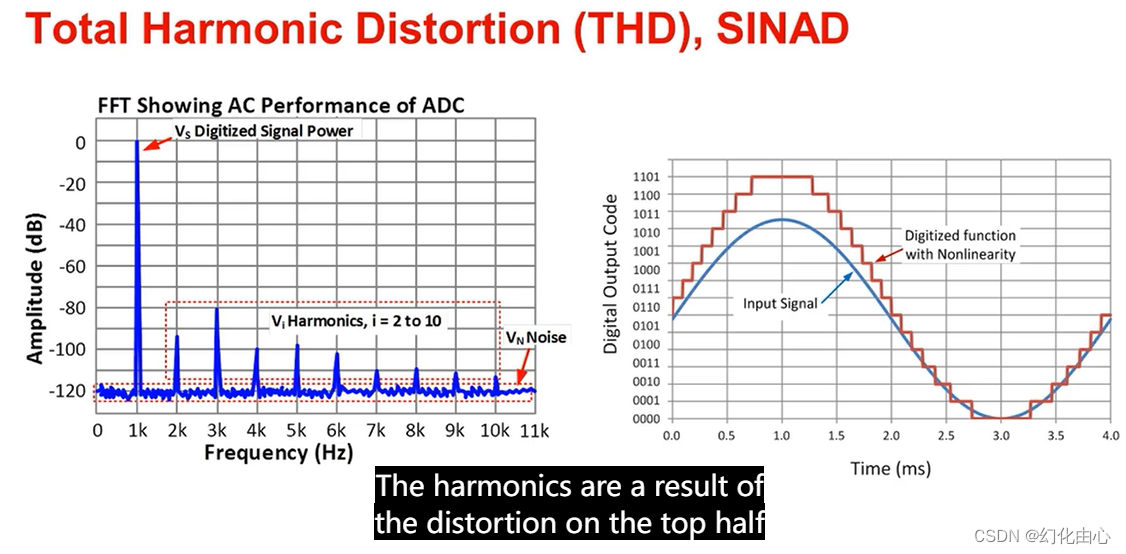

2、总谐波失真(THD)

这个参数比较常见,输入信号与系统所有谐波的总功率比。指输出信号比输入信号多出的谐波成分,体现谐波失真的情况。

THD=10logS/D

![]()

谐波失真是系统不完全线性造成的。所有附加谐波电平之和称为总谐波失真。总谐波失真与频率有关。一般说来,1000Hz频率处的总谐波失真最小。ADC输出中的谐波失真是由ADC特性中存在的任何非线性引起的。每个实用的ADC都具有非线性特性。结果,每个实际ADC的输出中都存在谐波。DNL和INL是ADC特性非线性的量度,而THD是ADC输出中产生的谐波失真的量度。

3、信号与噪声谐波比(SINAD)

简称信纳比,是基波分量与噪声及谐波失真功率的比值。SINAD能很好的反映ADC的整体动态性能。

SINAD=S+N+D/N+D

![]()

4、有效位数(ENOB)

切勿将有效位数(ENOB)与有效分辨率混为一谈,ENOB是包括了量化噪声和失真项,有效分辨率仅用于衡量ADC在无量化噪声的直流输入条件下的噪声。

ENOB=SINADdB-1.76dB/6.02dB

![]()

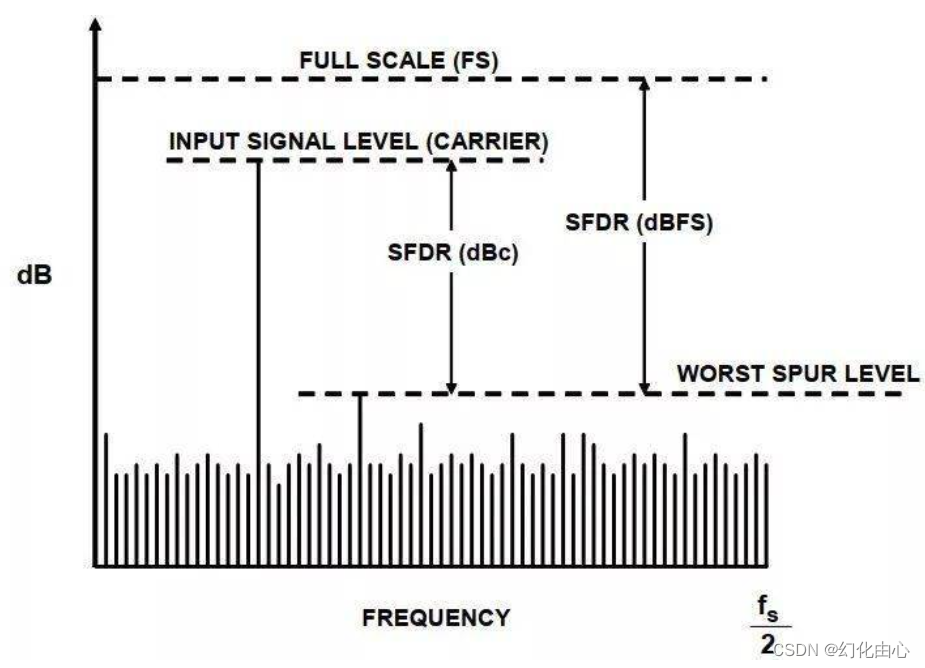

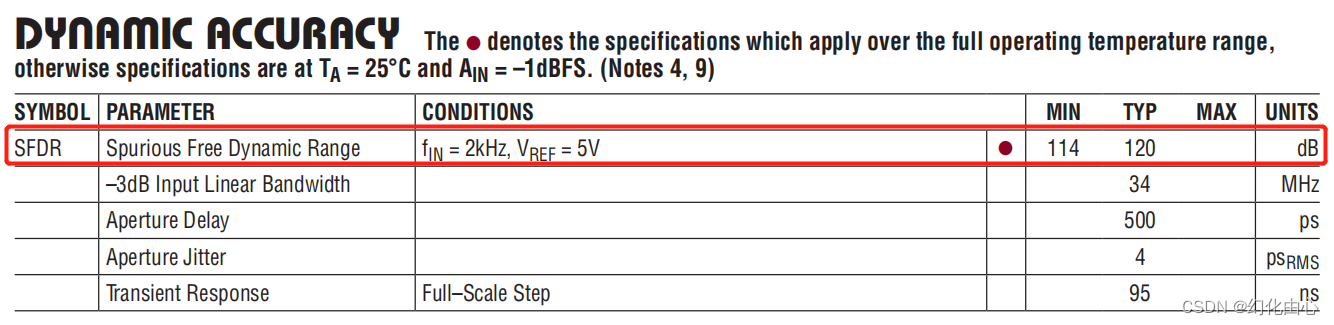

5、无杂波动态范围(SFDR)

英文全称是 Spurious-Free Dynamic range,意为无杂散动态范围,是基波分量与其他非基波和载波的最大杂波的频率分量(可以是谐波或失真波)的比值,反映了FFT分析频谱中信号幅值与最大谐波的距离关系。所以SFDR值越大则说明系统的噪声水平越低,ADC的动态性能越好。单位dBc是相对于载波频率幅度,dBFS是相对于ADC满量程范围。

SFDRdBC=基本信号幅度-最大杂散幅度

![]()

实际使用中,无杂散动态范围表明模数转换器在输入大信号的同时所能检测到的最小信号的能力。当ADC用在过采样率很高或者转换器的频谱性能很重要的情况下,无杂散动态范围的指标是标志系统性能的一个很重要的参数。

对于高速ADC,若要最大程度地提高SFDR,存在两个基本限制:第一是前端放大器和采样保持电路产生的失真;第二是ADC编码器部分的实际传递函数的非线性所导致的失真。提高SFDR的关键是尽可能降低以上两种非线性。

参考

1、陈苍硬件

2、模数转换器(ADC)选型参考指南_adc选型-CSDN博客

上传的文章为工作学习过程中的个人资料总结,欢迎各位同行交流指正

//因为是以前总结的,有很多前期参考的文章(文献)已无记录,如有冒犯请联系//

487

487

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?