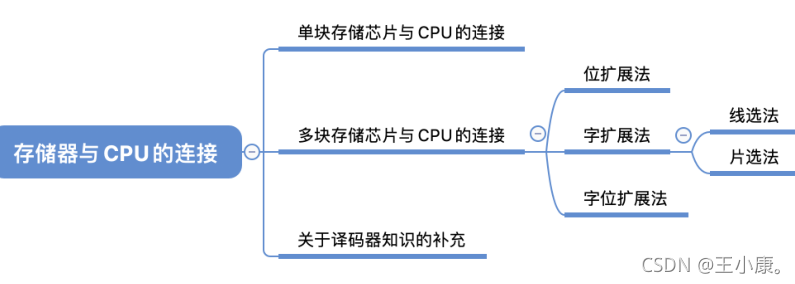

408计算机组成原理学习:存储器与CPU

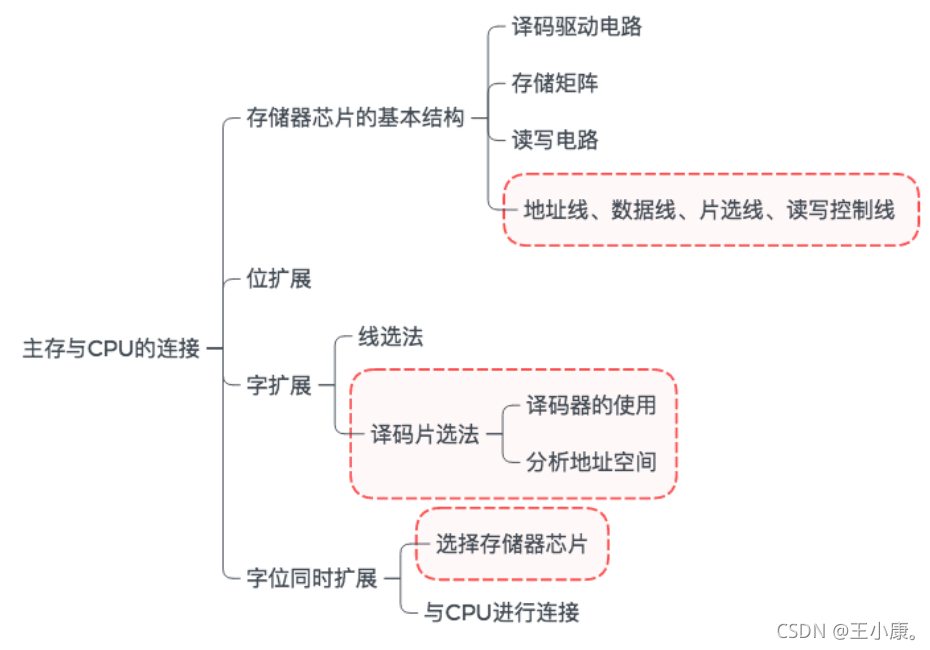

主存储器与CPU的连接

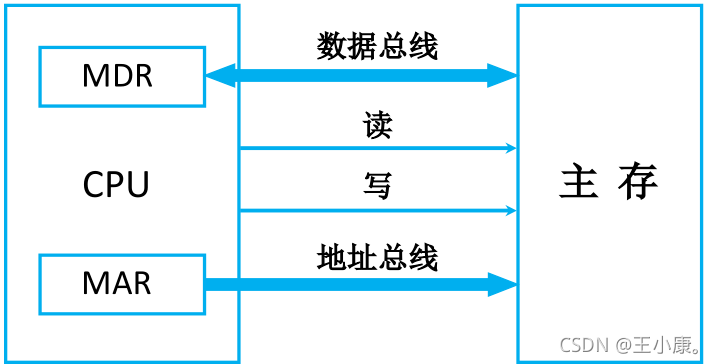

现在的计算机MAR、MDR通常集成在CPU内部。存储芯片内只需一个普通的寄存器(暂存输入、输出数据)

想要扩展主存字数怎么办?——字扩展

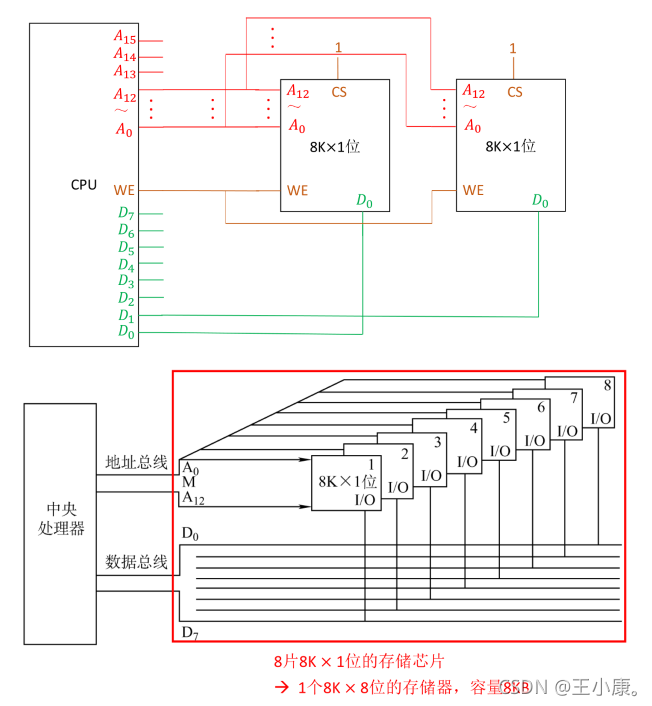

数据总线宽度>存储芯片字长,怎么办?——位扩展

主存中包含多块存储芯片

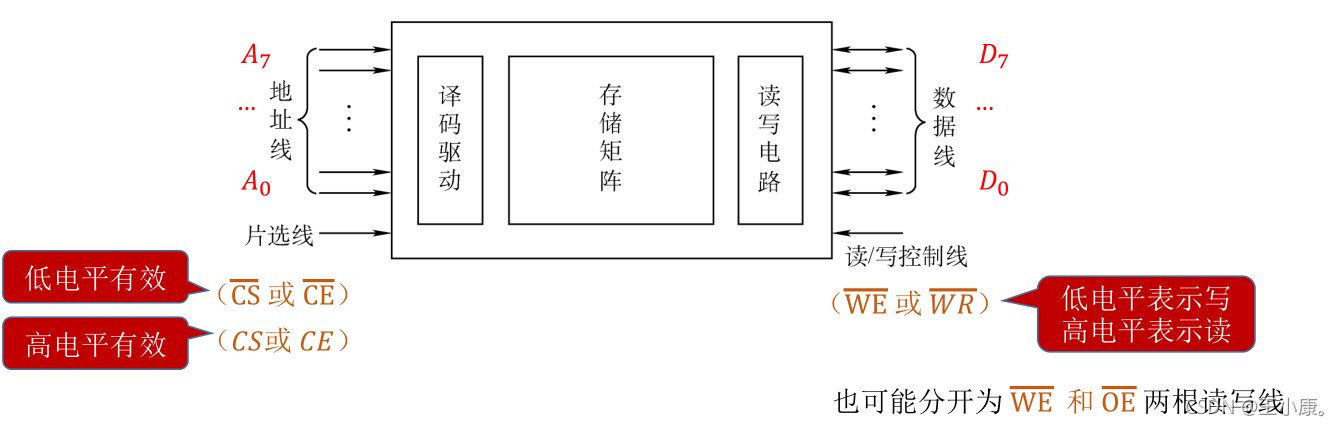

WE = Write Enable

增加主存的存储字长 - 位扩展

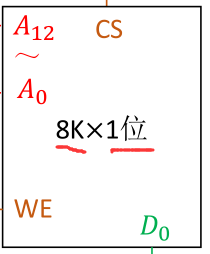

8K = 2^13,故有13根地址线

只有1块1位的芯片,所以每一次主存只能读/写一位的数据,故存储字长为1kb

扩展为:

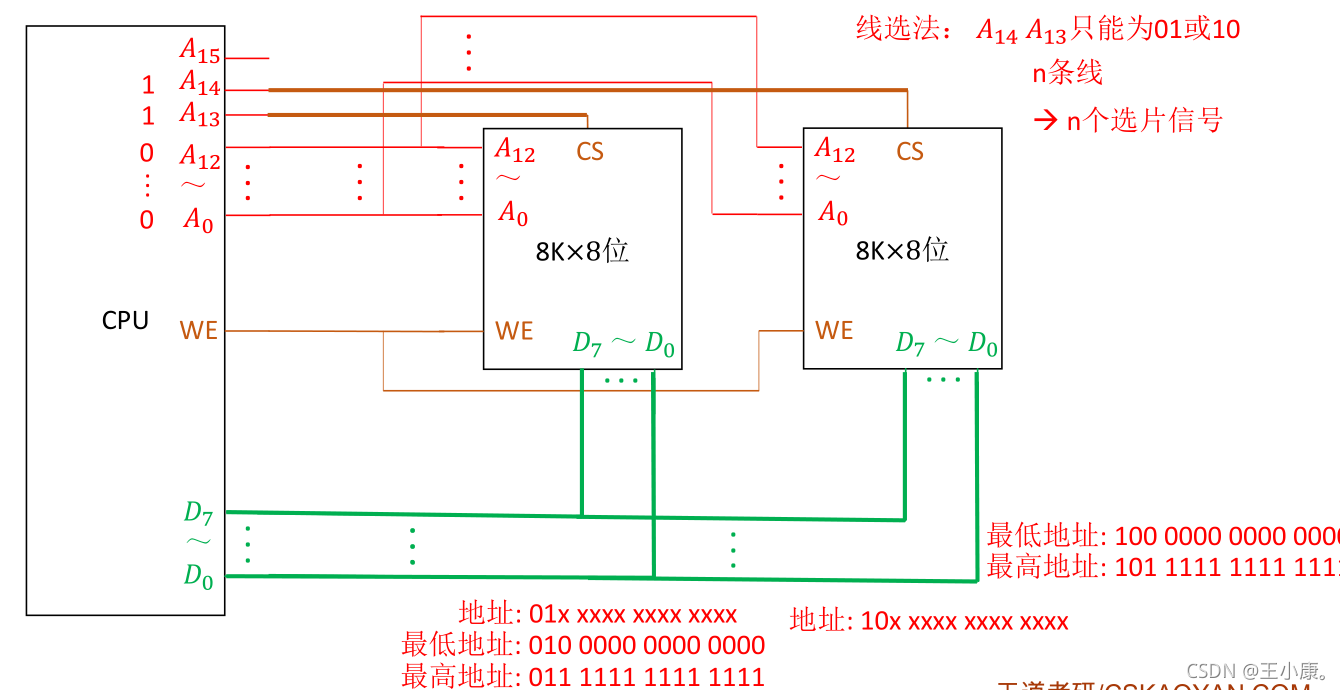

增加主存的存储字数 - 字扩展

通过地址线来选中使用的芯片

限制:芯片不能同时选中,故A14与A13只能为01或10

使用A0到A14共15条地址线

选中第一片芯片的话:

地址: 01x xxxx xxxx xxxx

最低地址: 010 0000 0000 0000

最高地址: 011 1111 1111 1111

选中第二片芯片的话:

地址: 10x xxxx xxxx xxxx

最低地址: 100 0000 0000 0000

最高地址: 101 1111 1111 1111

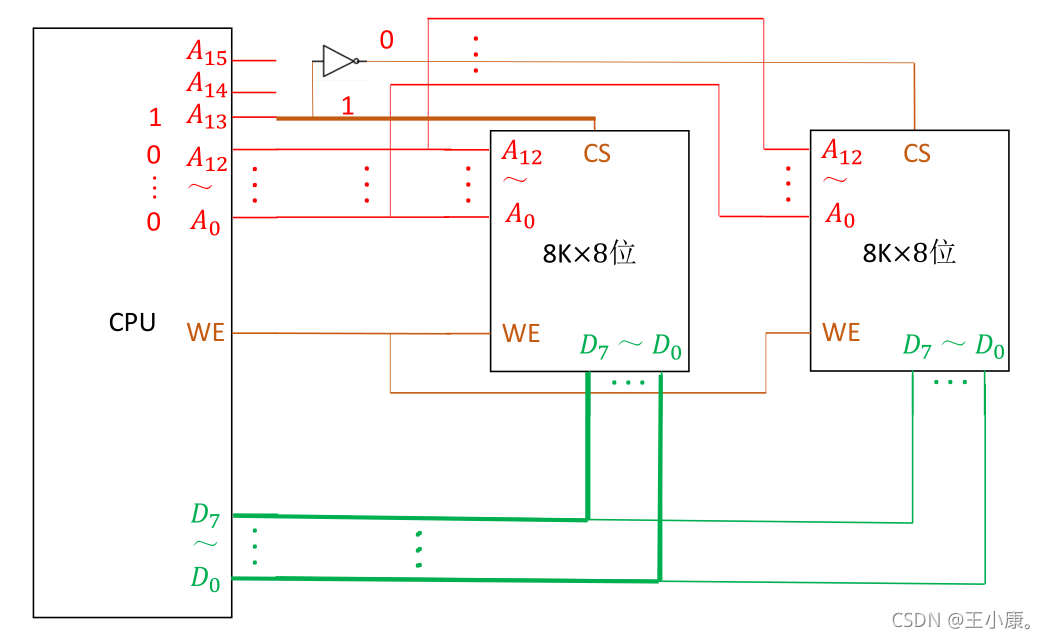

通过使用非门进行优化(使用一条地址线来选择芯片):

使用A0到A13共14条地址线

选中第一片芯片的话:

地址: 1x xxxx xxxx xxxx

最低地址: 10 0000 0000 0000

最高地址: 11 1111 1111 1111

选中第二片芯片的话:

地址: 0x xxxx xxxx xxxx

最低地址: 00 0000 0000 0000

最高地址: 01 1111 1111 1111

这种为1-2译码器(1条线,2=2^1两个选片信息)

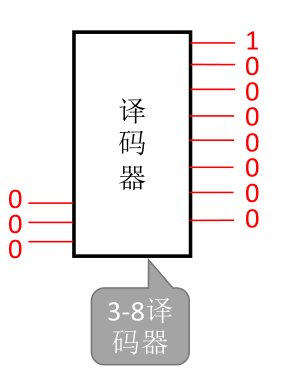

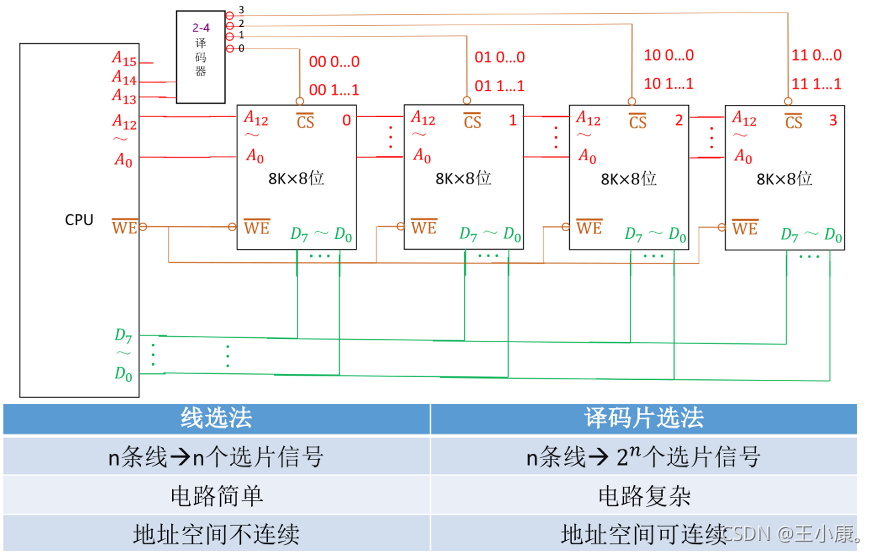

译码片选法:

n条线

-> 2^n 个选片信号

根据左边的000来选择右边的第几条线(第几个芯片)

3-8译码器(3条线,8=2^3八个选片信息)将A13到A15地址线都使用了

根据选片信息不同,选择不同的芯片

Eg:

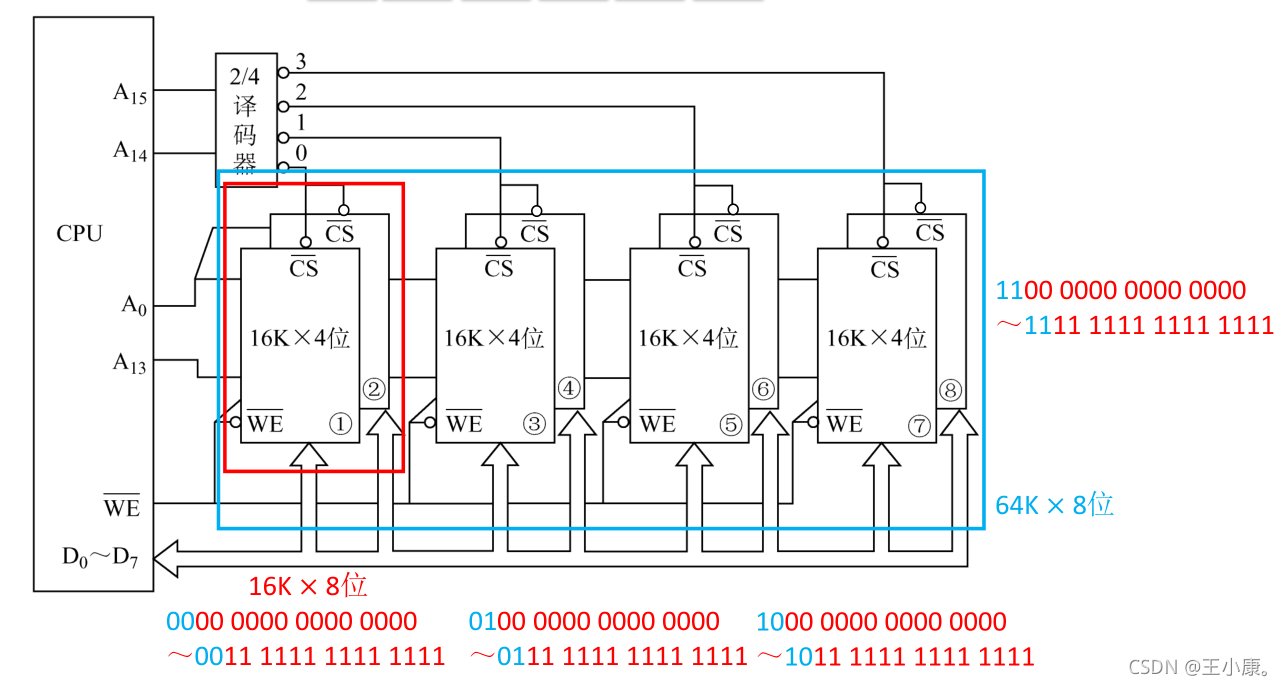

主存容量扩展 - 字位同时扩展

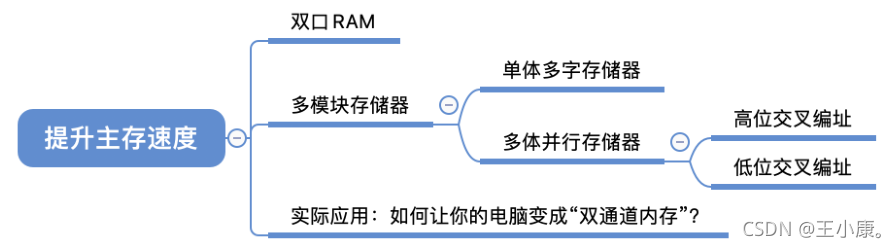

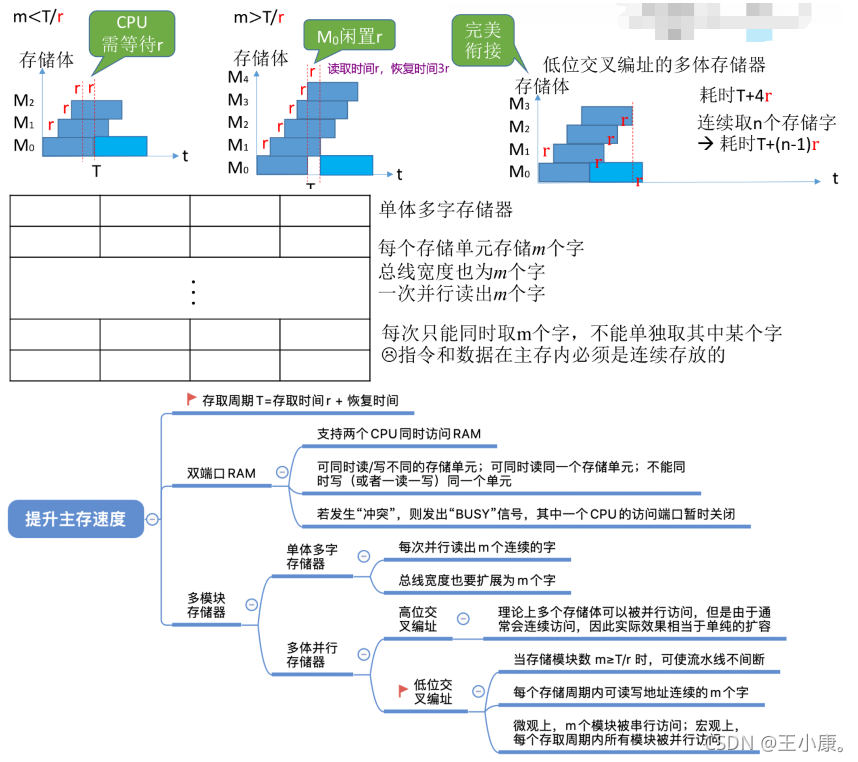

双口RAM&多模块存储器

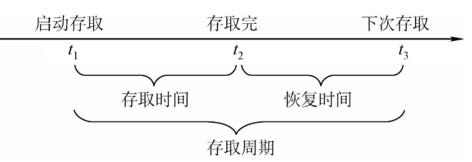

存取周期:可以连续读/写的最短时间间隔

DRAM芯片的恢复时间比较长,有可能是存取时间的几倍(SRAM的恢复时间较短)

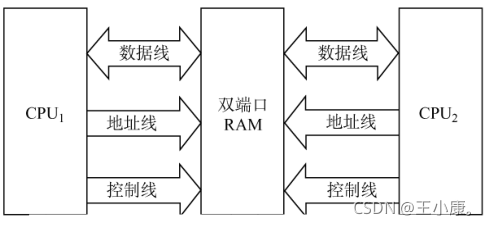

双端口RAM

作用:优化多核CPU访问一根内存条的速度

需要有两组完全独立的数据线、地址线、控制线。CPU、RAM中也要有更复杂的控制电路

两个端口对同一主存操作有以下4种情况:

- 两个端口同时对不同的地址单元存取数据。 正常

- 两个端口同时对同一地址单元读出数据。 正常

- 两个端口同时对同一地址单元写入数据。 写入错误

- 两个端口同时对同一地址单元,一个写入数据,另一个读出数据。 读出错误

解决方法:

置“忙”信号为0,由判断逻辑决定暂时关闭一个端口(即被延时),未被关闭的端口正常访问,被关闭的端口延长一个很短的时间段后再访问。

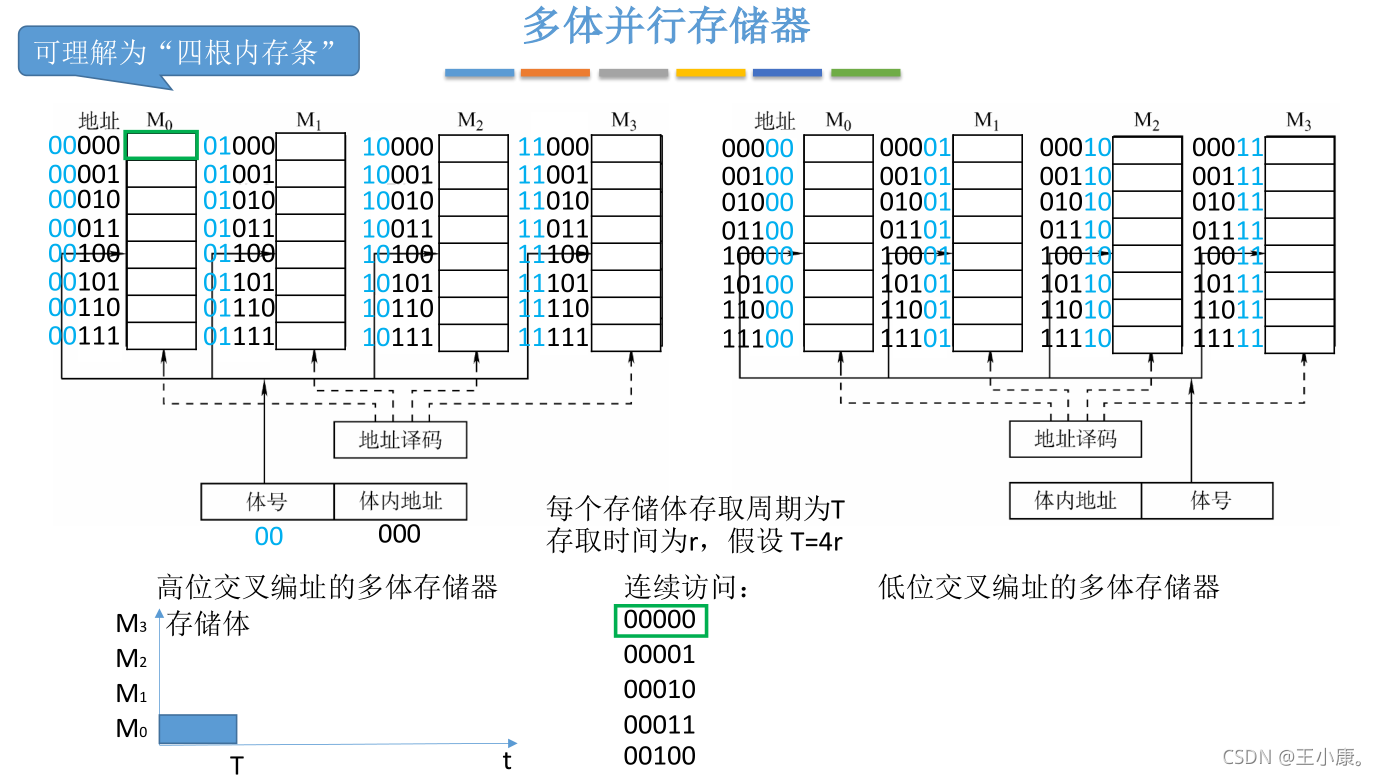

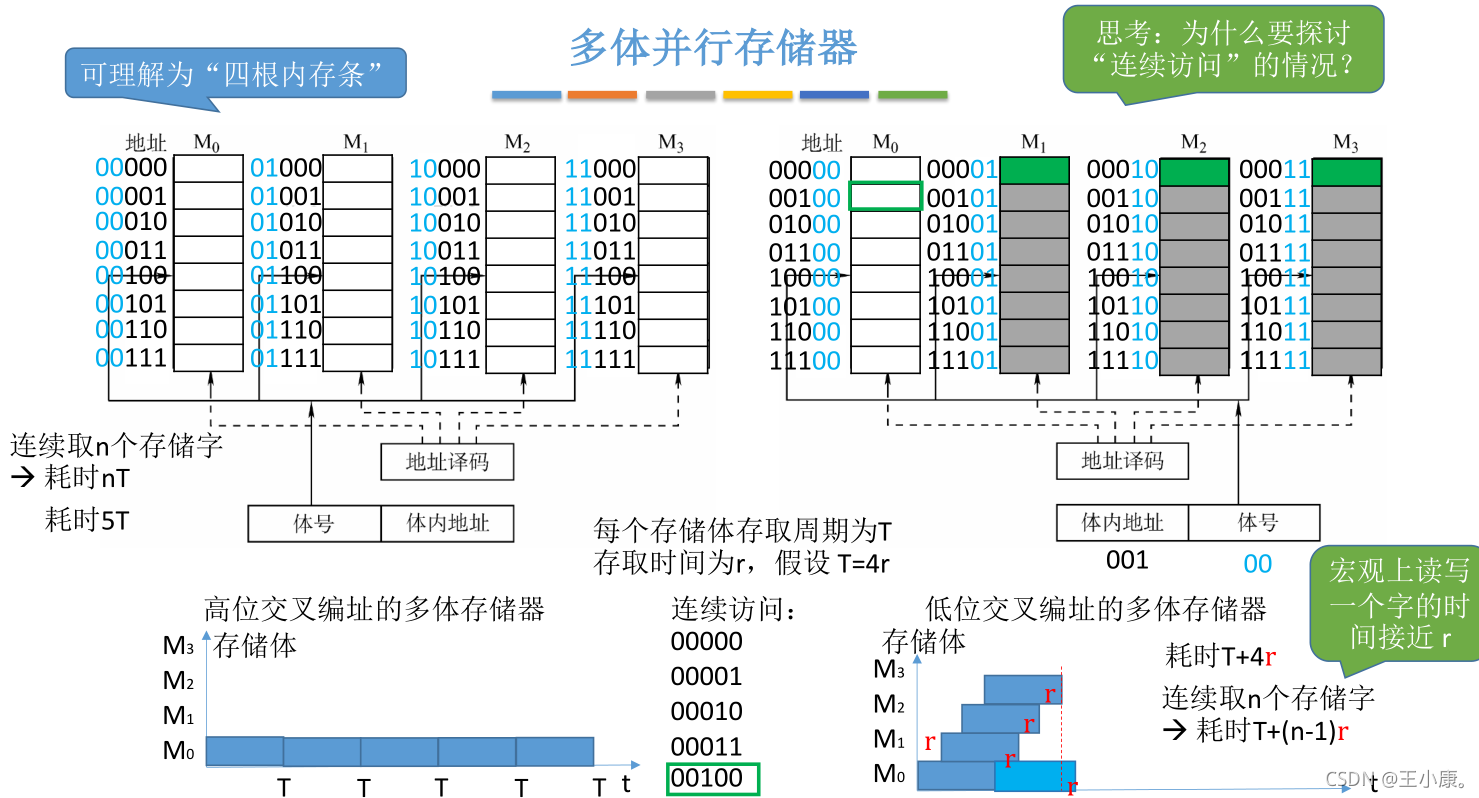

多体并行存储器

通过使用体号来选择使用哪一个存储体

高位与地位的连续访问不同

采用“流水线”的方式并行存取(宏观上并行,微观上串行)

宏观上,一个存储周期内,m体交叉存储器可以提供的数据量为单个模块的m倍。

存取周期为T,存取时间为r,为了使流水线不间断,应保证模块数 m≥T/r

存取周期为T,总线传输周期为r,为了使流水线不间断,应保证模块数 m≥T/r

如何插入内存条,实现高位交叉的多体存储器(相当于单纯的扩容)?

如何插入内存条,实现低位交叉的多体存储器(俗称“双通道”)?

Tips:买内存条时,可挑选相同主频、相同容量的两根来组成双通道

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?