目录

注:此文为网上内容的归纳整理,尊重原创作者!

阶跃

阶跃实质上是一种频率响应法的理想频率信号激励源。

----------------------

阶跃电压

由小到大的升压波形,一般实际使用如软启动器,就是使用的0-380V阶跃电压。

Q:什么是阶跃电压?

A:在极短的时间内电压从 0 上升到 V。稳定在 V 一段时间后又在极短时间内回到 0

电压在这个极短的时间内进行上升,又在这个极短的时间内下降,可以看作是频率很高的电压。阶跃电压连接放大电路进行放大,为确保电压上升部分不产生失真,那么放大电路需要有很高的频率响应。

-------------------------------------

阶跃电压法

就是在MOS电容上加一个阶跃电压后,测量MOS电容随时间的弛豫过程,即测量MOSC-t曲线,对所测得的C-t曲线进行数据处理,求得产生寿命。

通过分析耗尽的阶跃电压作用下的C-t瞬态特性方程,提出了确定产生寿命的计算简单的新方法。2理论分析考虑一个n-Si衬底的MOS电容器,在加脉冲前处于平衡强反型模式。在其上加一耗尽的阶跃电压后,该器件将立即进入深耗尽态,同时在空间电荷区中形成了一个载流子的净产生区。

出处:http://bbs.ntpcb.com/read.php?tid-116855.html

在建立ADC输入和通过优化带宽限制噪声时所需的最小RC值,可以由假设通过指数方式建立阶跃输入来计算。

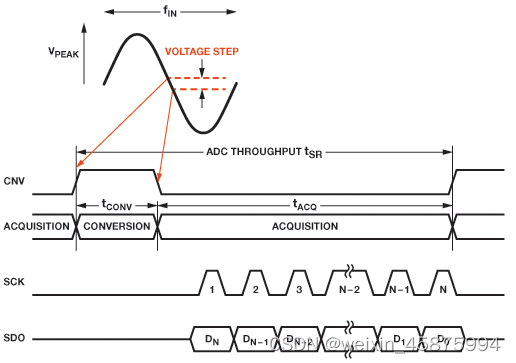

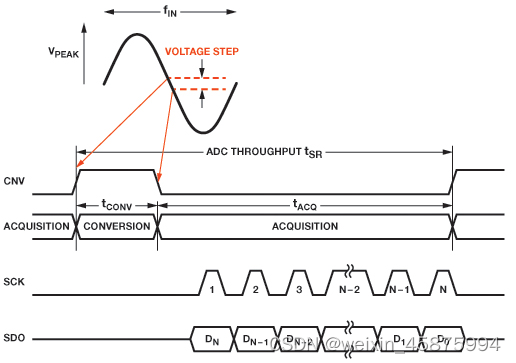

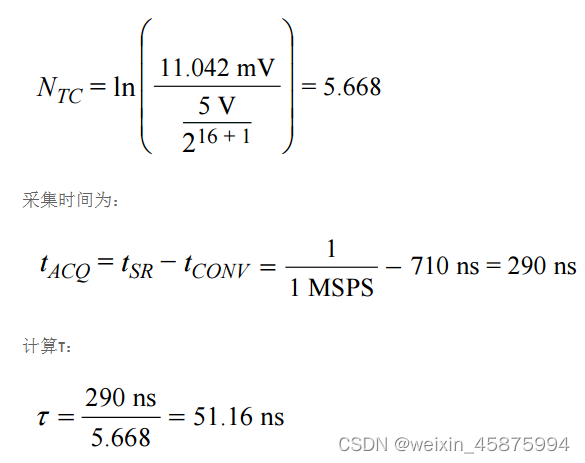

要计算阶跃大小,需要知道输入信号频率、幅度和ADC转换时间。转换时间, tCONV(图2)是指容性DAC从输入端断开并执行位判断以产生数字代码所需的时间。转换时间结束时,保存前一样本电荷的容性DAC切换回输入端。此阶跃变化代表输入信号在这段时间的变化量。此阶跃建立所需的时间称为 "反向建立时间".

图2. N位ADC的典型时序图

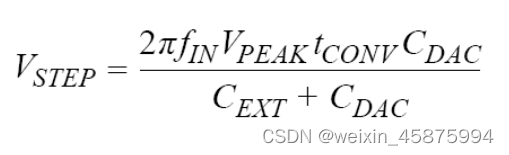

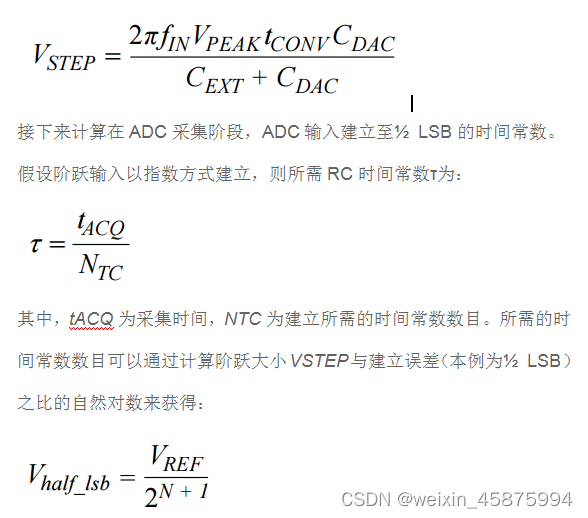

1. 计算出阶跃电压Vstep

参数说明:

①. Vstep-----------阶跃电压

②. Fin--------------信号频率

③. Vpeak----------输入信号峰值,注意是波峰或者波谷,而不是峰峰值

④. Tconv-----------ADC数据转换时间,即转换为数字信号的时间

⑤. Cdac------------ADC内部采样保持电容,在Datasheet中对应于ADC的Cin输入电容

⑥. Cext-------------滤波电容,一般取值Cext=100*Cdac

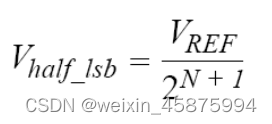

①. Vhalf_lsb---------最低有效位的1/2

②. Vref----------------ADC满量程电压

③. N-------------------ADC位数

5. 根据时间常数=RC公式计算出R

具体举例

在给定输入频率下,一个正弦波信号的最大不失真变化率可通过下式计算:

如果ADC的转换速率大大超出最大输入频率,则转换期间输入电压的最大变化量为:

这是容性DAC切换回采集模式时出现的最大电压阶跃。然后,DAC电容与外部电容的并联组合会衰减此阶跃。因此,外部电容必须相对较大,达到几nF。此分析假设输入开关导通电阻的影响可忽略不计。现在需要建立的阶跃大小为:

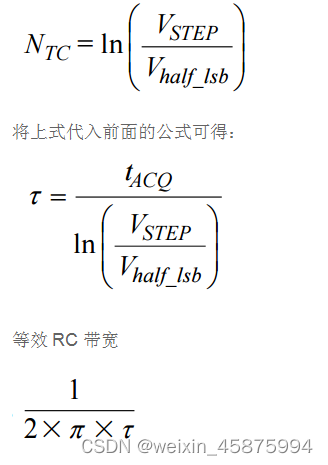

接下来计算在ADC采集阶段,ADC输入建立至½ LSB的时间常数。假设阶跃输入以指数方式建立,则所需RC时间常数τ为:

因此,

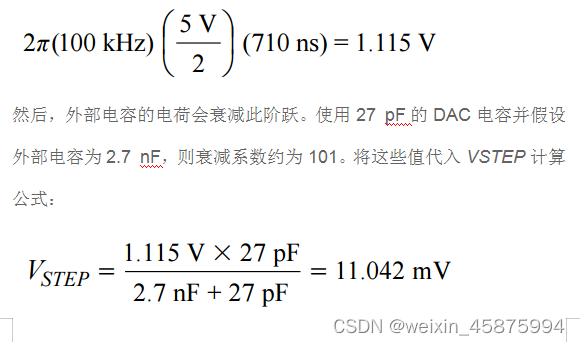

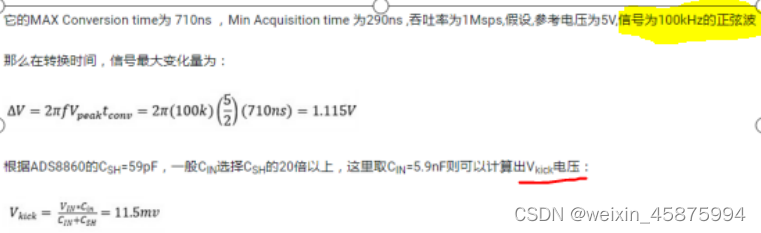

示例:借助RC带宽计算公式,选择16位ADCAD7980 (如图3所示),其转换时间为710 ns,吞吐速率为1 MSPS,采用5 V基准电压。最大目标输入频率为100 kHz。计算此频率时的最大阶跃:

接下来计算建立至½ LSB(16位、5 V基准电压)的时间常数数目:

因此,带宽为3.11 MHz, REXT 为 18.9 Ω.

图3. 采用16位1 MSPS ADC AD7980的RC滤波器

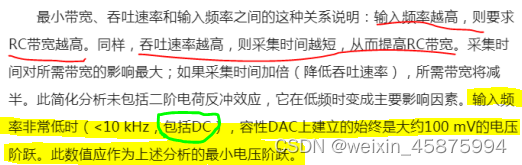

最小带宽、吞吐速率和输入频率之间的这种关系说明:输入频率越高,则要求RC带宽越高。同样,吞吐速率越高,则采集时间越短,从而提高RC带宽。采集时间对所需带宽的影响最大;如果采集时间加倍(降低吞吐速率),所需带宽将减半。此简化分析未包括二阶电荷反冲效应,它在低频时变成主要影响因素。输入频率非常低时(<10 kHz,包括DC),容性DAC上建立的始终是大约100 mV的电压阶跃。此数值应作为上述分析的最小电压阶跃。

多路复用 输入信号很少是连续的,通常由不同通道切换产生的大阶跃组成。最差情况下,一个通道处于负满量程,而下一个通道则处于正满量程(见图4)。这种情况下,当多路复用器切换通道时,阶跃大小将是ADC的满量程,对于上例而言是5 V。

图4. 多路复用设置

在上例中使用多路复用输入时,线性响应所需的滤波器带宽将提高到3.93 MHz(此时阶跃大小为5 V,而非单通道时的1.115 V)。假设条件如下:多路复用器在转换开始后不久即切换(图5),放大器和RC正向建立时间足以使输入电容在采集开始前稳定下来。

图5. 多路复用时序

对于计算得到的RC带宽,可以利用表1进行检查。从表中可知,要使满量程阶跃建立至16位,需要11个时间常数(如表1)。对于计算的RC,滤波器的正向建立时间为11 × 40.49 ns = 445 ns,远少于转换时间710 ns。正向建立不需要全部发生在转换期间(容性DAC切换到输入端之前),但正向和反向建立时间之和不应超过所需的吞吐速率。对于低频输入,信号的变化率低得多,因此正向建立并不十分重要。

表1. 建立至N位分辨率所需的时间常数数目

REXT的值必须能使失真水平保持在要求的范围以内。图6显示了驱动电路电阻对失真的影响与AD7690输入频率的函数关系。失真随着输入频率和源电阻的提高而提高。导致这种失真的原因主要是容性DAC提供的阻抗的非线性特性。

图6. 源电阻对THD的影响与输入频率的关系

低输入频率(<10 kHz)可以支持较大的串联电阻值。失真还与输入信号幅度有关;对于同一失真水平,较低的幅度可以支持较高的电阻值。计算上例中的 REXT in the example above, where τ = 51.16 ns 假设CEXT 为2.7 nF,得到电阻值为18.9 Ω。这些值接近ADI数据手册应用部分给出的常见值。

此处计算的标称RC值是有用的指南,但不是最终解决方案。选择REXT与 CEXT之间的适当平衡点,需要了解输入频率范围、放大器可以驱动多大的电容以及可接受的失真水平。为了优化RC值,必须利用实际的硬件进行试验,从而实现最佳性能。

阶跃函数

阶跃函数是一种特殊的连续时间函数,属于奇异函数。

在电路分析中,阶跃函数是研究动态电路阶跃响应的基础 。

阶跃函数,类似于楼梯似的,1s-2s u=0; 2s-3s u=1 ; 3s-4s u=2 。。。只是简单举例。

该定义式表明,在该函数t<0时,其值为0,;t>0时,其值为1;当t=0时,发生跳变,其值未定,而当t由负值或正值趋近于0时,其值则是确定的,即ε(t=0-)=0,ε(t=0+)=1。阶跃函数可以用来描述开关动作。

阶跃响应

当激励为单位阶跃函数时,电路的零状态响应称为单位阶跃响应,简称阶跃响应。

在给定初始状态下系统的阶跃响应包括当其控制输入是阶跃函数时其输出的时间演变。在电子工程和控制理论中,阶跃响应是在非常短的时间之内,一般系统的输出在输入量从0跳变为1时的体现。应用该函数以及冲激函数可以方便地描述动态电路的激励和响应。脉冲响应是阶跃响应的导数。

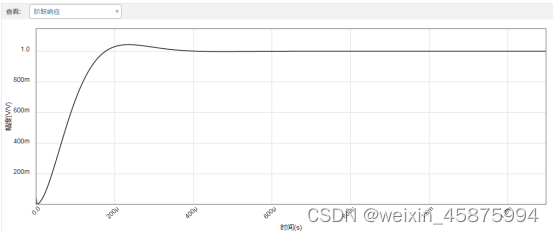

比如下图是有源低通器电路的阶跃响应:

满量程阶跃

多路复用 输入信号很少是连续的,通常由不同通道切换产生的大阶跃组成。最差情况下,一个通道处于负满量程,而下一个通道则处于正满量程(见图4)。这种情况下,当多路复用器切换通道时,阶跃大小将是ADC的满量程

对于计算得到的RC带宽,可以利用表1进行检查。从表中可知,要使满量程阶跃建立至16位,需要11个时间常数(如表1)。对于计算的RC,滤波器的正向建立时间为11 × 40.49 ns = 445 ns,远少于转换时间710 ns。正向建立不需要全部发生在转换期间(容性DAC切换到输入端之前),但正向和反向建立时间之和不应超过所需的吞吐速率。对于低频输入,信号的变化率低得多,因此正向建立并不十分重要。

频率阶跃

频率呈阶层跳跃,在t<0的时候,信号量恒为0,在t>0的时候,信号量恒为1。它是一种理想化的模型,因为在实际中,信号总是连续的,不可能在0点出现这样的“突变”。即“频率的规律变化”单位时间内阶层跳跃所完成振动的次数,是描述振动物体往复运动频繁程度的量,常用符号f或v表示,单位为秒-1。

以下网址是计算ADC阶跃电压的提问

SAR ADC RC滤波器疑问 - 问答 - 精密转换器专区 - EngineerZone

1. 理想目标是使△V小于1/2LSB。

2. 需要建立的阶跃是△V,外部电容充电作用的结果。

--------------------------------------------------------------------------------------

ADC在采样周期时,可能会产生电压阶跃,请问这个电压阶跃是怎么产生的?

这个阶跃主要是外部的滤波电容引起的, 外部的滤波电容一般是内部采用电容额100倍,在保持阶段,内外的电容断开,外部电容随和输入电压变化,当进入采样近端,二者相连,由于电压不同导致电压阶跃。

-----------------------------------------------------------------------------------------------------------

ADC输入为直流时的电压阶跃

ADC电路之前要加信号滤波电路,是减弱无用信号对有用信号的干扰,至于是采用LC还是RC电路看这个滤波电路对输入有用信号的影响大小来确定,一般地如果ADC输入阻抗很大,处理的信号频率低(如直流),选用RC电路又便宜又能达到效果;如果处理的信号频率高,频带宽(如DC-100M),个人意见是可选用LC滤波电路。

如果是直流,理论上就不存在RC取值的上限。但,问题是任何直流都存在上下电的过程,这个过程会随着RC的增加而增长。因此,你必须考虑这个稳态建立时间的容忍度。另外一个“容忍度”是成本和空间。如此,便就有了RC的上限。那下限是什么?这就要看所要滤去的“噪声”频率分布,主要看其频率下限。RC的下限取值为保证按要求滤去噪声的最低频率。可以将RC滤波器的截止频率设计在此频点上,若不够再往下移。

输入为直流时,公式中阶跃电压按100mv算。

输入为交流时,按一下步骤算:

23万+

23万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?