目录

-----------------------------------------------------------------------------------------------

https://www.eefocus.com/szbluefly/blog/16-02/377410_bf21f.html

PCB设计十大误区-绕不完的等长(二) - PCB设计 - 电子工程世界-论坛

https://www.eefocus.com/szbluefly/blog/16-03/377668_59cff.html

注:此文为上述链接内容的归纳整理,尊重原创作者!

----------------------------------------------------------------------------------------------

不同信号时延要求

串行信号在发送端将数据信号和时钟(CLK)信号通过编码方式一起发送,在接收端通过时钟数据恢复(CDR)得到数据信号和时钟信号。由于时钟和信号在同一通道传播,串行信号对和对之间在PCB上传输延时要求较低,主要依靠锁相环(PLL)和芯片的时钟数据恢复功能。

源同步时钟,主要是DDR信号,DQ(数据)信号参考DQS(数据选通)信号,CMD(命令)信号和CTL(控制)信号参考CLK(时钟)信号。DQ是CMD&CTL的2倍。延时要求更高。

影响因素分析:

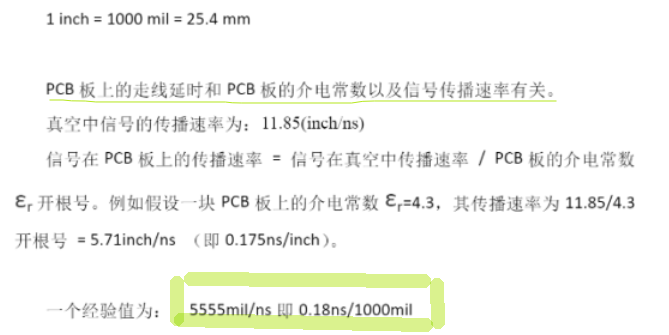

影响PCB中信号传输速度因素: 板材DK(介电常数),信号模式,信号线与信号间耦合以及绕线方式有关。

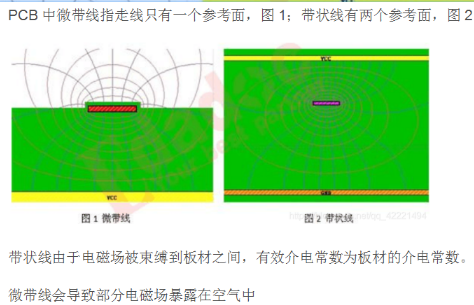

1.微带线和带状线传输延时

微带线的走线延时大约为140ps/inch,带状线的走线延时大约为166ps/inch。

2.走线和过孔传输时延

TD_via=√LC,其中TD_via表示信号经过过孔的时延,L表示过孔的寄生电感,C表示过孔的寄生电容。

对于普通FR4板材的微带线,1.6mm走线传输时延约为11ps,对于带状线约为12.5ps

设计时注意:

1)需要做等长的信号要尽量走同层,换层时需要注意总的长度要保持相等并且每层走线都需要等长。

2) 需要等长的信号走相同走线层可以保持过孔的时延一致,从而消除过孔时延不一致带来的影响。

3.串扰对信号时延的影响

串扰:PCB板上线与线的间距很近,走线上的信号可以通过空间耦合到其相邻的一些传输线上去

设计时注意:

1).拉大线距,走线尽量满足3w原则;

2).耦合长度尽量短,相邻传输线平行走线长度越长串扰越大;走线尽量减小相邻平行线走线长度;对相邻层走线尽量采用垂直走线;

3).走线尽量走带状线,减小串扰影响;

4).保持完整回流平面,避免跨分割,走线和参考面尽量紧耦合;

4.绕线方式

蛇形绕线的信号传输速度会比直线参考线的速度要快,这是由于蛇形绕线靠的太近,平行的耦合长度太长,信号在蛇形绕线上的自耦合导致信号传播速度较快。

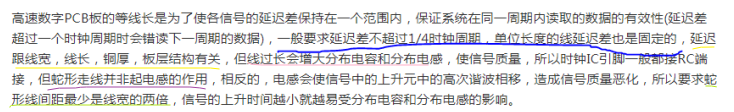

手册看时延 走线长度差要求

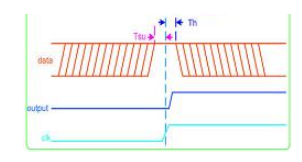

“ 数字电路中高低电平相互翻转的时候是需要时间的,为了保证在接受端电平能被正确的采样,通常会预留一点时间给信号电平建立起来,同样,正确的采样也需要一点时间,就需要信号翻转到某个电平后保持一段时间。这就是所谓的setup time和holdup time。

如上图,左边红色的Ts是setup time,右边Th是holdup time

对于一个导线上传输信号来说最大的时间延迟 Tdelay=Tclk(工作时钟)-Ts-Th。对于多个导线信号传输的情况,如果他们之间的长度差距过长,信号在导线走的路线长短不一样,造成的时延差大过Tdelay,则接收端就会接收错误。

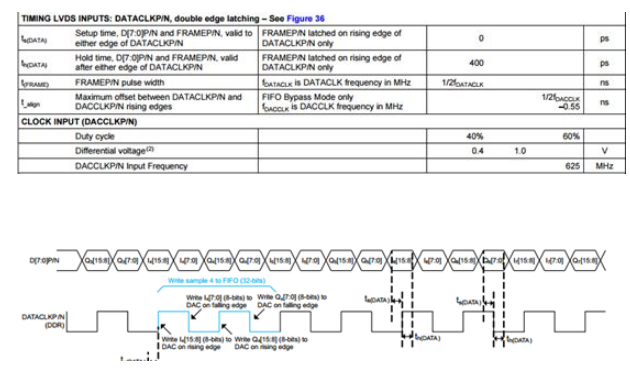

上面两张图是从TI某款DAC芯片手册上截出来的,可以看出这个时钟芯片上升沿和下降沿都是要采样数据的。为什么 Ts时间为0?这是因为该DAC芯片对于数据来说是输入端,自身没有要求,而实际上数据从驱动端到输入端,电平翻转建立是需要时间的,如下图是该DAC芯片自己输出的上升和下降时间(电压从高电平电压的10%升到90%,或者从90%降到10%)

实际的Ts跟驱动器的能力,电路设计都有关系,我们取一个大概可能的值例如300(setup time是指信号建立并稳定的时间一般要比简单上升或者下降时间大些。

可以算出Tdelay = 1000000/(2*625)-300-400 =100ps=0.1ns,既折算回导线之间最大的长度差L= 0.1* 299792458(光速)/10^9 = 0.012m=1.2cm。所以导线之间最大的布线距离差在此种情况下估算不能超过1.2cm。”

小结

对于普通FR4板材的微带线,1.6mm走线传输时延约为11ps,对于带状线约为12.5ps

微带线的走线延时大约为140ps/inch,带状线的走线延时大约为166ps/inch。(表层走线比内层快:表层即微带线走线周围介电常数小于4)

(V=C/Er0.5,Er是信号线周围材料的相对介电常数。如果信号线暴露在空气中那么信号的传输速度就等于C。如果信号线暴露在空气中那么信号的传输速度就等于C。常见的PCB材料Fr4介电常数在4.2~4.5左右,信号传输速度是光速的二分之一。光速大约12inch/ns,信号大约6inch/ns.换成延时,就是常说的PCB板上信号延时大约是166ps/inch.)

差分对的线长差(mil) < 0.2*Rt*V,Rt是差分信号的上升时间,V是差分信号在PCB中的传播速度,一般是6000mil/ns。

设计时注意:

1)尽量减少不必要的绕线,比如串行信号差分对和差分对之间没有必要做等长。

2)增大绕线间间距,尽量满足单根绕线间距大于5H(H为线到最近参考面的距离),差分绕线大于3H。

4)尽量增加平行线段的距离S,至少大于3H,H 指信号走线到参考平面的距离。通俗的说就是绕大弯走线,只要S 足够大,就几乎能完全避免相互之间的耦合效应。

5)带状线(Strip-Line内层)或者埋式微带线(Embedded Micro-strip)的蛇形走线引起的信号传输时延小于微带线走线(Micro-strip)。理论上,带状线不会因为差模串扰影响传输速率。走线尽量走带状线,减小串扰影响;

6)高速以及对时序要求较为严格的信号线,尽量不要走蛇形线,尤其不能在小范围内蜿蜒走线。

7)高速PCB 设计中,蛇形走线没有所谓滤波和抗干扰的能力,只可能降低信号质量,所以只作时序匹配之用而无其他目的。

8)耦合长度尽量短,相邻传输线平行走线长度越长串扰越大;走线尽量减小相邻平行线走线长度;对相邻层走线尽量采用垂直走线;减小耦合幅度Lp,当两倍的Lp 时延接近或超出信号上升时间时,产生的串绕将达到饱和。

9)保持完整回流平面,避免跨分割,走线和参考面尽量紧耦合;

10)需要做等长的信号要尽量走同层,换层时需要注意总的长度要保持相等并且每层走线都需要等长。

9616

9616

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?