PCB设计之信号的传播延时

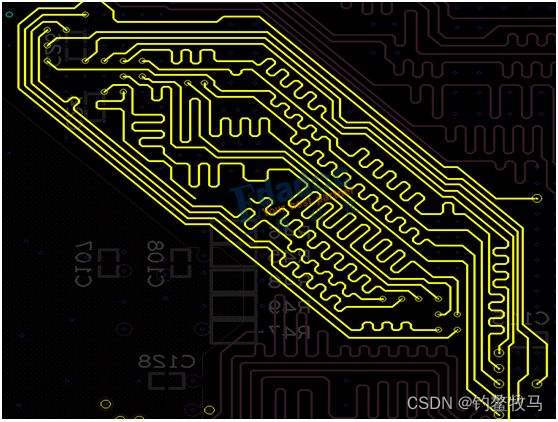

PCB设计中我们经常会提到一个概念就是要求同组同层,DDR信号要做组内等长,差分信号要求做对内等长,甚至一些差分组之间也要做等长控制。客户发来的设计要求和芯片的手册中,我们可以看到各式各样的等长要求。随着信号速率越来越高,PCB的设计中大量出现需要控制等长的内容。

信号要能正常工作都必须满足一定的时序要求,随着信号速率的升高,数字信号的发展经历了从共同时钟到源同步时钟以及串行(serdes)信号。在当今的消费电子,通信服务器等行业,源同步和串行信号占据了很大比重。串行信号比如常见的PCIE、SAS、SATA、SFP+、10GBASE-KR等信号,源同步信号比如DDR信号。

串行信号在发送端将数据信号和时钟(CLK)信号通过一定的编码方式一起发送,在接收端通过时钟数据恢复(CDR)得到数据信号和时钟信号。由于时钟数据在同一通道传播,串行信号对与对之间在PCB上传输延时要求较低,主要依靠锁相环(PLL)和芯片的时钟数据恢复功能。

源同步时钟主要是DDR信号,在DDR设计中,DQ(数据)信号参考DQS(数据选通)信号,CMD(命令)信号与Ctrl(控制)信号参考CLK(时钟)信号,由于DQ的速率是CMD&Ctrl信号速率2倍,所以DQ信号和DQS信号之间的传输延时要求比CMD&Ctrl和CLK之间的要求更高。目前市场上主流的为DDR3与DDR4。DDR5目前已经开始进入市场,在DDR5设计中,DQ与DQS之间的传输延时设计将面临更高的挑战。

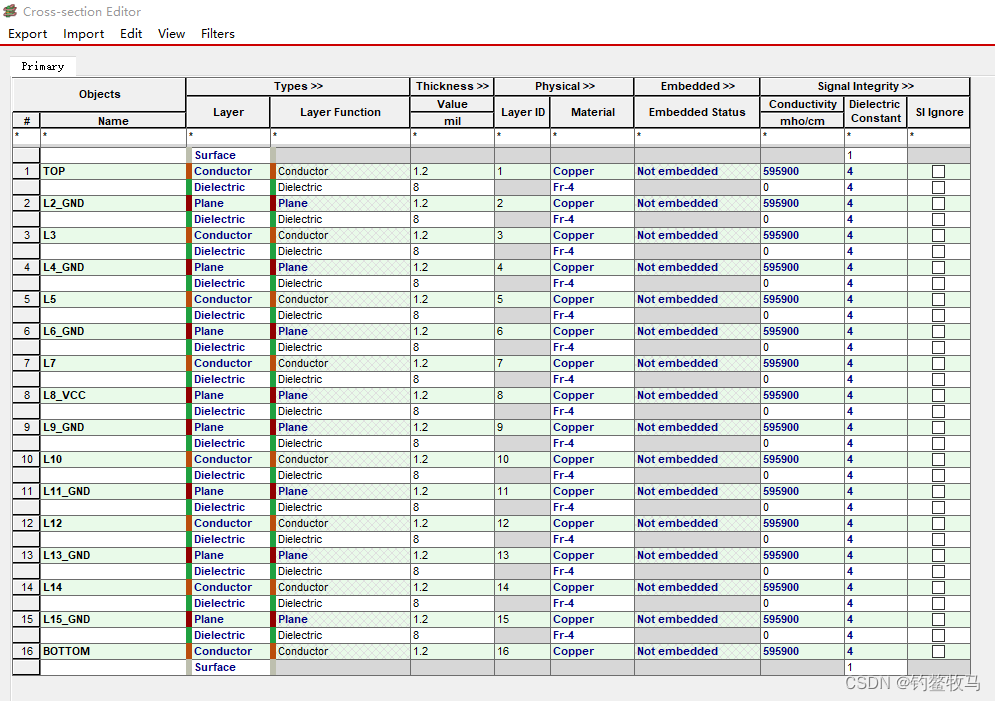

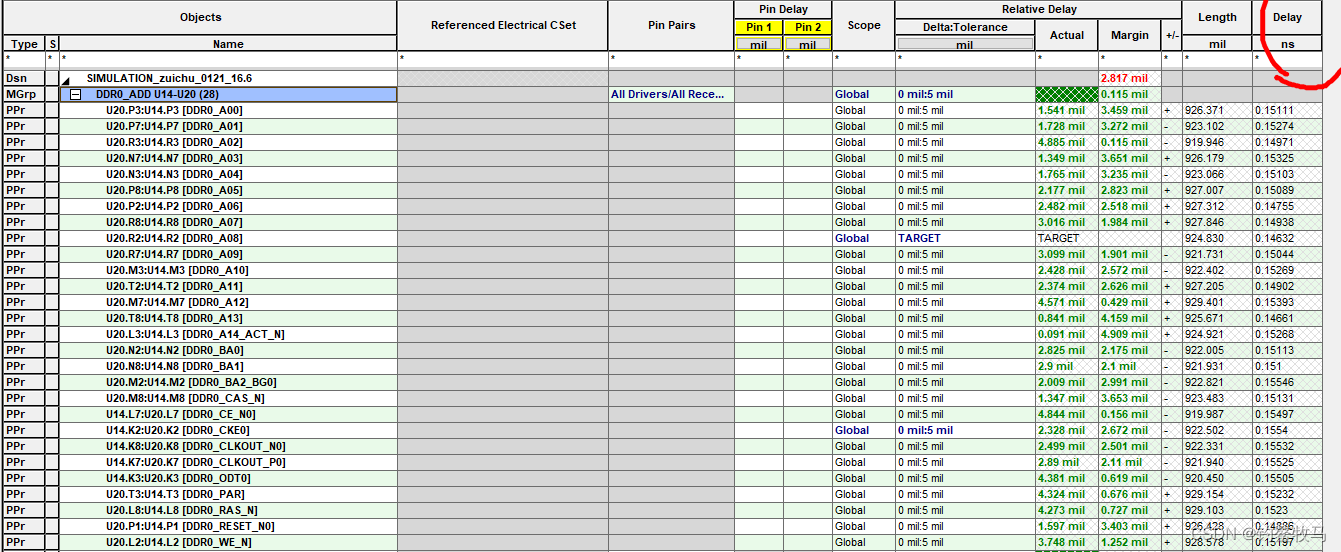

绕等长的核心目的其实是为了系统的等时,最终我们研究的目的就到了时序上,简而言之,绕等长是为了满足时序要求。目前设计软件已经支持对于信号延时的估算。以Allegro为例,在准确填写叠层厚度和介电常数基础上,利用设计软件分析功能可以初步得出信号实际的延迟(Delay)。

|

|

|

| 准确填写叠层厚度和介电常数 | 规则设置与观察信号延时 |

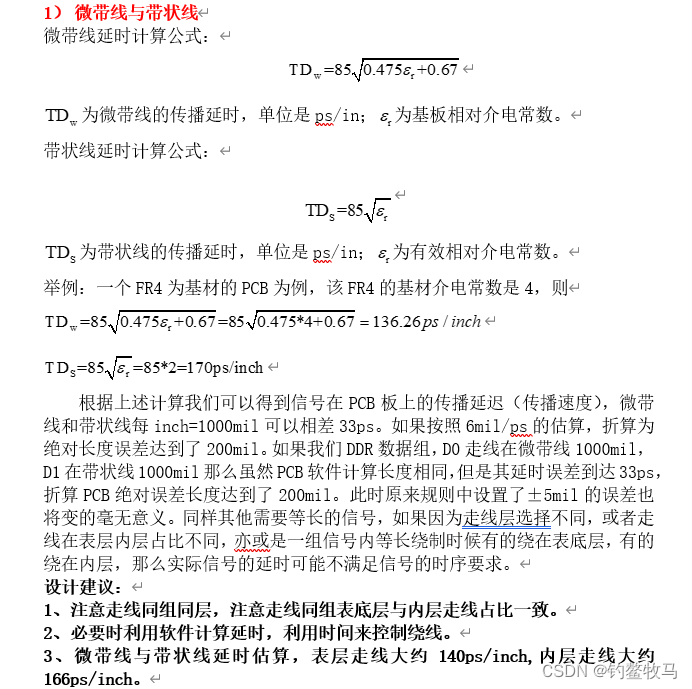

既然我们的终极目的是保证信号的时序即信号的实际延迟,接下来我们介绍一些常见影响信号延迟的要素和计算方式:

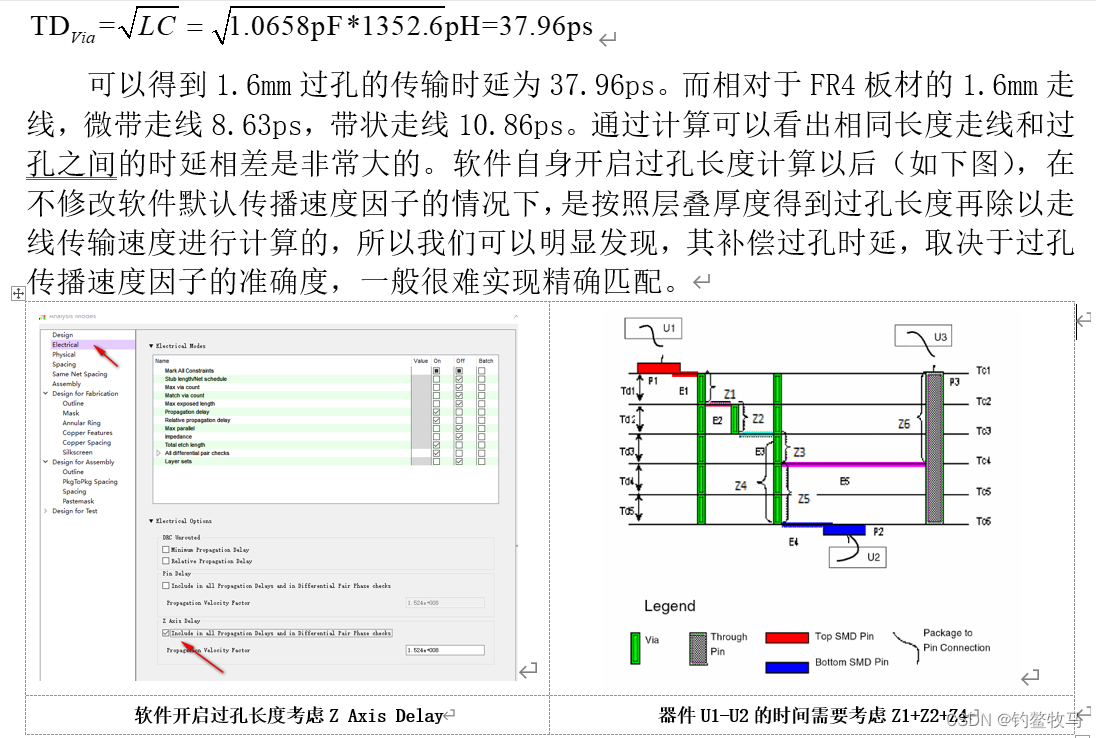

默认参数只能补偿一部分过孔的延时。如果过孔还有残桩的话会进一步导致过孔延迟增大,所以目前简单的软件计算过孔长度没法完美解决过孔时延问题。待以后设计软件内置信号完整性分析工具后或可实现精确补偿,由此我们发现目前最好的方法还是同组同层。做到过孔长度、焊盘大小、隔离大小,残桩、数量相同,则过孔的延时导致的时序问题不攻自破。

设计建议:

1、优先同组同层(规避过孔长度,大小、残桩等差异)

2、打开软件的过孔考虑项(尤其是DDR4等高速设计中以及一些板子特别厚的设计,尽可能补偿过孔的时延)

3)绕线

在PCB设计时候,有些设计人员为了满足等长要求会对走线进行绕线,很少有设计人员会考虑到不恰当的绕线也会影响传输线时延。

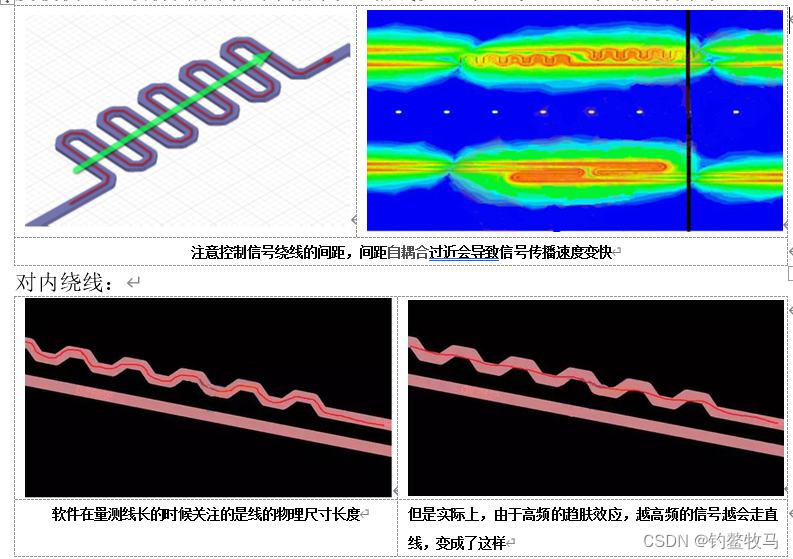

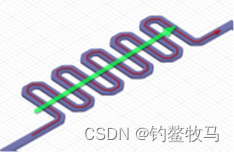

对间绕线:

绕制间距过近会导致信号间的串扰,间距过近的蛇形绕线,这是由于蛇形绕线靠的太近,平行的耦合长度太长,信号在蛇形绕线上的自耦合导致信号传播速度较快。后续仿真案例里面给出了1倍线宽边缘距与3W边缘距的仿真对比。

看来小波浪也不能太小,通常我们会让小波浪的每段都在2-3倍的线宽。

设计建议:

1、在PCB设计时候尽量减少不必要的绕线,比如一些串行信号差分对和差分对之间没有必要做等长要避免绕线。

2、增大绕线间间距,尽量满足单根绕线间距大于5H(H为线到最近参考面的距离),差分绕线大于3H(H为线到最近参考面的距离)。

3、减小绕线间平行走线长度。

4、对内等长如果采用小鼓包,鼓包长度需要满足3W原则,高度2H原则。

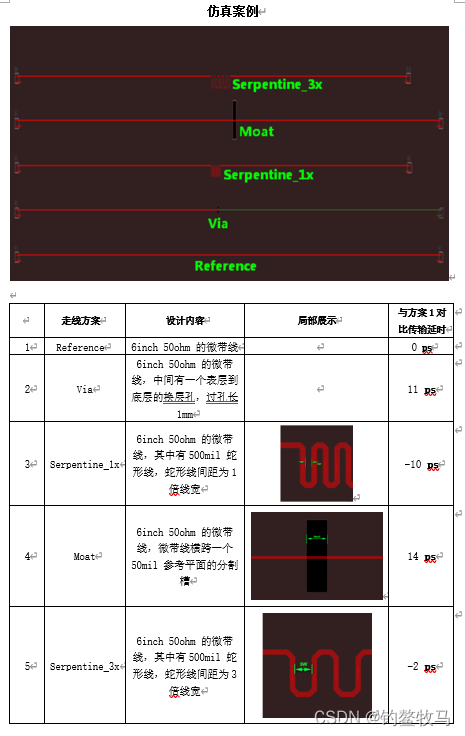

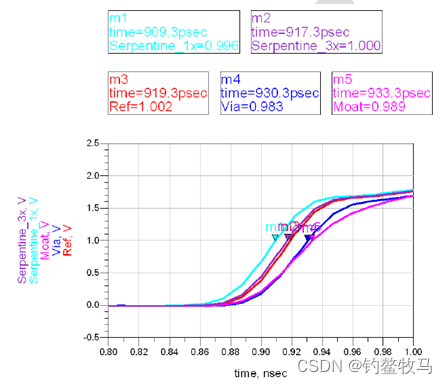

Case1:过孔带来的时延差值为11ps,这个就很好理解了,过孔有一定的物理长度,该过孔长1mm,过孔本身还具有寄生电容和寄生电感,所以实际带给信号的传输线延会比普通传输线要大,本例中是11ps,而且这个延时跟频率有一定关系。使用软件单独提取该过孔的模型,如下图,过孔的延时为10ps,与仿真得到的11ps 差不多。 如

何 关

Case2:1 倍线宽的蛇形绕线带来的延时差异是-10ps,比参考线快了10ps,造成延时差异的主要原因是信号的自耦合现象。在绕蛇形线的时候,期望的信号传输路径是沿着下图红色箭头传输,可是由于蛇形线之间的距离太近,导致信号实际传输路径是下图绿色箭头所指示的那样(当然,实际上信号也不会以绿色箭头那样传输,在这里这么标注只为了大家更形象的理解记忆,后期会有详细解释)。所以就导致了信号提前到达接收端。

如果把蛇形线之间的间距拉开,比如从1 倍线宽拉到3 倍线宽,信号的延时差异立刻缩小到-2ps,差异就没有那么大了。所以在使用蛇形线匹配长度时,要注意蛇形线之间的间距一定要拉开,拉开多远可参考下图

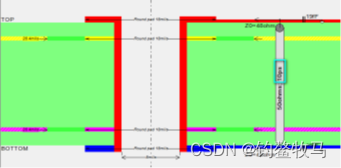

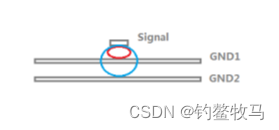

Case3:当参考线跨过50mil 的分割线时,带来的延时为14ps。在PCB 设计中,同一层的平面常常会因为不同的用途而分割开来,由此就会导致很多分割线。众所周知,传输线由信号路径和返回路径组成,信号的返回路径通常在距离信号路径最近的参考层上, 且在信号路径正下方(如下图红色圆圈)。如果跨过分割线,信号的返回路径被切断,信号就要寻找其他的返回路径回流,因此信号的回路面积就增大(如下图蓝色圆圈),传输线延时就会增大。

总结:在PCB设计时候要将等长的设计观念逐步向等时设计转变,在对时序或者等长要求高的设计尤其需要注意串扰,绕线方式,不同层走线,过孔时延等方面对时序的影响,妥善评估PCB板上的传输时延,从而提高设计的质量。

2213

2213

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?