流水灯

实验要求

实现四个灯循环亮,每个灯亮0.5s

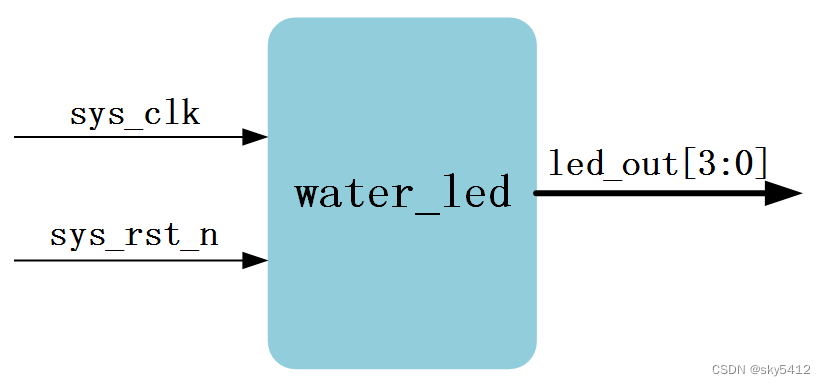

程序框图

波形图

led_out由led_out_reg取反获得,每当cnt_flag获得一个脉冲时,就将led_out_reg的值左移

代码

module water_led

#(

parameter CNT_MAX = 25'd24_999_999

)

(

input clk,reset,

output[3:0] led_out

);

reg[24:0] cnt;

reg cnt_flag;

reg[3:0] led_out_reg;

// 计数器

always @(posedge clk or negedge reset)

if(reset == 1'b0)

cnt <= 25'd0;

else if(cnt == CNT_MAX)

cnt <= 25'd0;

else

cnt <= cnt + 25'd1;

// 脉冲信号

always @(posedge clk or negedge reset)

if(reset == 1'b0)

cnt_flag <= 1'b0;

else if(cnt == CNT_MAX - 25'd1)

cnt_flag <= 1'b1;

else

cnt_flag <= 1'b0;

always @(posedge clk or negedge reset)

if(reset == 1'b0)

led_out_reg <= 4'b0001;

else if(led_out_reg == 4'b1000 && cnt_flag == 1'b1)

led_out_reg <= 4'b0001;

else if(cnt_flag == 1'b1)

led_out_reg <= led_out_reg << 1;

else

led_out_reg <= led_out_reg;

assign led_out = ~led_out_reg;

endmodule

仿真测试

`timescale 1 ns/ 1 ns

module water_led_vlg_tst();

reg clk;

reg reset;

wire [3:0] led_out;

water_led

#(

.CNT_MAX(25'd24)

)

i1 (

.clk(clk),

.led_out(led_out),

.reset(reset)

);

initial

begin

clk = 1'b1;

reset <= 1'b0;

#20

reset <= 1'b1;

end

always #10 clk = ~clk;

endmodule

6815

6815

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?