定时器资源:

最多包括两个高级定时器;四个普通定时器,和两个基本定时器,两个看门狗定时器和一个系统滴答定时器。

高级定时器、普通定时器和基本定时器资源对比如下:

| 定时器类型 | 分辨率 | 计数器类型 | 预分频系数 | 产生DMA请求 | 捕获/比较通道 | 互补输出 |

| 高级(TIM1, TIM8) | 16位 | 向上、下、上/下 | 1-65536 | 可以 | 4路 | 可以 |

| 普通(TIM2, 3,4,5) | 16位 | 向上、下、上/下 | 1-65536 | 可以 | 4路 | 不可以 |

| 基本(TIM6, 7) | 16位 | 向上计数 | 1-65536 | 可以 | 无 | 不可以 |

时钟与复位

复位

系统复位

系统复位会将所有寄存器都设置为默认值,除了RCC_CSR寄存器和备份区域。

系统复位的触发:

- 外部复位:NRST引脚输入低电平。

- 看门狗复位:窗口看门狗计数结束;独立看门狗计时结束。

- 软件复位

- 低功耗管理复位

软件复位

通过将Cortex®-M3中复位控制寄存器中的SYSRESETREQ位置1。

上电复位

当进入待机模式

当进入停止模式

电源复位

上电/掉电时的复位。

从待机模式中返回复位。

备份域复位

软件复位,备份区域复位可由设置备份域控制寄存器 (RCC_BDCR)(见6.3.9节)中的

BDRST位产生。

在VDD和VBAT两者掉电的前提下,VDD或VBAT上电将引发备份区域复位。

时钟

时钟树

可用于供给系统运转的三大时钟:

HSI振荡器时钟

HSE振荡器时钟

PLL时钟。

拥有二级时钟源的设备:

1、40kHZ低速内部RC时钟(LSI)。一般用于驱动独立看门狗以及从待机/停机状态下唤醒系统。

2、32.768kHZ的低速内部晶振。用于驱动RTC时钟。

*关于选用32.768kHZ的解释:RTC时钟需要的精度和可靠性较高,不需要太高的晶振速度。同时为了得到准确的1HZ(1s),32.768kHZ经15分频之后正好得到1HZ。

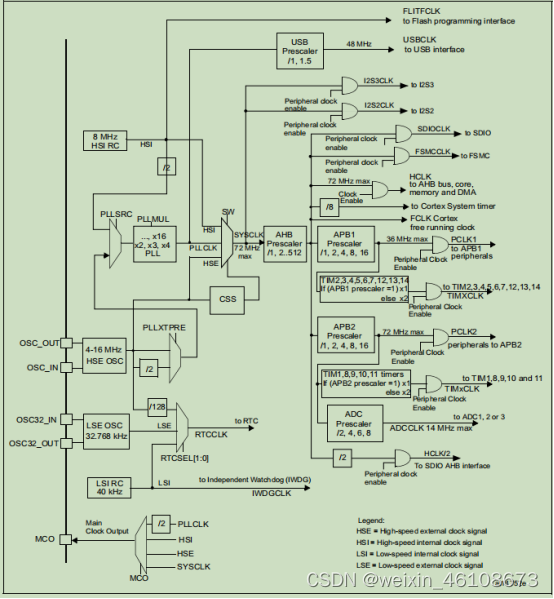

关于时钟树:

左边部分为时钟源和预分频器。经过分频的时钟信号会经过AHB总线来到右半部分。经过进一步的分频等操作,为外设提供时钟信号。

涉及的时钟源:HSE,HSI,LSE,LSI。

AHB总线

APB1(低速):最高频率为36MHz

APB2(高速):最高频率为72MHz

SDIO(安全数字输入输出接口)接口的时钟频率固定为HCLK/2。可用于SD卡通讯。

定时器时钟频率

若AHB的预分频系数为1,表示其频率与所在的AHB总线相同。

若AHB的预分频系数为2,其频率是所在AHB总线频率*2。

时钟树怎么看?

以TIM来举例。

①:振荡器输入时钟信号:OSC_OUT和OSC_IN。产生HSE高速外部时钟。

②:HSE时钟信号一直传输到AHB总线上,TIM所处的总线是高速APB2总线。因此信号会来到APB2。

③:信号来到TIM处后判断其分配系数,如上诉定时器时钟频率所说。

④:提供时钟信号的同时,也需要使能TIMx的时钟。

常用外设的时钟源:

HSE:一般可以用于精度要求较高的外设。常见外设USART, SPI, IIC。

HSI:常见于GPIO。

PLL:一般用于提高工作频率。常见于ADC,TIM。

LSI:一般用于低功耗下的外设。独立看门狗。

LSE:常见于RTC。

时钟树后续内容

HSE高速外部时钟

产生HSE信号的来源:

- HSE外部晶振

- HSE外部时钟

为了提高时钟输出的稳定性以及缩短启动稳定时间,需要尽量将外部时钟源和电容与晶振安装在离振荡输入引脚更近的位置。

外部时钟源(HSE旁路)

需要提供外部时钟源,最高频率可到25MHZ。操作在RCC_CR寄存器中的HSEBYP和HSEON两个位以选择该模式。

外部晶振

外部晶振可以提供4~16MHZ的、精度更高的时钟作为系统主时钟。

可以在RCC_CR中的HSERDY位查看HSE是否稳定,在启动阶段如果该位没有被硬件置位,时钟信号将不会被释放。

可以在RCC_CIR寄存器中使能其时钟中断。

HSE晶体可以通过设置时钟控制寄存器里RCC_CR中的HSEON位被启动和关闭。

HSI 高速内部时钟

HSI由8MHZ RC振荡器产生,可以直接用于系统时钟或者2分频后作为PLL输入。

HSI RC振荡器无需其他外部器件可以提供时钟源。启动时间会比HSE短,但是在校准后其时钟精度依然较差干哈。

HSI 校准

RC振荡器的频率会被多种因素影响。在复位之后,可以在RCC_CR的HSICAL[7:0]查看其出厂校准值。可以通过RCC_CR里的HSITRIM[4:0]位来调整HSI频率。

可以在RCC_CR中的HSIRDY位查看HSI是否稳定,在启动阶段如果该位没有被硬件置位,时钟信号将不会被释放。

HSI RC可以通过设置时钟控制寄存器里RCC_CR中的HSION位被启动和关闭。

当HSE晶振失效时,HSI信号可以作为备用时钟源。

PLL

内部PLL可以用于对HSI RC和HSE晶振进行倍频。

对PLL的配置必须在使能PLL之前,PLL启动后无法再更改其配置参数。

RCC_CIR中可以配置PLL时钟中断。

如果涉及USB的使用,PLL必须配置为48MHZ或者72MHZ输出。用于提供48MHZ的USBCLK。

LSE 低速外部时钟

LSE晶振是32.768kHz的低速晶振,在低功耗的同时保持着高精度。可以用于RTC。

通过RCC_BDCR的LSEON位使能LSE。通过LSERDY位查看是否稳定,在RCC_CIR中配置其时钟中断。

LSE旁路

需要提供外部时钟源。最高可到1MHZ。通过RCC_BDCR寄存器配置。

LSI 低速内部时钟

LSI RC可以作为低功耗时钟源,在停止模式和待机模式下为独立看门狗和自动唤醒单元供电。时钟频率大约为40kHZ。

在RCC_CSR中配置LSION以使能LSI RC。在RCC_CIR中使能其时钟中断。

LSI校准

可以通过TIM5来对LSI RC进行校准。来提供更准确的时钟信号给IWDG或者RTC。

步骤:

- 使能TIM5定时器,配置其通道4进行输入捕获。

- 将AFIO_MAPR的TIM5_CH4_IREMAP置为1,因此将LSI连接到TIM5的通道4.

- 通过TIM5的输入捕获/比较或者中断来测量LSI的频率。

- 根据测量结果,设置20位预分频器。

SYSCLK系统时钟

系统复位后,HSI被设置为系统时钟。系统时钟源的切换只能发生在目标时钟源都已经就绪的情况下。

在RCC_CR里的状态位指示哪个时钟已经准备好了,哪个时钟目前被用作系统时钟。

CSS 时钟安全系统

CSS可以被软件启动。CSS将在HSE振荡器启动延迟后被使能,并在HSE时钟关闭后关闭。

HSE若发生故障,HSE将被自动停止。然后将该事件发送至高级定时器,并且产生时钟安全中断CSSI,允许软件完成营救操作。

RTC

RTC的时钟源选择:HSE/128,LSE,LSI。选择不同的时钟源需要配置寄存器RCC_BDCR的RTCSEL[1:0]。若备份区域不复位,无法对配置进行更改。

LSE时钟位于备份区域中,LSI和HSE不在。

若选用LSE作为RTC时钟源:

- 无需VDD供应,仅需要提供VBAT即可维持运行。

若选用LSI作为AWU时钟源:

- AWU的运行需要VDD的供应。

若选用HSE/128作为RTC时钟源:

- 如果VDD供电被切断或内部电压调压器被关闭(1.8V域的供电被切断),则RTC状态无法保证。

- 必须设置pwr_cr的DPB位(取消后备区域的写保护)为1。

看门狗时钟

若独立看门狗已经由硬件选项或软件启动,LSI振荡器将被强制打开,且无法关闭。在LSI振荡器稳定后,时钟供应给IWDG。

时钟输出

MCO:Main Clock Output.主时钟输出,通过MCO pin可以将主时钟信号输出到外部。

可以作为MCO输入的时钟源:

SYSCLK

HSI

HSE

PLL clock / 2

时钟的选择由RCC_CFGR中的MCO[2:0]位控制。

时钟相关寄存器

RCC寄存器基地址:0x40021000

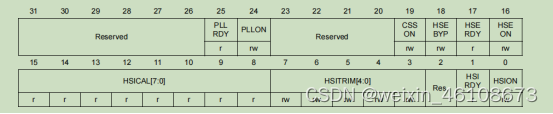

时钟控制寄存器 RCC_CR

地址偏移:0

复位默认值: 0x0000 xx83

PLLRDY:PLL时钟是否继续标志

0:未锁定

1:已锁定(硬件置位)

PLLON:PLL时钟使能

0:关闭

1:打开

CSSON:时钟安全系统使能

0:时钟监测器关闭;

1:如果外部4-16MHz振荡器就绪,时钟监测器开启。

HSEBYP:外部高速时钟旁路

只有在外部4-16MHz振荡器关闭的情况下,才能写入该位。

0:外部4-16MHz振荡器没有旁路;

1:外部4-16MHz外部晶体振荡器被旁路。

HSERDY:外部高速时钟就绪标志

0:外部4-16MHz振荡器没有就绪;

1:外部4-16MHz振荡器就绪。(硬件置位)

HSEON:外部高速时钟使能

0:HSE振荡器关闭;

1:HSE振荡器开启。

HSICAL[7:0]:内部高速时钟校准

在系统启动时,这些位被自动初始化

HSITRIM[4:0]:内部高速时钟调整

HSIRDY:内部高速时钟就绪标志

0:内部8MHz振荡器没有就绪;

1:内部8MHz振荡器就绪。(硬件置位)

HSION:内部高速时钟使能

发送故障时,该位会被硬件置为1。来启动内部8MHZ的振荡器。

0:内部8MHz振荡器关闭;

1:内部8MHz振荡器开启。

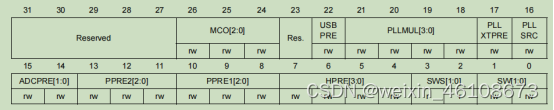

时钟配置寄存器 RCC_CFGR

地址偏移:0x04

复位默认值: 0x0000 0000

MCO:微控制器时钟输出

0xx:没有时钟输出;

100:系统时钟(SYSCLK)输出;

101:内部RC振荡器时钟(HSI)输出;

110:外部振荡器时钟(HSE)输出;

111:PLL时钟2分频后输出。

USBPRE:USB预分频

0:PLL时钟1.5倍分频作为USB时钟

1:PLL时钟直接作为USB时钟

PLLMUL:PLL倍频系数

0000:PLL 2倍频输出 1000:PLL 10倍频输出

0001:PLL 3倍频输出 1001:PLL 11倍频输出

0010:PLL 4倍频输出 1010:PLL 12倍频输出

0011:PLL 5倍频输出 1011:PLL 13倍频输出

0100:PLL 6倍频输出 1100:PLL 14倍频输出

0101:PLL 7倍频输出 1101:PLL 15倍频输出

0110:PLL 8倍频输出 1110:PLL 16倍频输出

0111:PLL 9倍频输出 1111:PLL 16倍频输出

PLLXTPRE:HSE分频器作为PLL输入

0:HSE不分频

1:HSE 2分频

PLLSRC:PLL输入时钟源

0:HSI振荡器时钟经2分频后作为PLL输入时钟

1:HSE时钟作为PLL输入时钟。

ADCPRE[1:0]:ADC预分频

00:PCLK2 2分频后作为ADC时钟

01:PCLK2 4分频后作为ADC时钟

10:PCLK2 6分频后作为ADC时钟

11:PCLK2 8分频后作为ADC时钟

PPRE2[2:0]:高速APB预分频(APB2)

0xx:HCLK不分频

100:HCLK 2分频

101:HCLK 4分频

110:HCLK 8分频

111:HCLK 16分频

PPRE1[2:0]:低速APB预分频(APB1)

0xx:HCLK不分频

100:HCLK 2分频

101:HCLK 4分频

110:HCLK 8分频

111:HCLK 16分频

HPRE[3:0]: AHB预分频

当AHB时钟的预分频系数大于1时,必须开启预取缓冲器

0xxx:SYSCLK不分频

1000:SYSCLK 2分频 1100:SYSCLK 64分频

1001:SYSCLK 4分频 1101:SYSCLK 128分频

1010:SYSCLK 8分频 1110:SYSCLK 256分频

1011:SYSCLK 16分频 1111:SYSCLK 512分频

SWS[1:0]:系统时钟切换状态

由硬件置’1’或清’0’来指示哪一个时钟源被作为系统时钟。

00:HSI作为系统时钟;

01:HSE作为系统时钟;

10:PLL输出作为系统时钟;

11:不可用。

SW[1:0]:系统时钟切换

00:HSI作为系统时钟;

01:HSE作为系统时钟;

10:PLL输出作为系统时钟;

11:不可用。

5686

5686

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?