第2章 嵌入式处理器

1. ARM工作状态和工作模式

工作状态

- ARM状态:ARM处理器工作于32位指令的状态,即32位状态。所有指令均为32位。

- Thumb状态:ARM处理器执行16位指令的状态,即16位状态。在Thumb模式下,较短的操作码有更少的功能性,而较短的操作码提供整体更佳的编码密度。

- Thumb-2状态:兼有16位及32位指令,实现了更高的性能、更有效的功耗及更少地占用内存。

- 调试状态:处理器停机调试时进入调试状态。Cortex-M3只有Thumb-2状态和调试状态。

- ARM与Thumb间的切换:通过BX指令,将操作数寄存器的最低位设置为1[0]即可实现 ARM状态和Thumb状态的切换。

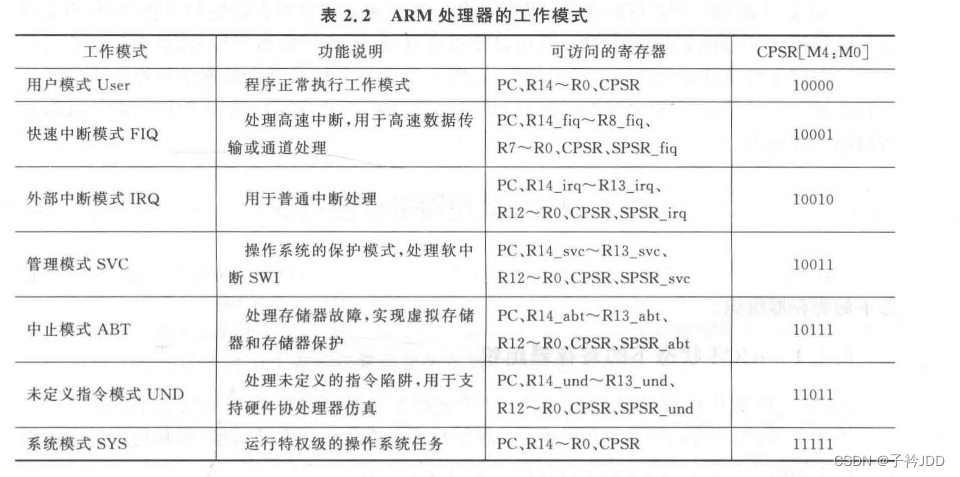

工作模式

-

经典ARM处理器的工作模式:经典ARM处理器支持7种工作模式,取决于当前程序状态寄存器 CPSR 的低5位[M4:M0]的值。ARM处理器工作模式可以相互转换,但是是有条件的。当处理器工作于用户模式时,除非发生异常,否则将不能改变工作模式。当发生异常时,处理器自动改变CPSR[M4:M0]的值,进入相应的工作模式,例如当发生IRQ外部中断时CPSR[M4:M0]的值置为10010,而自动进入外部中断模式;当处理器处于特权模式时,用指令向CPSR[M4:M0]写入特定的值,以进入相应的工作模式。

-

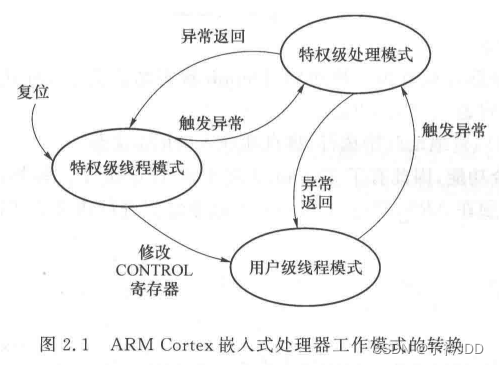

ARM Cortex-M系列嵌入式处理器的编程模式及特权级:线程模式(Thread mode)是执行普通代码的工作模式,而处理模式(Handler mode)是处理异常中断的工作模式。复位时系统自动进入线程模式,异常处理结束返回后也进入线程模式,特权和用户代码能在线程模式下运行。当出现异常中断时,处理器自动进入处理模式,在处理模式下,所有代码都是特权访问的。

2、ARM Cortex-M寄存器结构

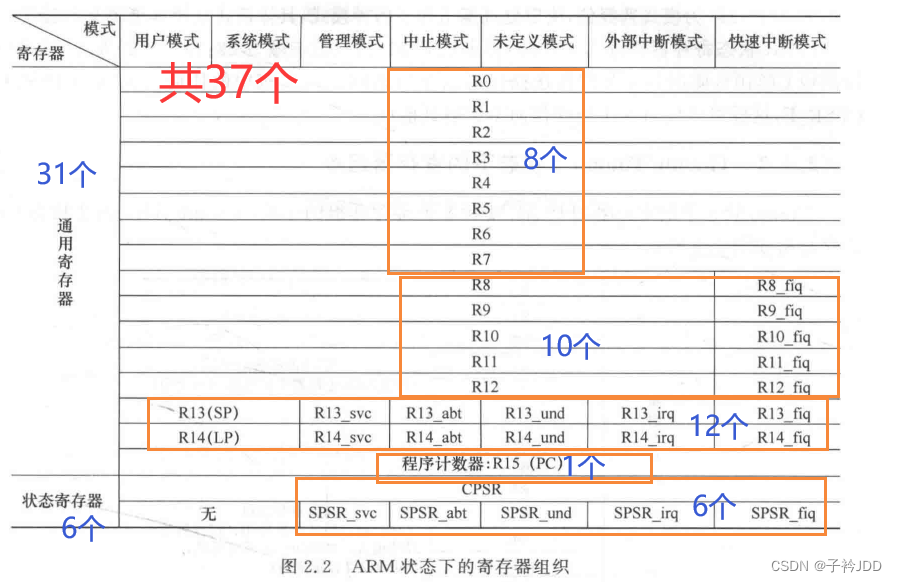

ARM状态下的寄存器组织

所有通用寄存器均为32位结构。

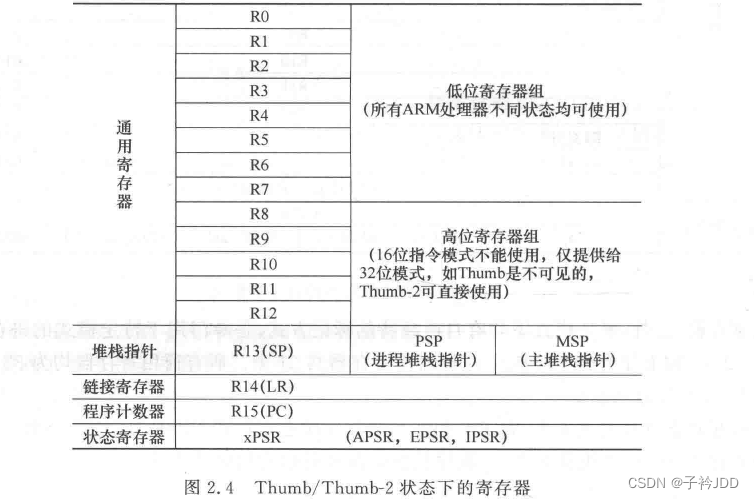

Thumb/Thumb-2状态下的寄存器组织

Thumb状态下的寄存器组是ARM状态下寄存器组的子集。高位寄存器R8~R12在Thumb状态下不可见,即不能直接作为通用寄存器使用,而在Thumb-2下可以使用,即R8~R12只有在32位指令状态下才可当通用寄存器使用。

R13为堆栈指针,有两个堆栈指针,一个是主堆栈指针MSP,另一个是进程堆栈指针PSP,R14为链接寄存器LR,R15为程序计数器PC。

3、ARM Cortex异常中断及中断向量、堆栈

ppt22

经典ARM处理器的异常中断

- 经典ARM的异常类型

- 在经典ARM体系结构中,异常中断用来处理软中断、未定义指令陷井、系统复位及外部中断。共有7种不同类型的异常中断及其对应的向量地址。优先级由高到低依次是:

(1)复位异常RESET(最高优先级)

(2)数据访问中止异常DABT

(3)快速中断异常FIQ

(4)外部中断异常IRQ

(5)指令预取中止异常FABT

(6)软件中断异常SWI和未定义的指令异常(最低优先级)

- 经典ARM异常的中断响应过程:

(1)保护状态寄存器。CPSR=>SPSR,对处理器当前状态、中断屏蔽及各标志位的保护。

(2)设置状态寄存器。设置CPSR中的M4~M0的5个位使进入相应工作模式,设置I=1禁止IRQ中断。

(3)保存断点地址。将断点地址保存到新的异常工作模式的R14中。

(4)转中断入口地址。给程序计数器PC强制赋值,使转入由中断向量地址,以便执行相应的处理程序。 - 经典ARM多异常程序中返回:

(1)恢复原来被保护的用户寄存器。

(2)恢复程序状态寄存器。SPSR=〉CPSR,以恢复被中断的程序工作状态。

(3)恢复断点地址。将PC值恢复成断点地址,以执行用户原来运行着的程序。

(4)开中断。清除CPSR中的中断禁止标志I和F,开放外部中断IRQ和快速中断FIQ。

这些操作都是中断返回时自动完成的,无需用户使用堆栈操作指令。

ARM Cortex-M微控制器的异常中断

ARM Cortex-M微控制器异常状态:未激活Inactive状态、挂起Pending状态、激活Active状态、激活且挂起Active and pending状态。

ARM Cortex-M微控制器异常类型:系统复位Reset、不可屏蔽中断NMI、硬件故障Hard Fault、存储器管理故障MemManage、总线故障(预取中止或数据中止)、使用故障usage、SVC指令产生的异常SVCall、可挂起的系统服务异常PendSV、系统滴答定时器中断SysTick以及外部中断Interrupt(IRQ0-IRQ239)。

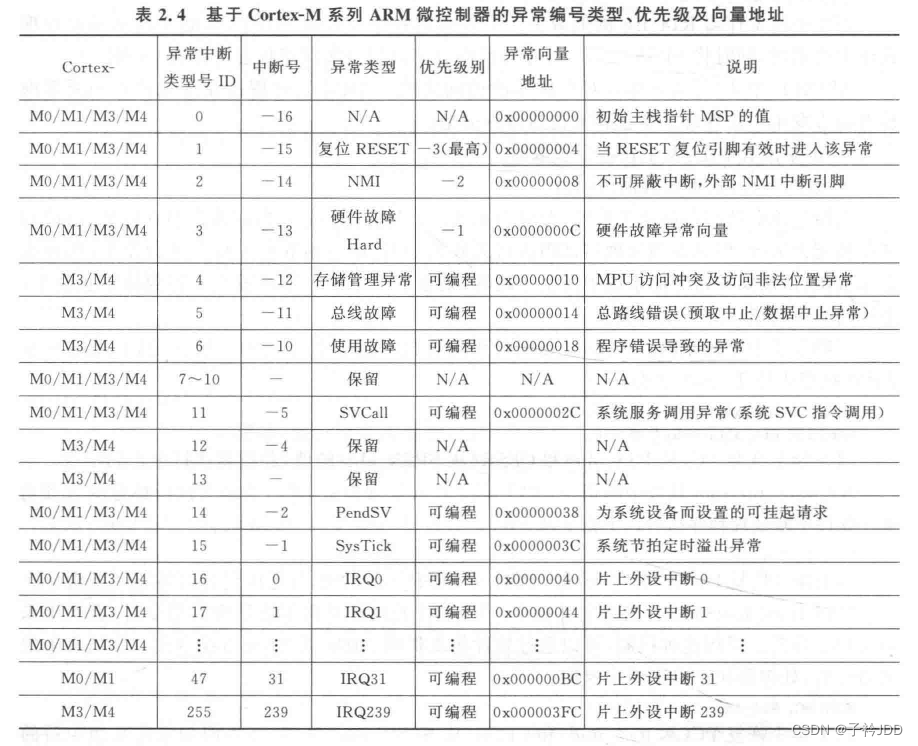

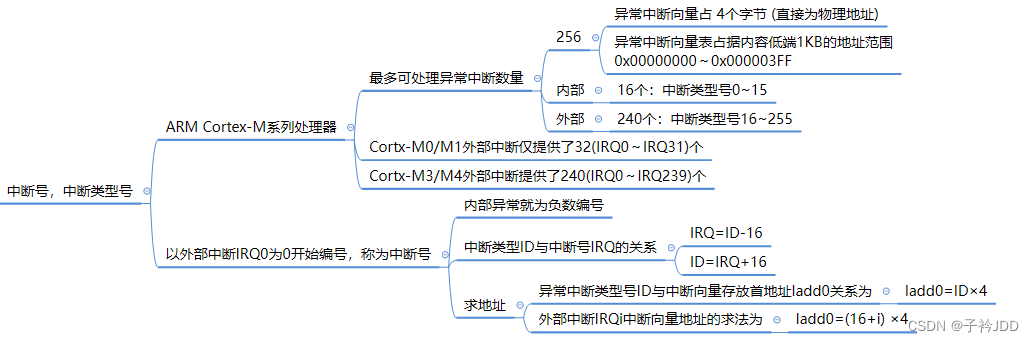

中断号,中断类型号

ARM Cortex-M系列处理器最多可处理256个异常中断,系统内部异常编号0~15,外部中断编号16~255,即中断类型号ID从0开始到255。每个异常中断向量占4个字节(直接为物理地址),异常中断向量表占据内容最低端1KB的地址范围0x00000000~0x000003FF。

Cortx-M0/M1外部中断仅提供了32(IRQ0~IRQ31)个,

Cortx-M3/M4外部中断提供了240(IRQ0~IRQ239)个。

以外部中断IRQ0为0开始编号,称为中断号,则内部异常就为负数编号,中断类型ID与中断号IRQ的关系为:IRQ=ID-16或ID=IRQ+16,

无论已经ID还是已经IRQ均可以中断服务程序入口地址所存地址。异常中断类型号ID与中断向量存放首地址Iadd0关系为:Iadd0=ID×4 。

外部中断IRQi中断向量地址的求法为:Iadd0=(16+i) ×4

复位异常的优先级最高。任何情况下,只要进入复位状态,系统无条件地将PC指向0x00000004处,去执行系统第一条指令,通常此处放一条无条件的转移指令,转移到系统初始化程序处。

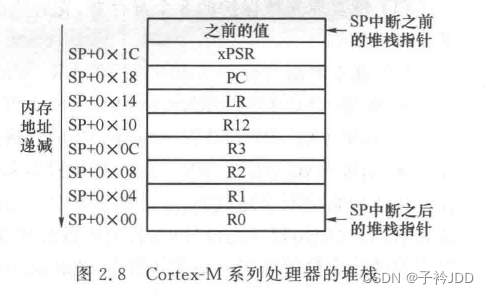

ARM Cortex-M系列微控制器的堆栈

ARM Cortex-M处理器的堆栈:采用递减地址方式,先进后出(FILO)。压入堆栈时地址减小(地址减4),弹出堆栈时地址增加(地址加4),最先压入的要最后弹出。支持两个堆栈区域,一是主堆栈,二是进程堆栈,采用两种不同的堆栈指针MSP和PSP来指示。

ARM Cortex-M异常的中断响应过程:

ARM Cortex-M异常的中断响应过程:

(1)入栈保护。中断发生时,系统自动依次将xPSR、PC、LR、R12、R3、R2、R1和R0压入堆栈

(2)取中断入口地址。根据类型号获取中断服务程序入口地址。

(3)更新寄存器。

SP更新到入栈保护后的值(-0x14)

中断服务寄存器IPSR的值为新的中断类型编号

PC指向中断服务程序入口地址

LR更新为特殊的返回值EXC_RETURN

从异常处理程序中返回:

(1)恢复保。返回时,系统自动依次将R0、R1、R2、R3、R12、LR、PC和xPSR从堆栈弹出

(2)EXC_RETURN返回值给LR。在中断服务程序结束时返回给LR。EXC_RETURN的值可以为:

如果EXC_RETURN=0xFFFFFFF1将返回处理模式,并使用主堆栈MSP;

如果EXC_RETURN=0xFFFFFFF9将返回线程模式,并使用主堆栈MSP;

如果EXC_RETURN=0xFFFFFFFD将返回处理模式,并使用线程堆栈PSP

4、ARM存储格式及数据类型

ARM存储格式

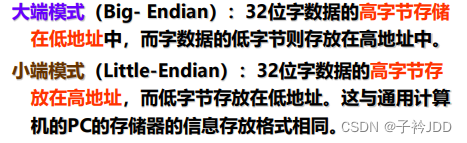

ARM体系结构将存储器看作是从0X00000000地址开始的以字节为单位的线性组合。每个字数据32位占4个字节,即4个单元的地址空间,依次排列。作为32位的处理器,ARM体系结构所支持的最大寻址空间为4GB( 2 32 {2^{32}} 232字节),可以用大端模式和小端模式两种方法存储字数据。

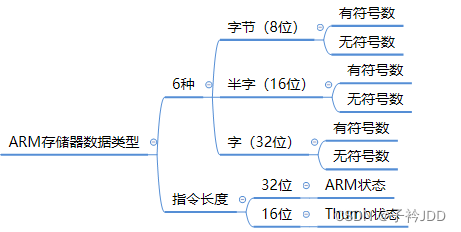

ARM存储器数据类型

ARM处理器支持字节(8位)、半字(16位)、字(32位)三种数据类型。其中,字需要4字节对齐(地址的低两位为0)、半字需要2字节对齐(地址的最低位为0)。每一种又支持有符号数和无符号数,因此共有6种数据类型。

ARM微处理器的指令长度可以是32位(在ARM状态下),也可以为16位(在Thumb状态下)。如果是ARM指令则必须固定长度,使用32位指令,且必须以字为边界对齐;如果是使用Thumb指令,指令长度为16位,则必须以2字节为对齐。

必须指出的是,除了数据传送指令支持较短的字节和半字数据类型外,在ARM内部所有操作都是面向32位操作数的。从存储器调用一个字节或半字时,根据指令对数据的操作类型,将其无符号或有符号的符号位自动扩展成32位,以作为32位数据在内部进行处理。

另外,ARM还支持其它类型的数据,如浮点数的数据类型等。

5、AMBA总线及基于该总线的嵌入式处理器组成及特点

AMBA总线

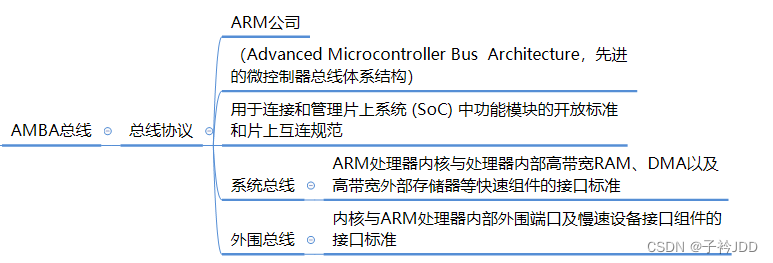

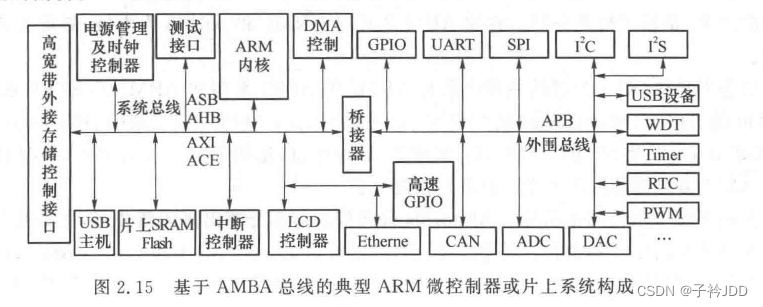

AMBA(Advanced Microcontroller Bus Architecture,先进的微控制器总线体系结构)是ARM公司公布的总线协议,是用于连接和管理片上系统 (SoC) 中功能模块的开放标准和片上互连规范。AMBA标准规定了ARM处理器内核与处理器内部高带宽RAM、DMA以及高带宽外部存储器等快速组件的接口标准(通常称为系统总线),也规定了内核与ARM处理器内部外围端口及慢速设备接口组件的接口标准(通常称为外围总线)。

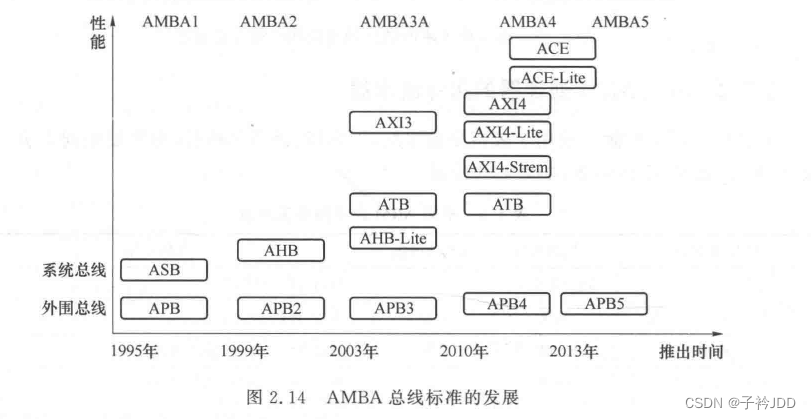

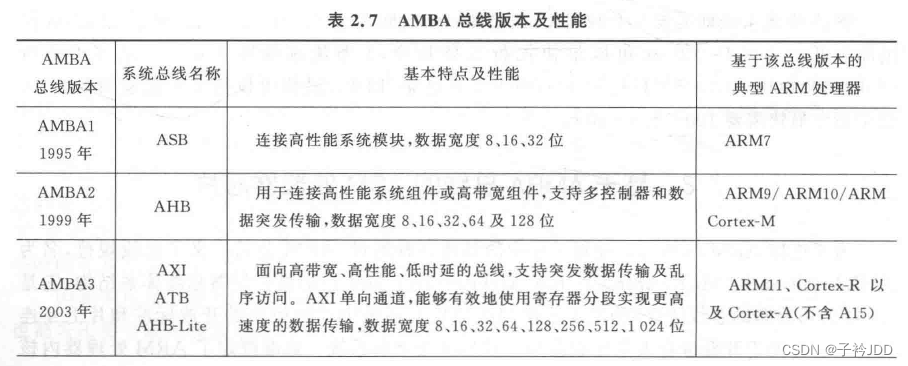

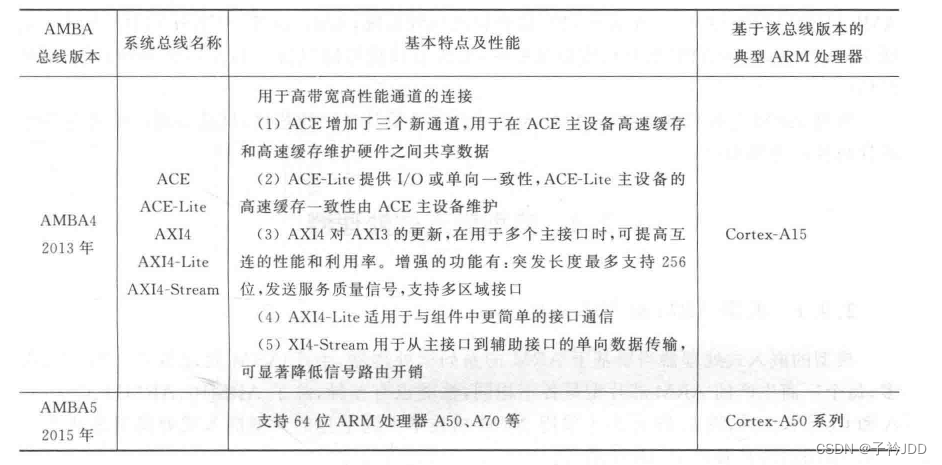

发展及版本:

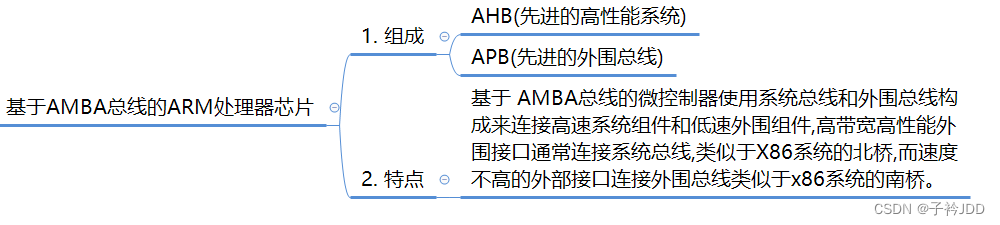

基于AMBA总线的ARM处理器芯片

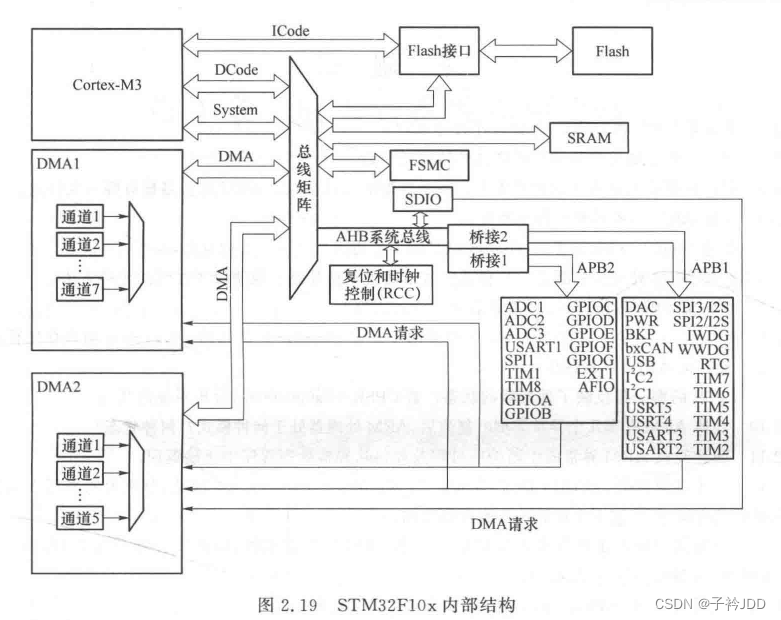

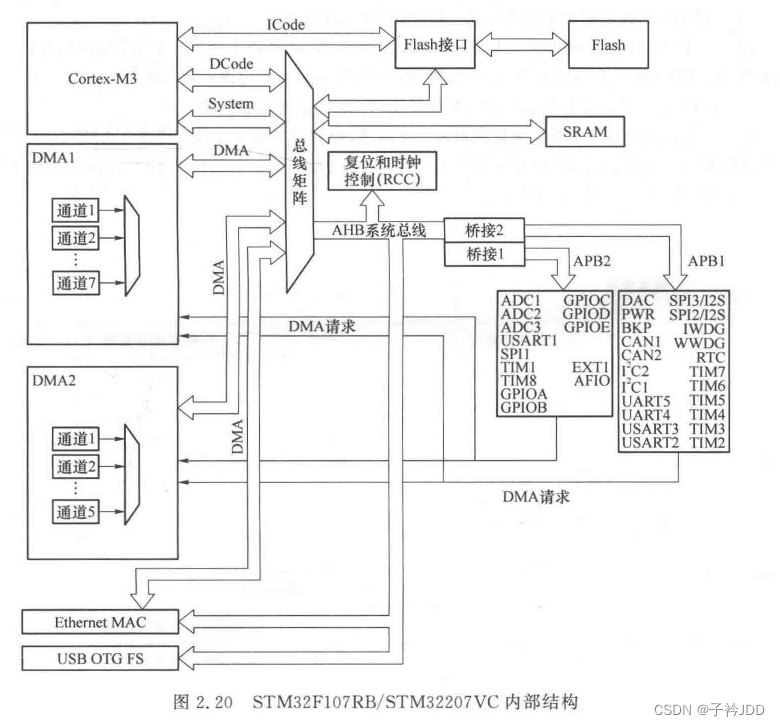

6、典型芯片STM32F10x的内部组成

本文详细介绍了ARM处理器的工作状态和模式,包括ARM、Thumb和Thumb-2状态。重点讲解了Cortex-M系列处理器的异常中断处理,包括中断向量、堆栈管理和中断响应过程。同时,概述了存储格式、数据类型以及AMBA总线在嵌入式系统中的作用。以STM32F10x芯片为例,展示了其内部组成。

本文详细介绍了ARM处理器的工作状态和模式,包括ARM、Thumb和Thumb-2状态。重点讲解了Cortex-M系列处理器的异常中断处理,包括中断向量、堆栈管理和中断响应过程。同时,概述了存储格式、数据类型以及AMBA总线在嵌入式系统中的作用。以STM32F10x芯片为例,展示了其内部组成。

605

605

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?