目录

一.SRAM存储单元结构

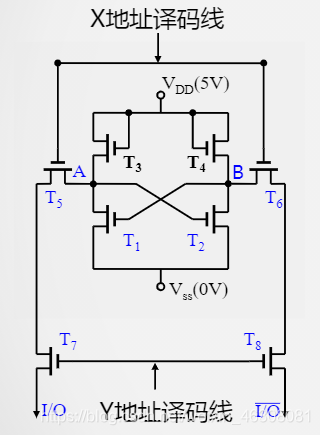

(1)结构图(双译码X+Y)

六管静态存储单元结构(每个管都处于饱和导通状态或者截止状态)

T1、T2为工作管,用来保存\存储数据

T3、T4为负载管,用于为T1、T2提供电荷

T5、T6、T7、T8为门控管,用于控制开关

(2)SRAM存储单元工作原理

X地址选通(行选通)

T5、T6管被打开,A、B与位线连通

Y地址选通(列选通)

T7、T8管被打开,A、B分别于I/O 和 非I/O 相连通

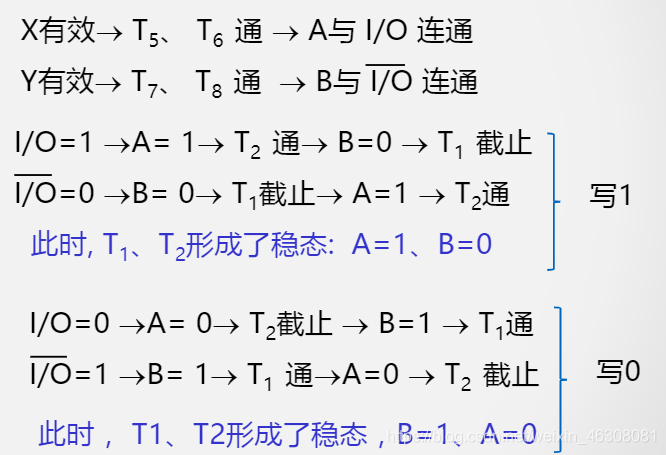

【1】写过程

对于I/O=1时的结果分析:

当I/O=1时,A=1,此时T2处于饱和导通状态,因为T2接地而且B与T2相连,所以B=0

当B=0时,T1与B相连,所以此时T1也为0,T1为0可以使A保持高电平的状态,形成稳定的互锁状态

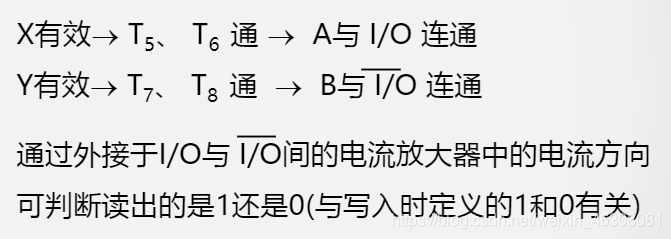

【2】读过程

当A点读入的值为1时,读出结果即I/O结果也为1

当A点读入的值为0时,读出结果即I/O结果也为0

B点同理

注意: 不论是读或写,都要求X和Y译码线同时有效!

【3】保持过程

当X和Y撤销后,由负载管T3、T4分别为T1、T2提供工作电流,保持此互锁状态。

二.静态存储器的结构

(1)单译码结构

若干个存储单元通过存储器的地址译码线来选通它的门控管

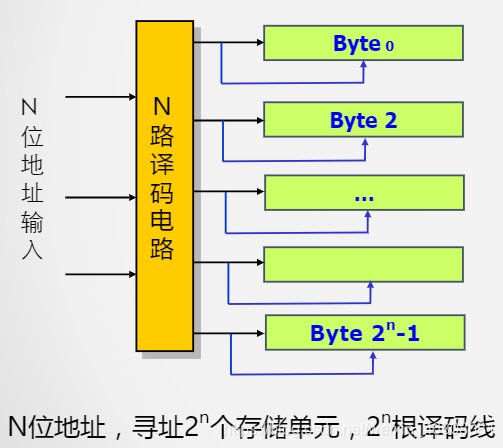

(2)双译码结构

X的译码输出作为这一行所有的行选通信号,Y的译码输出作为这一列所有的列选通信号

(3)采用双译码的静态存储器结构

上面提到的双译码结构就是图中的存储单元阵列

X和Y的位数可能不相同,均需要通过驱动器进行扩大

还有控制电路,分为读信号RD、写信号WR和片选信号CS,当片选信号有效时才可以进行其他操作。

三.例题

(1) 某计算机字长16位,其存储器容量为64KB,按字编址时,其寻址范围是多少?

【1】存储容量为64KB时,按字节编址的寻址范围就是64KB

【2】当按字编址时,因为一个字有8位,所以结果为 64K × 8 / 16 = 32K

(2) 一个16K*32位的SRAM存储芯片,其数据线和地址线之和为多少?

该存储芯片为16K*32位,那么16K为24×210,即它需要的数据线为4+10=14根。此外它还需要32根地址线,所以数据线和地址线的总和为46。

(3) 一个16K*32位的SRAM存储芯片,其内部采用位数相同的行列地址译码器,则其内部译码输出线的总量为多少?

【1】16K的存储单元需要的译码输入线为:24×210即14位。

【2】因为它采取位数相同的行列地址译码器,所以行列各7位,那么需要的译码输出线为 27 + 27 = 28 。即结果为28。

【3】拓展:当采用单译码方式时,译码输出线为 24×210 = 214

本文详细解析了SRAM存储单元的六管结构,包括写、读和保持过程,并介绍了静态存储器的单双译码结构。通过实例探讨了16位计算机寻址范围和SRAM芯片的地址线、数据线配置。涵盖了存储器容量计算、译码器输出线计算等关键知识点。

本文详细解析了SRAM存储单元的六管结构,包括写、读和保持过程,并介绍了静态存储器的单双译码结构。通过实例探讨了16位计算机寻址范围和SRAM芯片的地址线、数据线配置。涵盖了存储器容量计算、译码器输出线计算等关键知识点。

605

605

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?