使用FPGA资源PLL锁相环完成时钟的分频和倍频

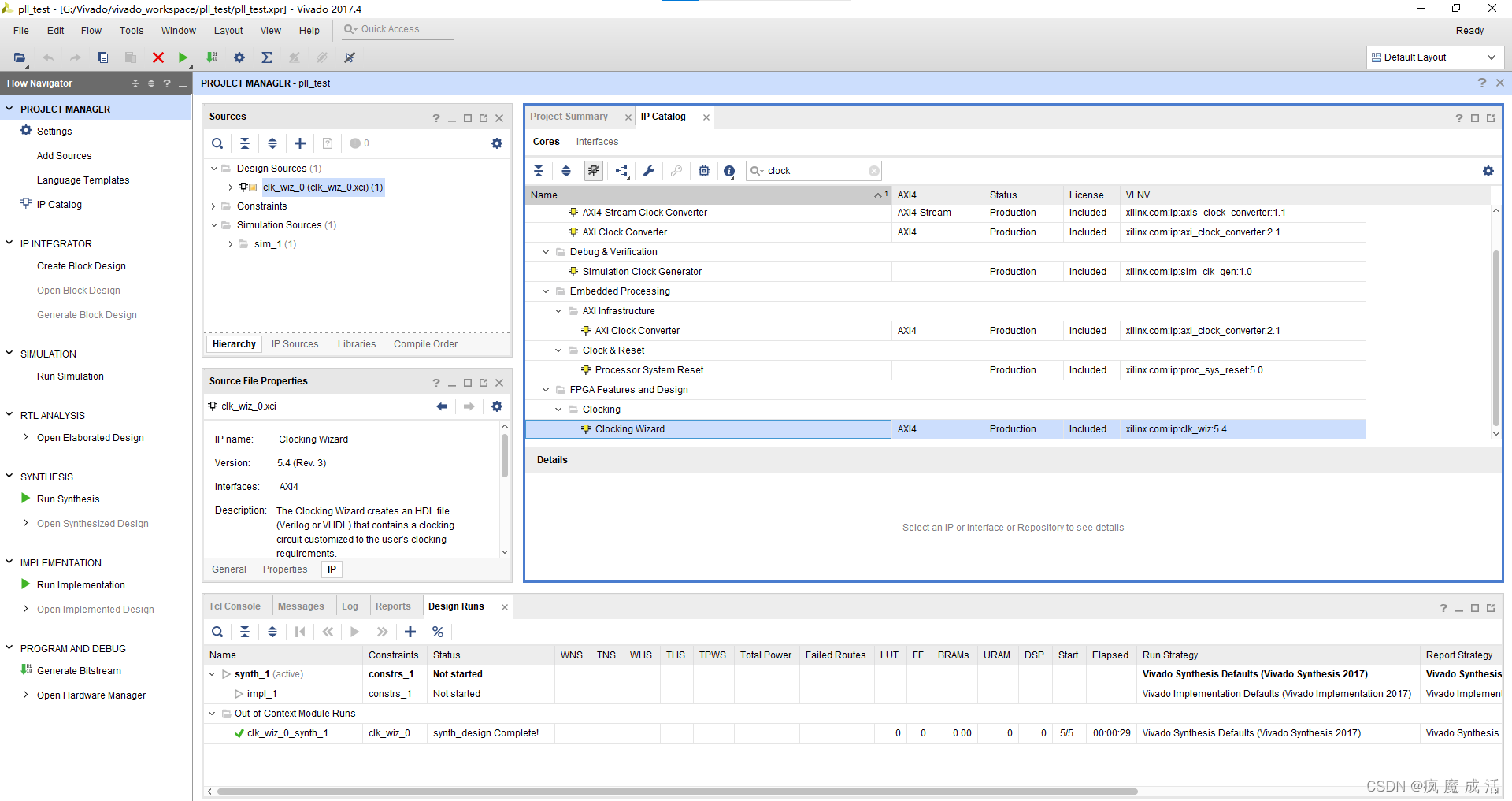

1、使用vivado创建一个工程

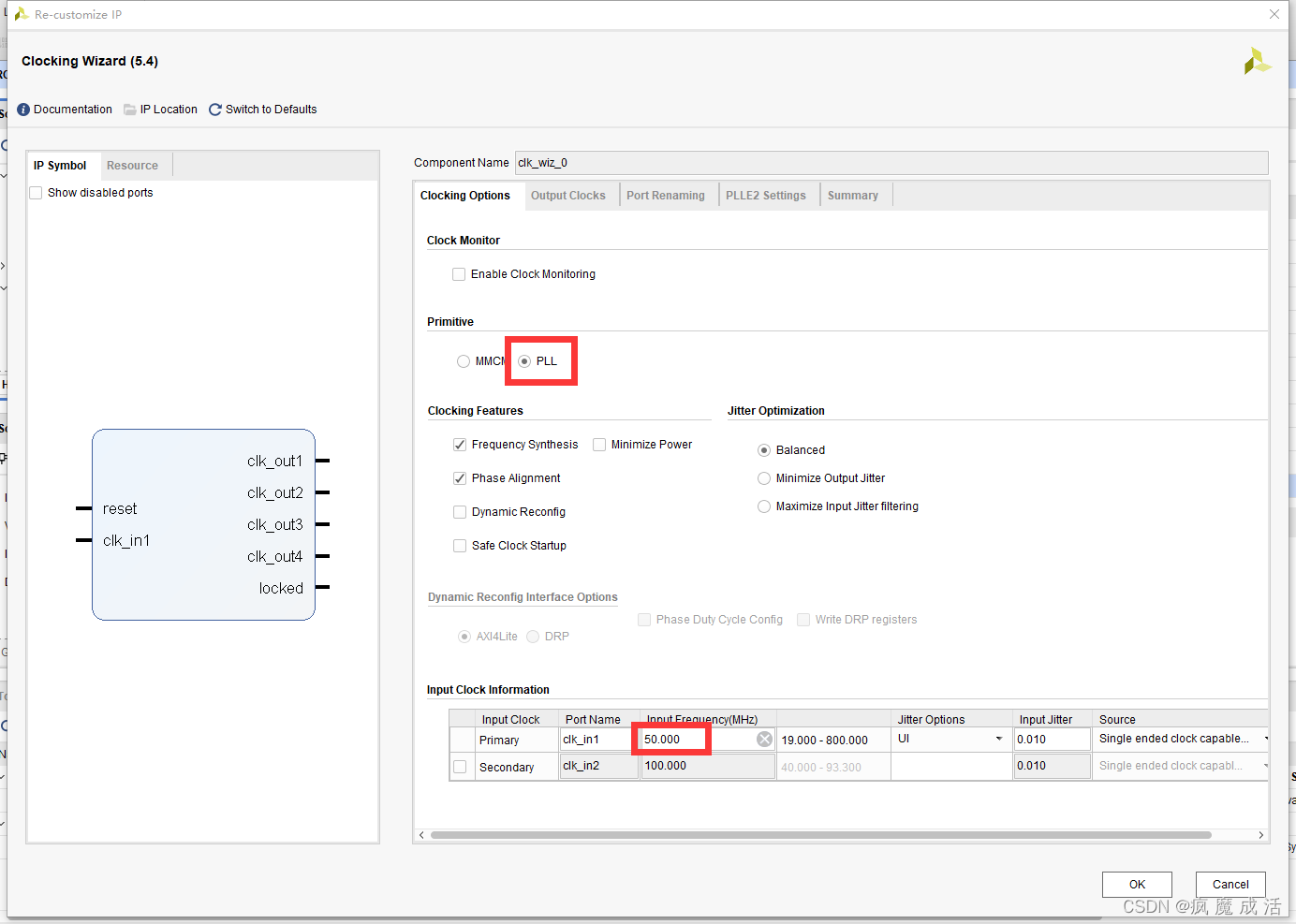

2、点击IP Catalog,搜索Clock Wizard,然后双击,本次实验使用PLL进行分频倍频,不动态改变相位,故选择PLL选项,并将时钟频率改变为50MHz,此处我们使用50MHz晶振作为时钟源

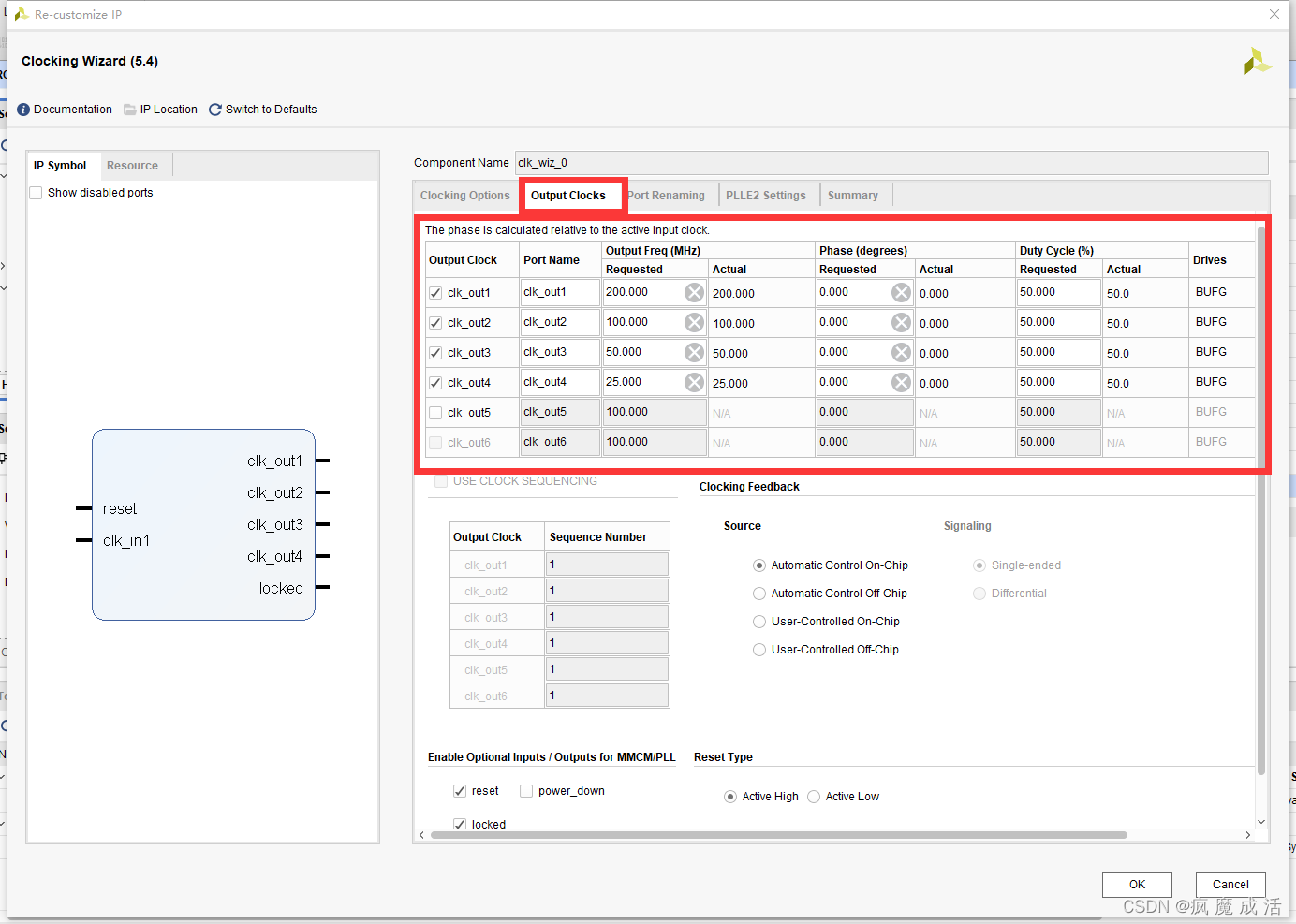

3、点击Output Clocks,配置产生的时钟频率,其他选项保持默认,点击ok,生pll ip核

此处我们使用了高电平复位,并使用locked信号,locked信号的作用是判断产生的时钟是否稳定输出,当locked为高电平时,此时输出的时钟信号是有效的,反之,则无效

4、编写Verilog源文件,找到pll ip核模块,并在顶层文件中进行例化

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5854

5854

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?