实现流程

所涉及文件:

链接: https://pan.baidu.com/s/1cbBHe2N6A1IIlp9fNB8jKw

提取码:obq1

第一步:使用matlab自带的图片转码指令进行RGB到YCbCr转码(1)

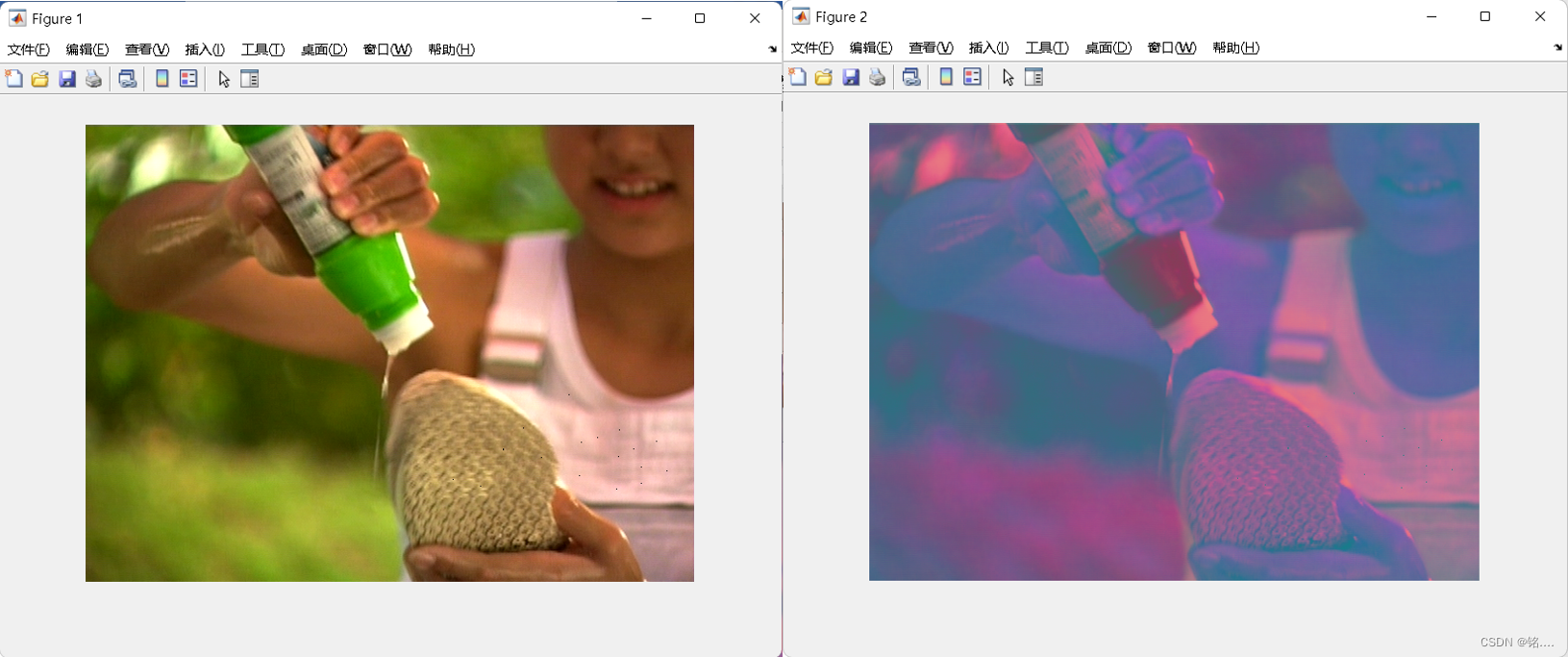

使用matlab将图片转成YCrCb格式并观察其效果,文件名为rgb_to_ycrcb.m,imread中路径名为bmp文件所处路径,得到如下输出结果

其中,figure1为原图片,figure2为转成YCrCb格数输出的文件。为更好的理解过程,在下一步中采用更加基本的程序来展示。

第二步:使用matlab自带的图片转码指令进行RGB到YCbCr转码(2)

新建txt空白文本文件,并分别命名为

matlab_result_Y.txt

matlab_result_Cb.txt

matlab_result_Cr.txt

使用matlab文件读取方法对bmp文件进行读取,文件名为rgb_to_ycrcb2.m(其中路径自行根据文件位置进行修改)。在本次实验中,本人将提取出来的信息绘制出YCbCr的RGB图像及灰度图,以对所提取的数据的准确性做了初步的验证。结果如下:

通过figure2,figure3可以看出,所提取出的信息应该是基本正确的。

第三步:在Vivado中编写SystemVerilog程序实现转码及初步仿真

**注:**整张图片时序输入将导致波形文件过大,Vivado可能会产生错误。故将代码分为两部分。第一部分中,在t=0时刻输出仿真所得YCbCr码并写入txt文件;第二部分中,仿真信号与模块输出信号输出一定时长的波形信号,在有限的波形信号中,比对两个信号是否一致即可。后仿真同理。

新建空白,编写SystemVerilog程序。本次作业在参考他人csdn上关于bmp文件的格式描述后(https://blog.csdn.net/zhong_ethan/article/details/121310111)得到启发。具体步骤如下:

新建空白txt文本文件

sv_tb_sim_result_Y.txt

sv_tb_sim_result_Cb.txt

sv_tb_sim_result_Cr.txt

编写模型文件rgb_to_ycrcb.sv与测试文件tb_rgb_to_ycrcb.sv。

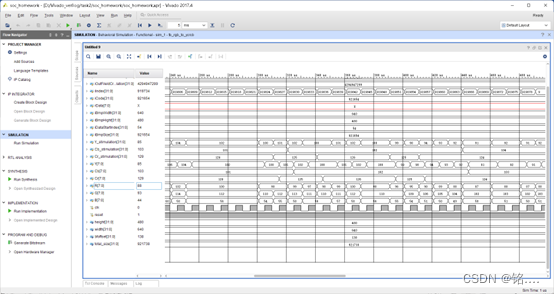

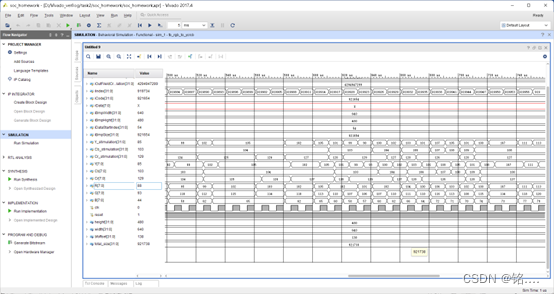

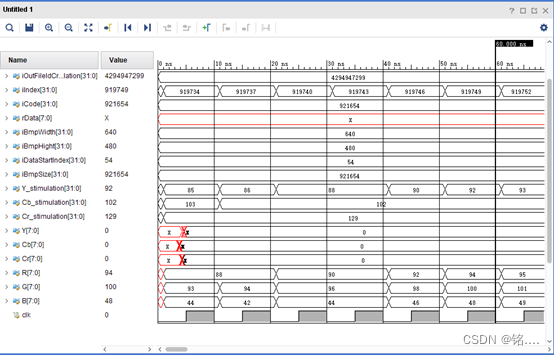

得到波形如图:

其中,R、G、B变量为读入的RGB数据,Y、Cb、Cr为经过模型文件的输出文件,Y_stimulation,Cb_stimulation,Cr_stimulation为仿真文件生成的数据,可以发现,大部分数据均一致,部分数据存在1的差异,本人认为此处属于系统误差,对于硬件而言,不能无限分配资源。在模块内部采用16bit寄存器进行运算,与double型变量位数存在差异,无法避免。

仿真得到的文件为

sv_tb_sim_result_Y.txt

sv_tb_sim_result_Cb.txt

sv_tb_sim_result_Cr.txt

对比matlab所得到的仿真文件

matlab_result_Y.txt

matlab_result_Cb.txt

matlab_result_Cr.txt

同样仅存在少许的系统误差,故认为这样的转换是有效的

第四步:在ncverilog中仿真对比

采用ncverilog进行波形生成比对。因老师留下的ncverilog文件不全,无法成功安装,而网络上的资源参差不齐,难以找到合适的,故此处跳过。此处分享一个CADENCE_LDV_V5.0的crack文件

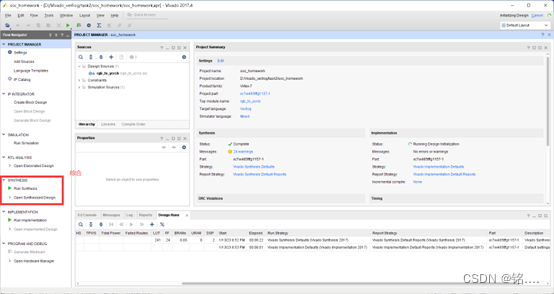

第五步:在综合及布局布线后后仿真

将可综合的sv文件编译,生成网表文件与延时文件。鉴于Vivado优秀的整合能力,能够更好的实现各个功能的集成,本次仿真采用vivado所附属的相应功能来完成本次作业。此方法与原方法存在差异有:软件差异、FPGA型号差异(vivado仅支持xlinx)、生成网表文件与延时文件格式差异(均为主流格式)。可与原方法互为补充。

综合成功后,Open Synthesized Design

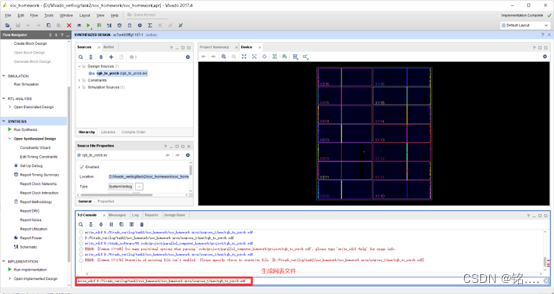

在控制台下输入以下命令:

write_edif D:/Vivado_verilog/task2/soc_homework/soc_homework.srcs/sources_1/new/rgb_to_ycrcb.edf

在指定路径下生成不含Xilinx IP 的rgb_to_ycrcb.edf网表文件

输入:

write_edif -security_mode all D:/Vivado_verilog/task2/soc_homework/soc_homework.srcs/sources_1/new/rgb_to_ycrcb.edf

则在相应位置生成包含Xilinx IP 的rgb_to_ycrcb.edf网表文件

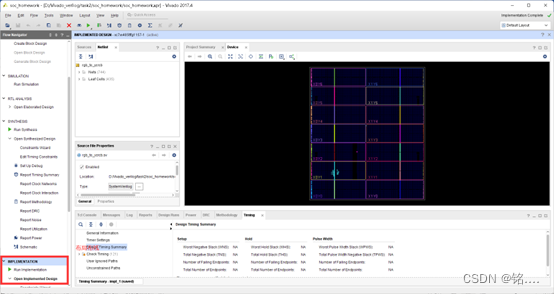

第五步,生成时序文件

参考网站https://blog.csdn.net/qq_40531974/article/details/117412025后,本人认为sdo文件可大致对应vivado中的sdf文件。

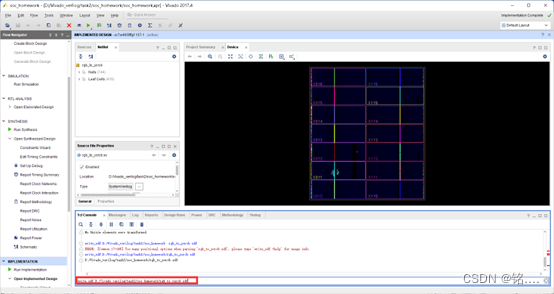

运行布局布线后,点击Open Implementation,在控制台输入:

write_sdf D:/Vivado_verilog/task2/soc_homework/rgb_to_ycrcb.sdf

则在相应位置生成rgb_to_ycrcb.sdf时序文件

第六步,后仿真

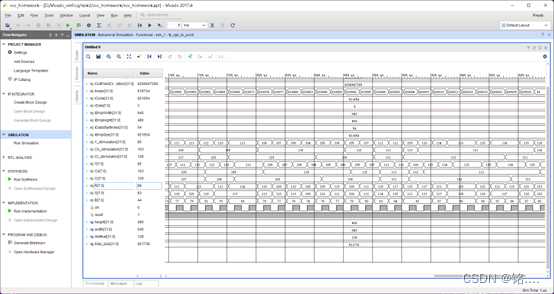

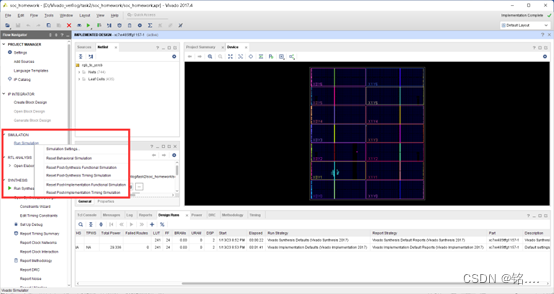

右键点击run stimulation,点击图中所需后仿真类别,得到生成的后仿真文件。

为区别之前生成的仿真文件,本人将之前的输出文件提前保存,将后续的文件输出文件命名为:

sv_tb_sim_result_Y_after_implementation.txt

sv_tb_sim_result_Cb_after_implementation.txt

sv_tb_sim_result_Cr_after_implementation.txt

对比可得,前后仿真文件结果,仅在前面有所区别,分析认为应该是FPGA从上电至正常运行必须有一定的准备时间。

第七步,将仿真结果得到的YCbCr带入matlab中生成bmp文件

由于前期工作思考不完善,这里对上述的tb_rgb_to_ycrcb.sv文件进行简单改变,得到tb_rgb_to_ycrcb2.sv文件。在此文件中,将输出结果命名为Y.txt,Cb.txt,Cr.txt。

编写matlab图片读取与生成文件generate_bmp.m,得到输出如图:

可以看出,与原图完全相符,认为本次作业成功完成

3639

3639

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?