Questa Sim(时序测试)

作者:Saint

掘金:https://juejin.im/user/5aa1f89b6fb9a028bb18966a

微博:https://weibo.com/5458277467/profile?topnav=1&wvr=6&is_all=1

GitHub:github.com/saint-000

知乎:https://www.zhihu.com/people/saint-80-61/columns

Questa Sim和ModelsSim是工业界最优秀的语言仿真器,两者都能用于FPGA的功能测试、性能测试、接口测试、时序测试、逻辑测试等测试类型,此节针对时序测试进行讨论,相同步骤查看功能测试相关描述。

时序测试:

1.生成时序文件(注意:此节分享仿真平台添加约束文件的方式进行时序测试,开发平台链接三方仿真平台进行时序测试的方法会在时序测试补充中描述)

被测件的开发平台不同,如何生成SDF文件、SDO文件操作亦不同,常用开发平台:ISE、Vivado、QuartusII;在这些开发平台中对执行布局布线操作后网表进行设置三工况,随着三工况设置后,根目录下的时序文件也会更新。

最大工况:最大温度、最小电压

典型工况:典型温度、典型电压

最小工况:最小温度、最大电压

根据FPGA芯片的用户手册查询相应的温度、电压

赛灵思芯片查询Datasheets

1.1在ISE中生成SDF时序文件

- 单击User Constraints\Creat Timing Constraints、在弹出界面中单击

OperatingConditions、填写最小、经典、最大三种工况的电压和温度值,保存UCF约束文件 - ISE界面中单击Place & Route\Generate Post-Place &

Route Simulation Model;

工程文件中自动生成netgen文件夹,在该文件夹目录下自动生成SDF时序文件

1.2在QuartusII中生成SDO时序文件

对被测件进行TimeQuest Timing Analysis

点选TimeQuest Timing Analyzer,新建SDC约束文件

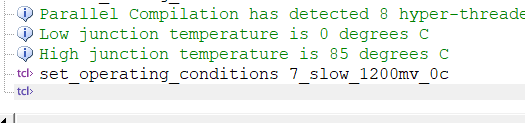

Set Operating Conditions选择相应的工况:

更新SDC约束文件

执行EDA Netlist Writer后在工程根目录…\simulation\modelsim下生成不同工况的SDO时序文件

1.3在Vivado中生成SDF时序文件

将被测件执行布局布线

布局布线后选择Report Implementation Summary

在Timing Settings中选择三工况

最大工况:Slow:max Fast:min

最小工况:Slow:min Fast:max

典型工况:Slow:min_max Fast:min_max

在仿真设置中添加仿真平台、仿真顶层文件及路径

链接三方仿真平台路径

执行后仿

在…\sim_1\impl\timing\modelsim路径下生成SDF时序文件

2.添加被测件和时序文件

将生成的SDF/SDO时序文件添加到Questa Sim

Apply to Region可以设置工况类型,忽略时序文件警告、减少时序错误

在Design中选中work中的仿真顶层文件

执行仿真

在三种工况下通过观察时序图与设计接口时序是否符合要求进行时序测试

599

599

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?