1.L1数据缓存的读操作:

LDR Rx,[addr]

- L1数据缓存的访问从指令发射到Load/Store单元,在单元中计算地址,产生访存请求

- 仲裁器判断是否接受请求。若不接受,Load/Store会等待直到仲裁器空闲下来处理这个请求。不接受的可能原因(处理资源不足):1)MSHR单元没有足够空间; 2)缓存资源被占用。若接受,冲裁器会在指令流水线中调度产生一个向寄存器文件的写回事件,表示将在未来占用寄存器文件的写端口。

- 冲裁器检查缓存是否命中。若Miss,则将访存请求写入MSHR单元,让MSHR与下一级存储交互。如果缓存空间不足,未命中的读请求需要进行替换操作,若被替换的数据为dirty,还要先将dirty数据写回。若Hit,则将数据取出,稍后写回寄存器文件。

- MSHR处理后的外部访问请求被发送到存储管理单元(Memory Manage Unit,MMU)将虚拟地址转换为实地址。再通过Interconnection Network传递给对应的memory partiton unit

- 数据从下一级存储返回时,仍经过MMU处理一些信息(比如等待数据的指令、待写回的寄存器编号),告知Load/Store单元重播刚才访问缺失的指令,同时返回的数据通过Fill Unit回填到SRAM阵列中,完成缓存的更新操作,并锁定这一行不能被替换,直到它被读取,从而保证刚刚的指令一定命中

2.L1数据缓存的写操作:

L1数据Cache是一个私有的,每个SIMT核心一个,非阻塞的第一级Cache,用于对于本地和全局存储空间的访问。L1 Cache不分bank,每个SIMT核心cycle可以为两个合并的存储器访问请求提供服务。一个存储器请求不能跨越2个或更多的Cache line。也要注意,L1数据Cache没有一致性协议。

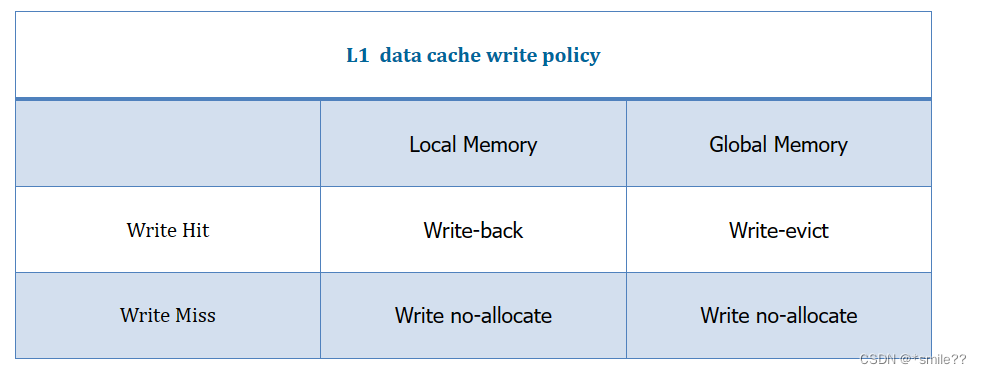

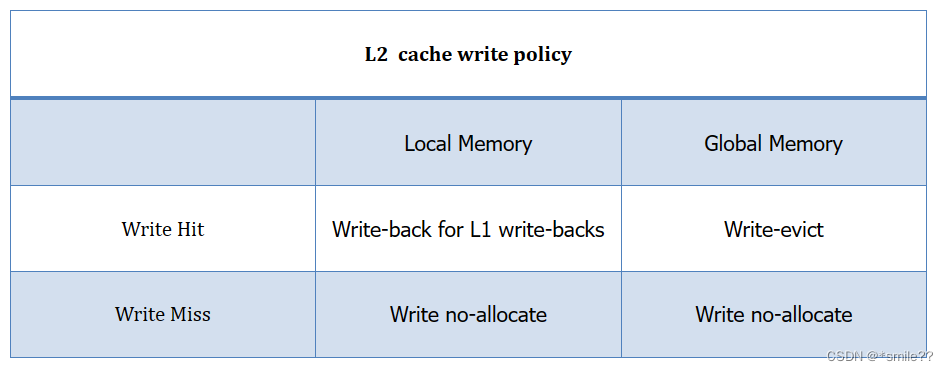

下表总结了L1数据Cache的写策略:

Write-evict:将更新的数据写入共享L2缓存的同时,将L1数据缓存中相应的缓存行设置为无效(invalid)

4360

4360

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?