FPGA任意波形函数信号发生器的设计

平台: quartus II 13.0

仿真:signal tap II

语言:VHDL

方式:原理图bdf输入

芯片:Cyclone IV E: EP4CE6E22C8

实验目的

设计一任意波函数信号发生器,具备以下两功能:

①能输出标准正弦波波形。

②能输出任意函数波形。

一、实验系统框图

![[外链图片转存失败,源站可能有防盗示例:pandas 是基于NumPy 的一种工具,该工具是为了解决数据分析任务而创建的。]!链机制,建上https://传(imblog.csdnimg.cn/229d47e11de74c5783bAe1f276ca8df3.zng?8px-oss-process=image/watermark,type_d3F5LXplbmhlaQ,shado16,text_Q1NETiBAd2VpeGluXzQ2NzE5NjA1,size_02,color_FFFFFF,t_65,g_se,x_167)(https://imgblog.csdnimg.cn/229d47e11de74c5783b8e1f276ca8df3.png?x-oss-process=image/watermark,type_d3F5LXplbmhlaQ,shadow_50,text_Q1NETiBAd2VpeGluXzQ2NzE5NjA1,size_20,color_FFFFFF,t_70,g_se,x_16)]](https://i-blog.csdnimg.cn/blog_migrate/6b09c8cbf36b0b4f21824271d18dc315.png)

二、顶层设计文件

创建工程,新建bdf文件,绘制原理图

三、用到的宏模块介绍

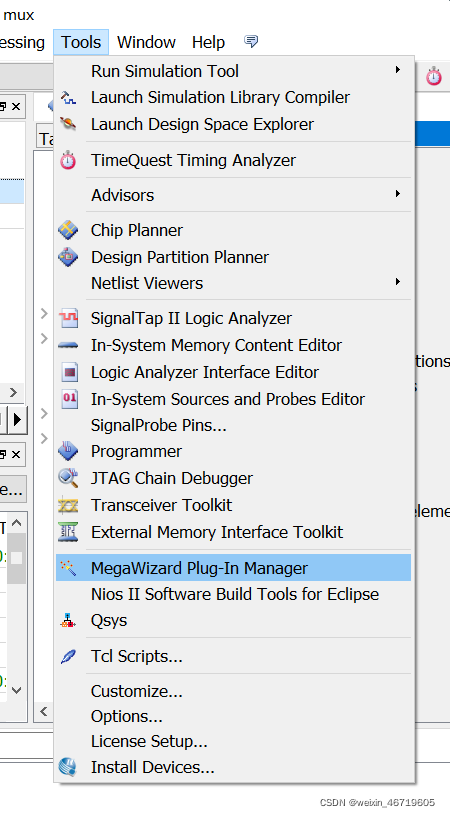

首先明确实验用到的宏模块操作是在tool——MeGaWizard Plug-In Manager中(如下图)

各种宏模块的参数设置根据想要的设置就行,这里就不过多展示

该顶层文件大致分为5个模块,根据上面的顶层文件从左到右依次介绍:

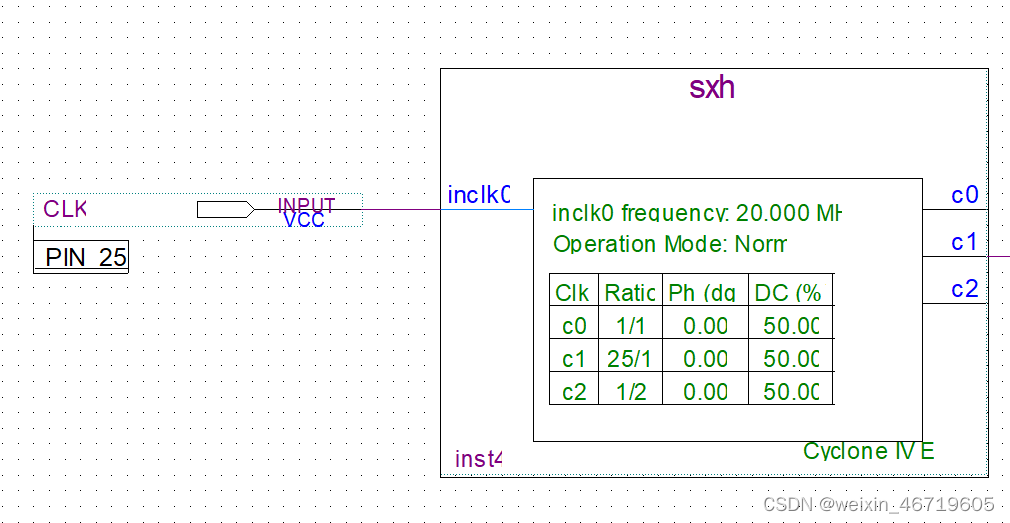

sxh——锁相环,由MeGaWizard Plug-In Manager中的ALTPLL宏模块构成。(如下图)

将板子上的pin25(我用的板子上pin25引脚是时钟信号clk,晶振20mhz)进行分频,这次仿真里我用的c1是扩大了25倍,倍频后送到adder32模块中

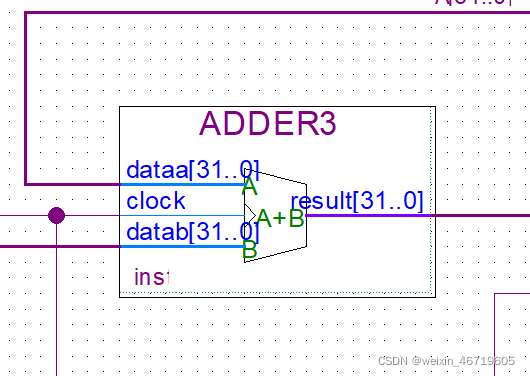

adder32——32位加法器,由LPM_ADD_SUB宏模块构成。设置了2阶流水线结构,使其在时钟控制下有更高的运算速度和输入数据稳定性。

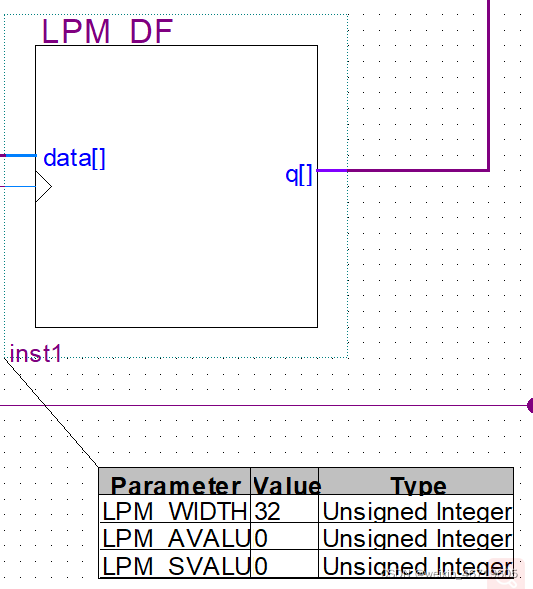

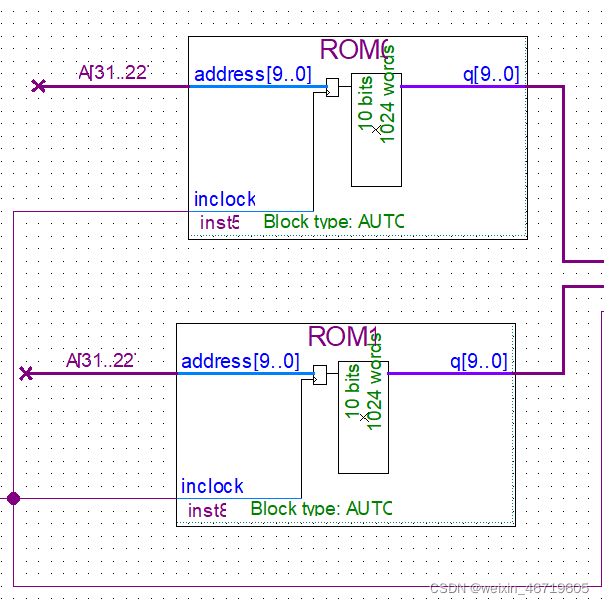

LPM_DFF——32位寄存器,由LPM_DFF宏模块构成;ADDER32和LPM_DFF一起构成一个32位的相位累加器。其高10位A[31..22]作为波形ROM的地址。注意其中参数的设置,因为数据是32位的LPM_WIDTH参数就设为32

ROM0、ROM1——波形数据存在ROM中,由ROM-PORT1宏模块构成。

ROM0我放入的是锯齿波,ROM1为正弦波数据。

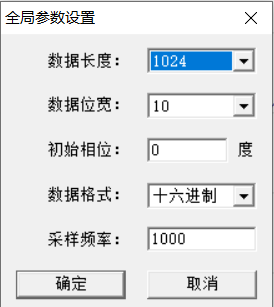

由于该数据的生成需要靠.mif文件生成一个周期内的波形数据,在这里我推荐一个mif文件自动生成的工具叫mifmaker,可以自行百度下载,如下图,可以自己选择数据和波形。

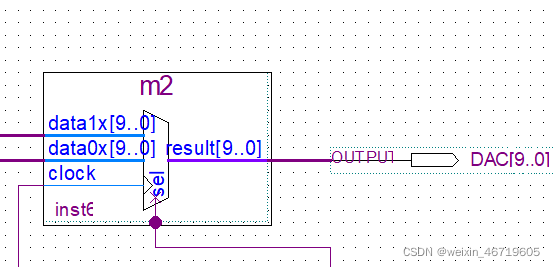

m2——多路选择控制器,由LPM_MUX宏模块构成

由于本次设计是按下K1键后可以切换波形,需要一个2选一选择控制器来控制输入的数据

四、本实验DDS原理

频率控制字B[31..0]与由DAC[9…0]驱动的DAC正弦信号的频率关系为:

f(out) = { B[31..0]/(2^32) } * f(clk)

其中f(out)为DAC输出的正弦波信号频率, f(clk)为CLK的时钟频率。直接输入是20MHz,接入锁相环可以达到更高的频率,且频率上限要看DAC的速度。且数据输入频率需要一个相同的工作时钟驱动,即为图中的DAC_CLK,它作用于外部DAC的工作时钟

五、Singal tap II仿真

仿真前需要将文件编译一遍,锁定好引脚,将仿真文件添加到工程中再编译一遍,最后下载到板子中进行仿真

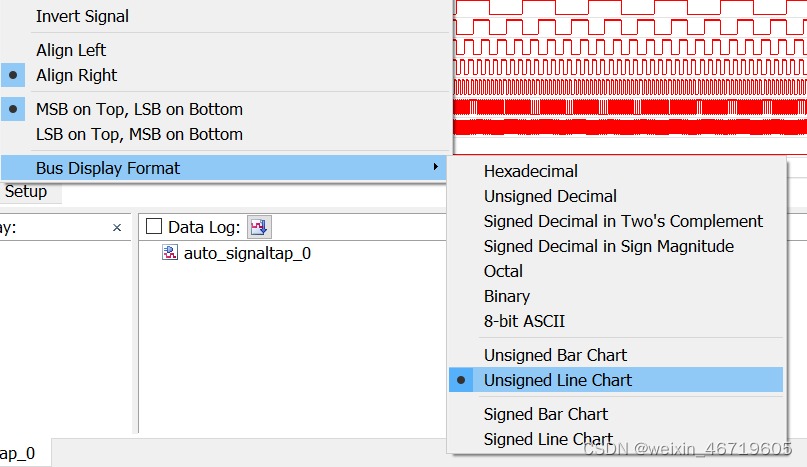

仿真中需要注意的是setup设置好采样深度,尽可能多观察到一些周期,且需要将数据线性模拟,如下设置:

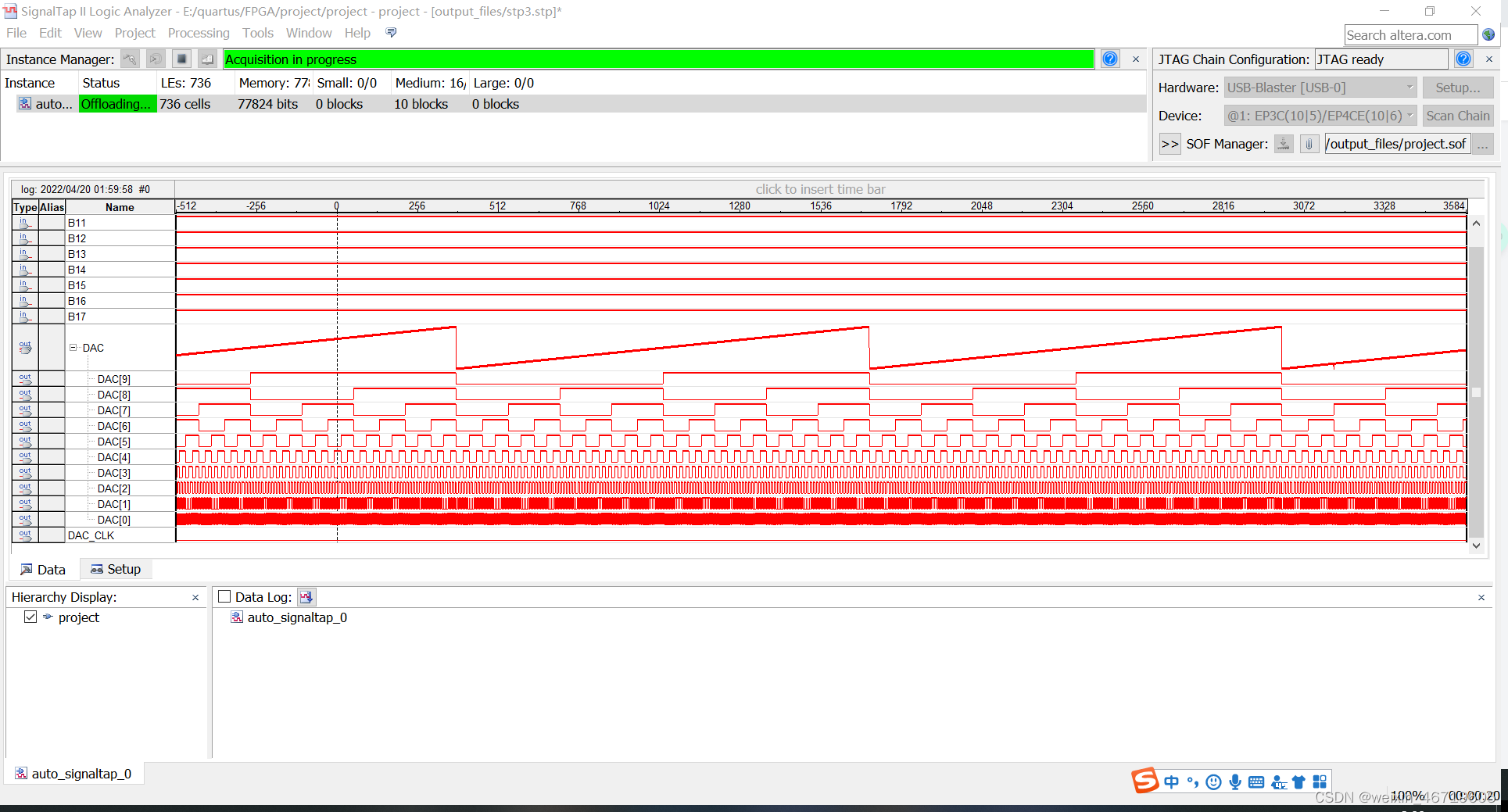

仿真结果:不按下K1为锯齿波

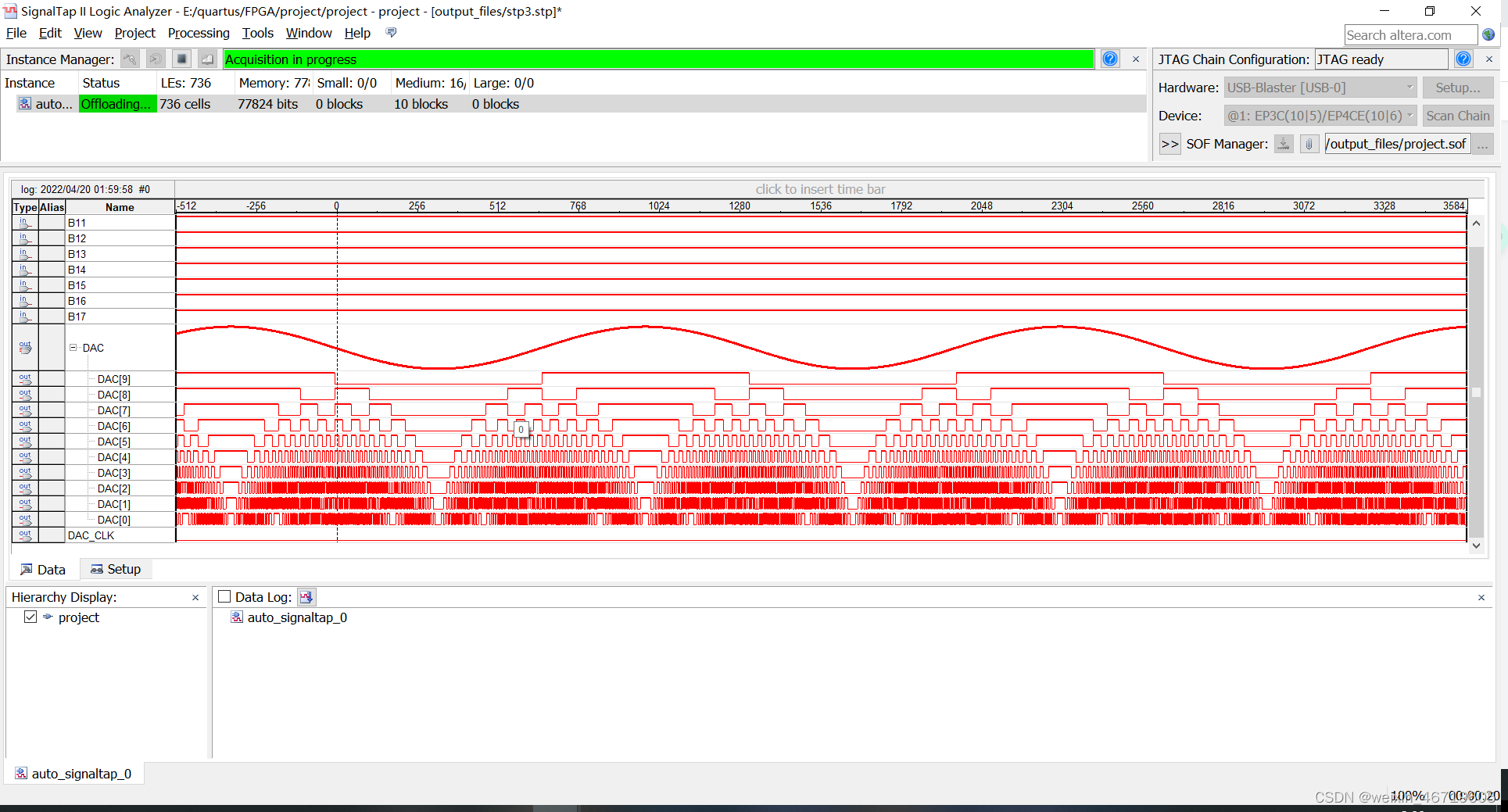

按下K1为正弦波:

总结

本文是关于FPGA学习实验中任意波形函数信号发生器的设计和仿真,仅供参考,本人新手一枚,如有错误还望各位在评论区指正;有疑问可以评论区提,虽然我也不一定知道(^ △ ^)

使用quartus II 13.0和VHDL,设计了一个基于Cyclone IV E EP4CE6E22C8 FPGA的任意波形函数信号发生器。该设计包括锁相环、32位加法器、32位寄存器、ROM模块和多路选择器,能够输出正弦波和锯齿波。通过Signal Tap II进行仿真,按下K1键可切换波形。

使用quartus II 13.0和VHDL,设计了一个基于Cyclone IV E EP4CE6E22C8 FPGA的任意波形函数信号发生器。该设计包括锁相环、32位加法器、32位寄存器、ROM模块和多路选择器,能够输出正弦波和锯齿波。通过Signal Tap II进行仿真,按下K1键可切换波形。

954

954

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?