题目来源:https://www.nowcoder.com/practice/9f91a38c74164f8dbdc5f953edcc49cc?tpId=302&tags=&title=&difficulty=0&judgeStatus=0&rp=0&sourceUrl=%2Fexam%2Foj%3Fpage%3D1%26tab%3DVerilog%25E7%25AF%2587%26topicId%3D302

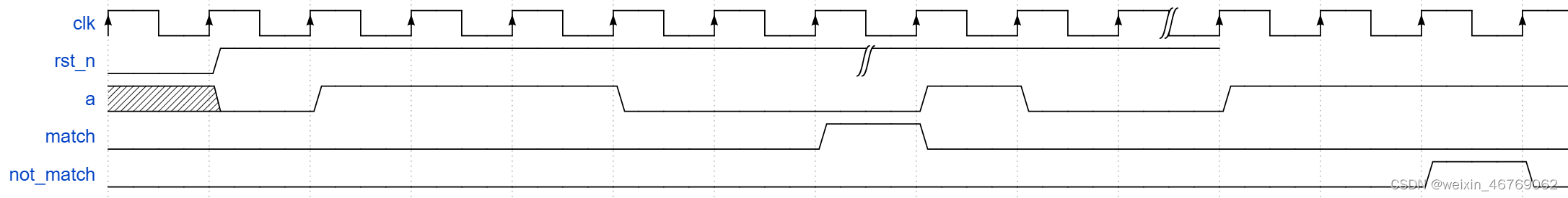

请编写一个序列检测模块,检测输入信号(data)是否满足011100序列, 要求以每六个输入为一组,不检测重复序列,例如第一位数据不符合,则不考虑后五位。一直到第七位数据即下一组信号的第一位开始检测。当信号满足该序列,给出指示信号match。当不满足时给出指示信号not_match。

代码实现:

module sequence_detect(

input clk,

input rst_n,

input data,

output reg match,

output reg not_match

);

fsm ///

localparam IDLE = 3’d0,

S0 = 3’d1,

S1 = 3’d2,

S2 = 3’d3,

S3 = 3’d4,

S4 = 3’d5,

S5 = 3’d6;

reg [2:0] state, next_state;

reg [2:0] cnt;

always @(posedge clk or negedge rst_n) begin

if(!rst_n) state <= 3’d0;

else state <= next_state;

end

always @(*) begin

case(state)

IDLE : next_state = !data ? S0 : IDLE;

S0 : next_state = data ? S1 : IDLE;

S1 : next_state = data ? S2 : IDLE;

S2 : next_state = data ? S3 : IDLE;

S3 : next_state = !data ? S4 : IDLE;

S4 : next_state = !data ? S5 : IDLE;

S5 : next_state = !data ? S0 : IDLE;

default : next_state = IDLE;

endcase

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

cnt <= 3’d0;

else

cnt <= cnt == 3’d5 ? 0 :cnt + 1’b1;

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

match <= 1’b0;

not_match <= 1’b0;

end

else begin

match <= next_state == S5 & cnt == 3’d5;

not_match <= next_state != S5 & cnt == 3’d5;

end

end

shift register

reg [5:0] data_lock;

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

data_lock <= 6’d0;

else

data_lock <= {data_lock[4:0], data};

end

reg [2:0] cnt;

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

cnt <= 3’d0;

else

cnt <= cnt == 3’d5 ? 3’d0 : cnt + 1;

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

match <= 1’b0;

not_match <= 1’b0;

end

else begin

match <= {data_lock, data}== 6’b011100 & cnt == 3’d5;

not_match <= {data_lock, data} != 6’b011100 & cnt == 3’d5;

end

end

/*

reg [2:0] cnt;

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

cnt <= 3’d0;

else

cnt <= cnt == 3’d6 ? 3’d1 : cnt + 1;

end

always @(*) begin

if(!rst_n) begin

match <= 1’b0;

not_match <= 1’b0;

end

else begin

match <= data_lock== 6’b011100 & cnt == 3’d6;

not_match <= data_lock != 6’b011100 & cnt == 3’d6;

end

end

*/

endmodule

1220

1220

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?