题目1:

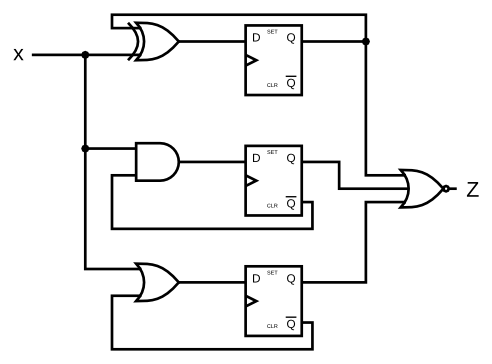

给定有限状态机电路,如图所示,假设在机器启动之前,D触发器最初复位为零。

构建此电路。

模块声明

module top_module (

input clk,

input x,

output z

);

观察电路图可得代码如下:

module top_module (

input clk,

input x,

output z

);

reg q1,q2,q3;

always@(posedge clk)

begin

q1 <= q1^x;

q2 <= !q2 & x;

q3 <= !q3 | x;

end

assign z = !(q1|q2|q3);

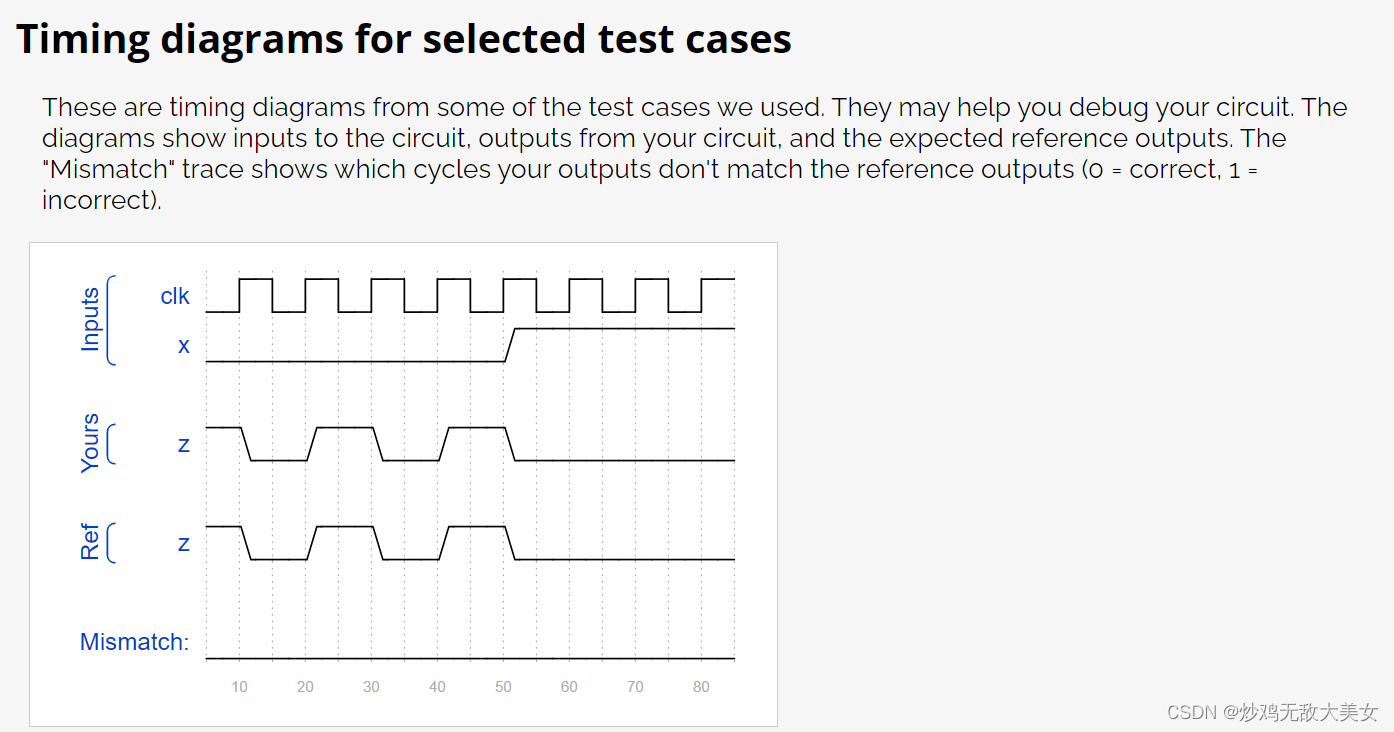

endmodule仿真结果如下:

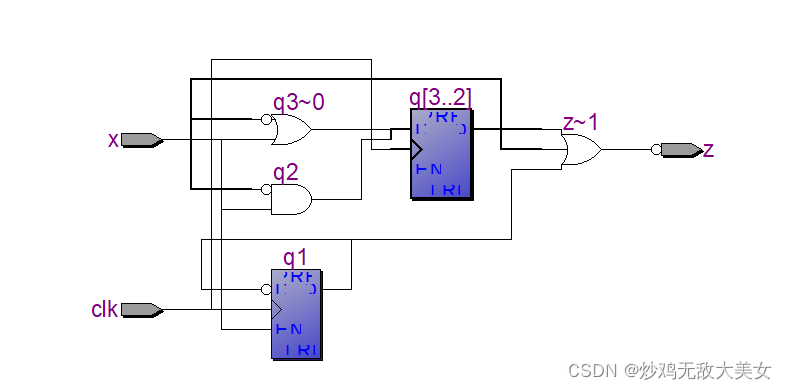

使用quartus ii画出的逻辑图如下:

题目2:

JK 触发器具有以下真值表。实现仅具有 D 型触发器和门的 JK 触发器。注意:Qold 是正时钟边沿之前的 D 触发器输出。

| J | K | Q |

|---|---|---|

| 0 | 0 | Qold |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | ~Qold |

模块声明

module top_module (

input clk,

input j,

input k,

output Q);

观察真值表可得代码如下:

module top_module (

input clk,

input j,

input k,

output Q);

always@(posedge clk)

begin

case({j,k})

2'b00: Q <= Q;

2'b01: Q <= 0;

2'b10: Q <= 1;

2'b11: Q <= !Q;

endcase

end

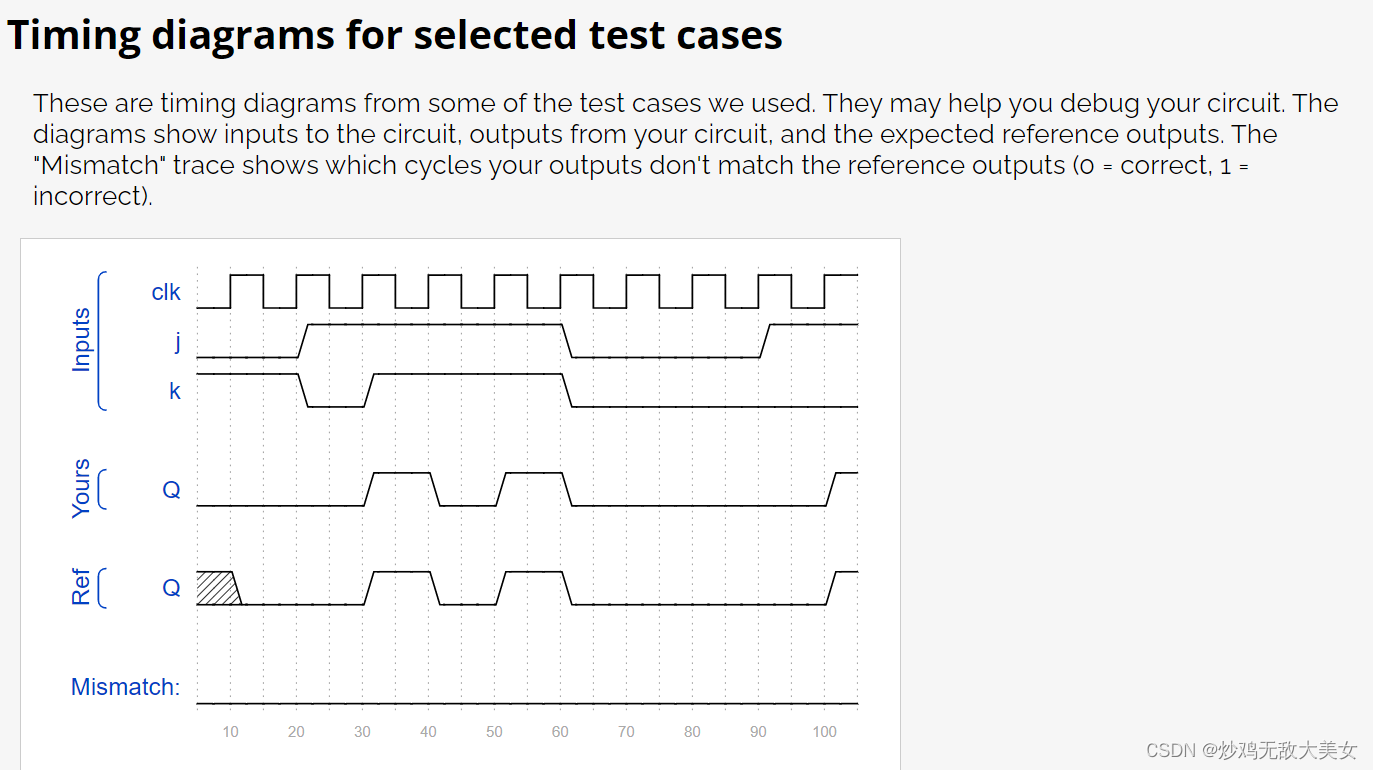

endmodule仿真结果如下:

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?