目录

一.概述

1)触发器用于记忆1位二进制信号,其中包括有两个能自动保持的状态,根据输入信号可以置0或1

2)分类:按触发方式分为按触发方式(电平,脉冲,边沿);按逻辑功能:包括RS、JK,D,T触发器)

二.SR锁存器

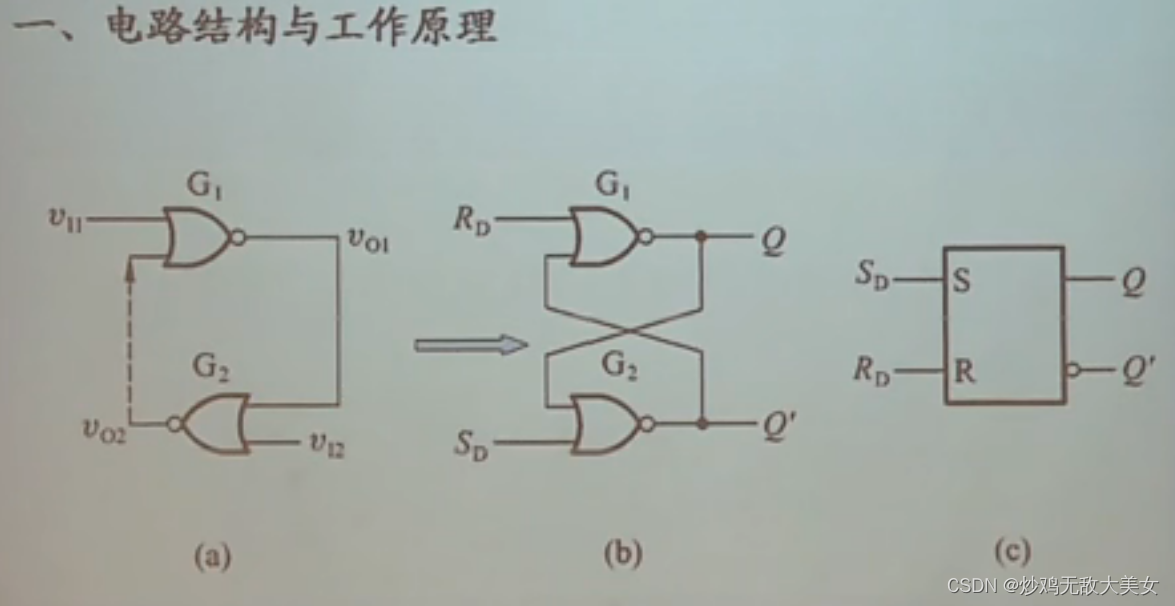

1)SR锁存器是所有触发器的基础,其电路结构图(或非门构成)和封装后的图形符号如下图所示。和

分别为置1端和置0端。

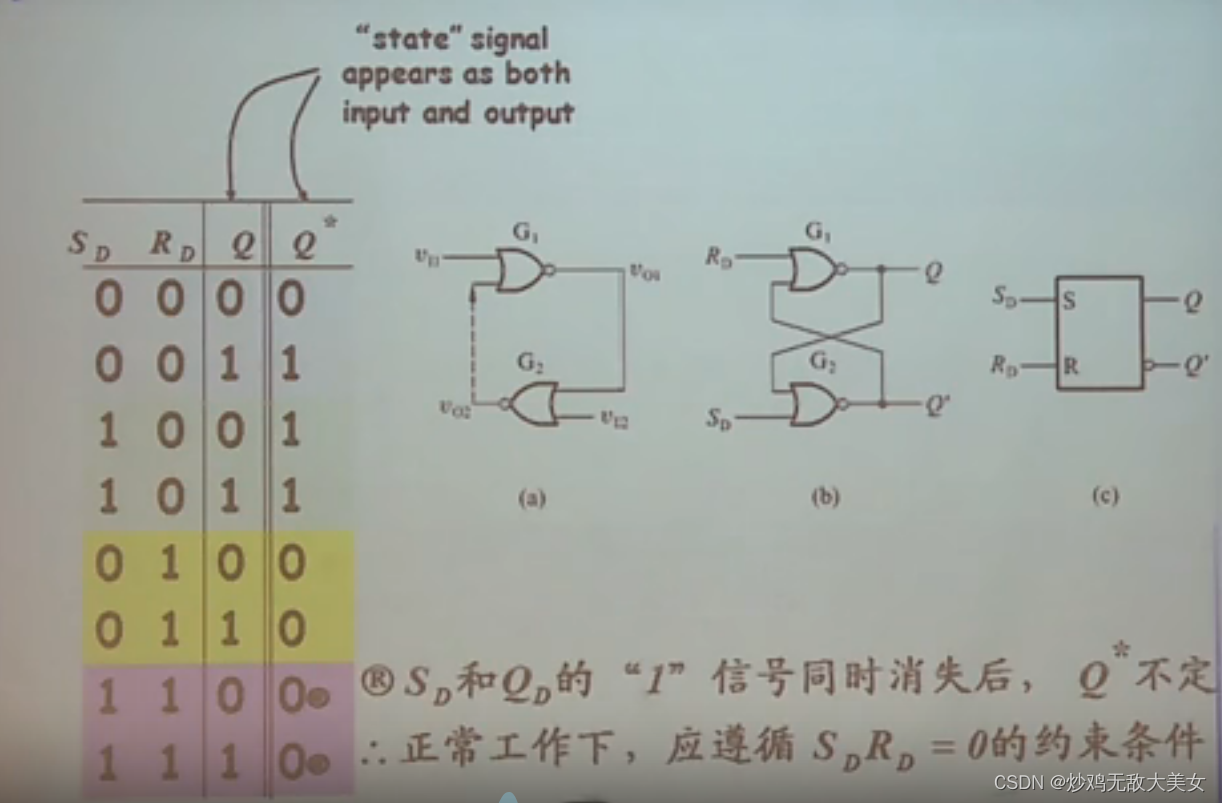

2)用或非门组成的SR锁存器的特性表

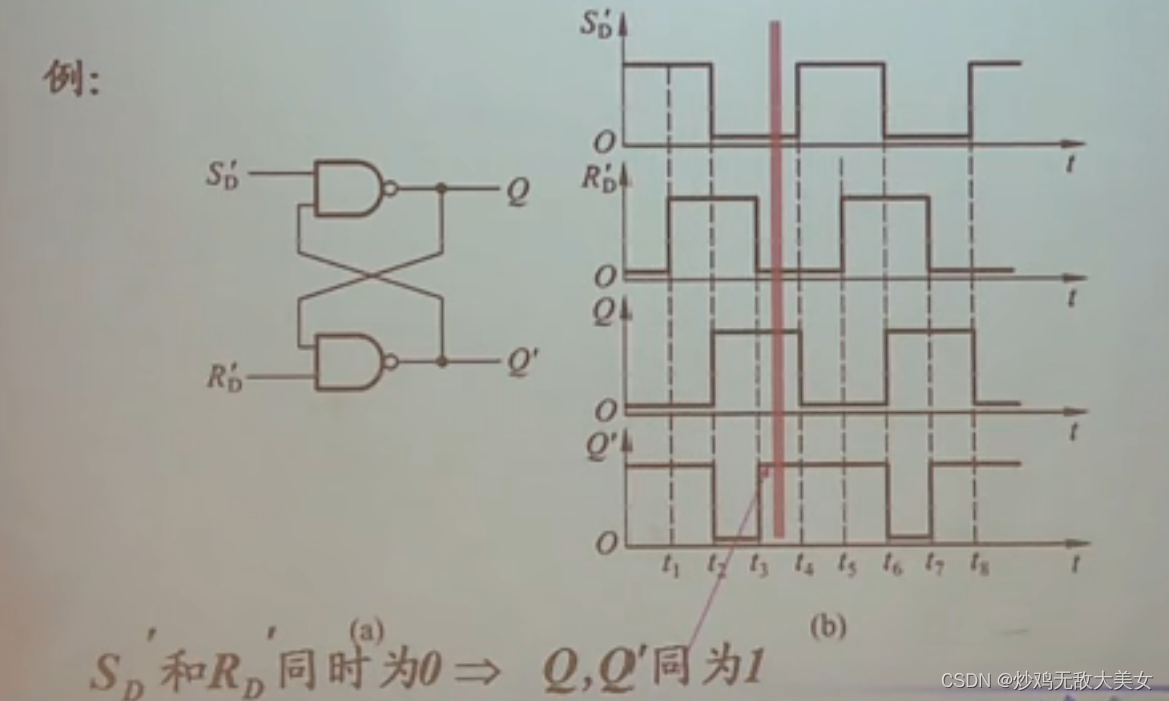

3)动作特点(用与非门作为例子)

在任何时刻,输入都能直接改变输出的状态。其中和

,其中

是置1输入端,

是置0输入端。

注意:SR锁存器存在着约束条件S&R=0,这是由于如果S和R同时有效的话,输出Q和Q'会出现不定状态;又或者当S和R不是同时有效,例如S先有效,R后有效,电路输出应该先置1,但如果当R有效到来后,S和R的有效信号同时变为0,这将影响着电路输入输出的决策(即输出不知道是0还是1),这会给电路工作带来困扰。

由此,可以考虑引入时钟信号对S和R进行控制。

三、按照电路的基本结构来分

按照电路的基本结构来区分触发器可分为:由电平触发的电平触发器、由边沿触发的边沿触发器、由脉冲触发的脉冲触发器。

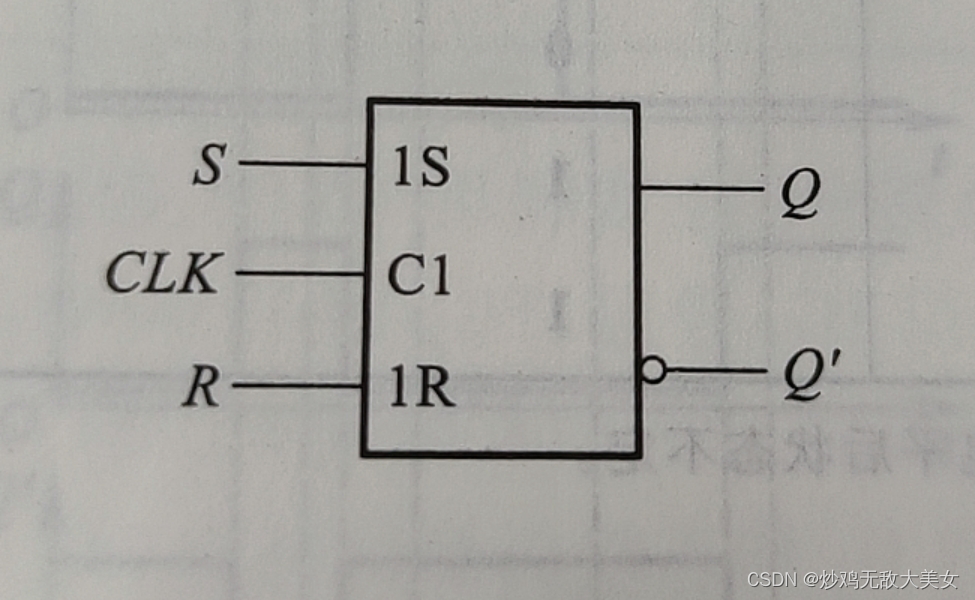

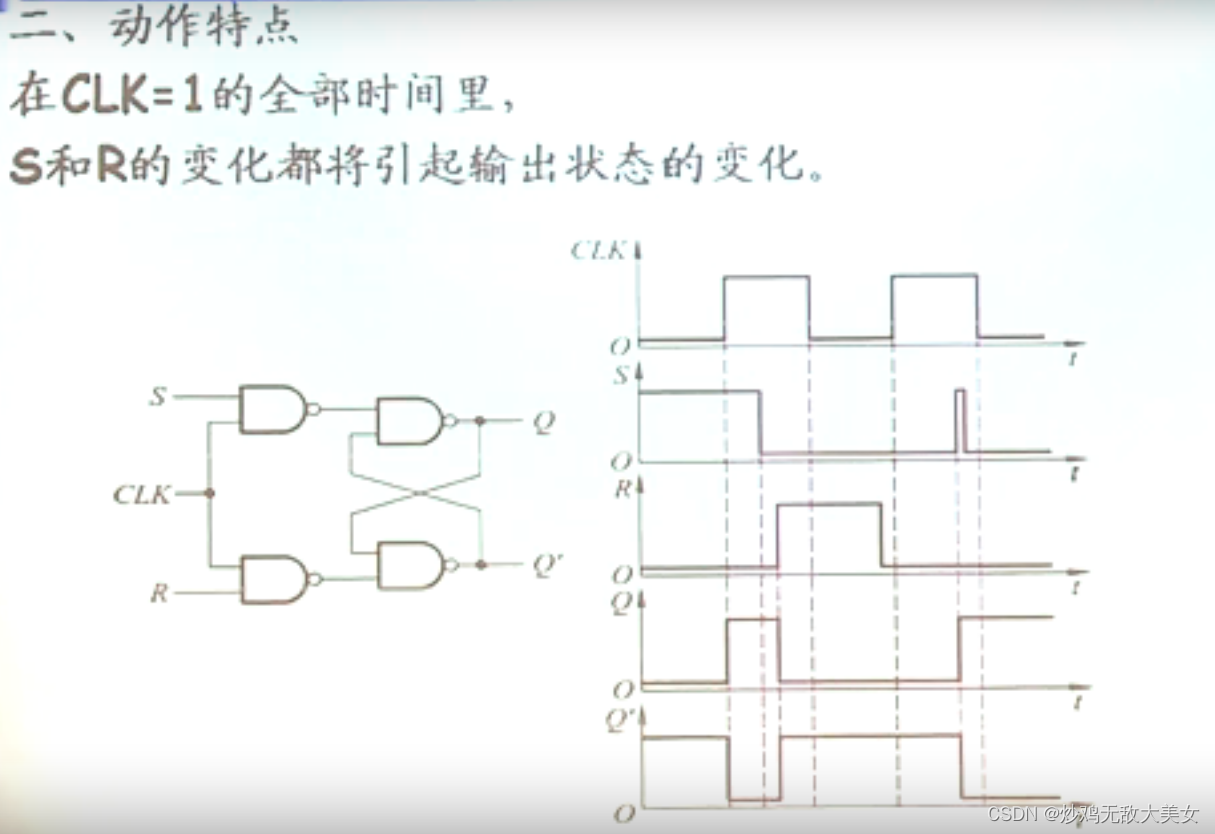

3.1.SR触发器(电平触发的触发器、RS触发器)

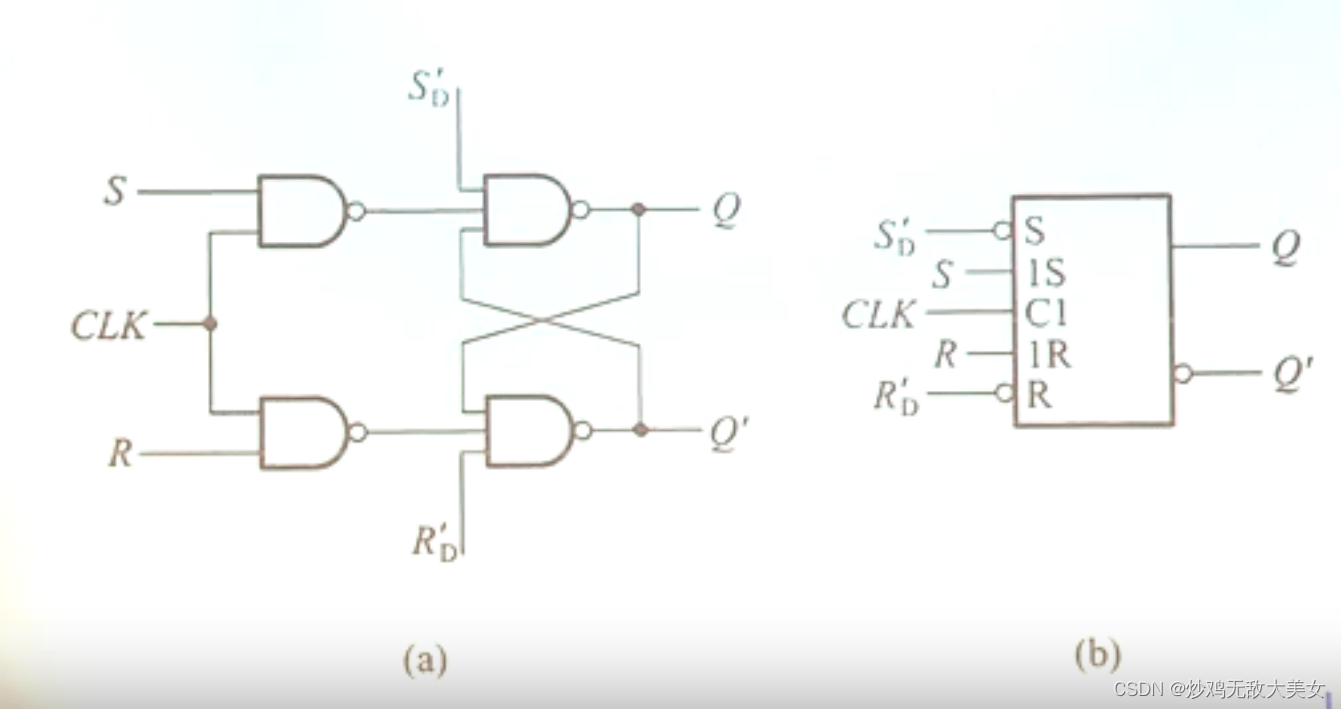

clk被称为触发端。第一幅图为其电路结构和特性表,第二幅图为SR触发器的图形符号。

2)下图表示带有异步置位。复位端的电平触发SR触发器。

注意:SR触发器虽然引入了时钟信号控制输入和输出,但是在以SR锁存器作为基础的条件上,其约束条件问题依然存在,即S和R同时置0或者置1的情况下,两者信号同时消失的话,输出信号的状态依然会出现不定状态。

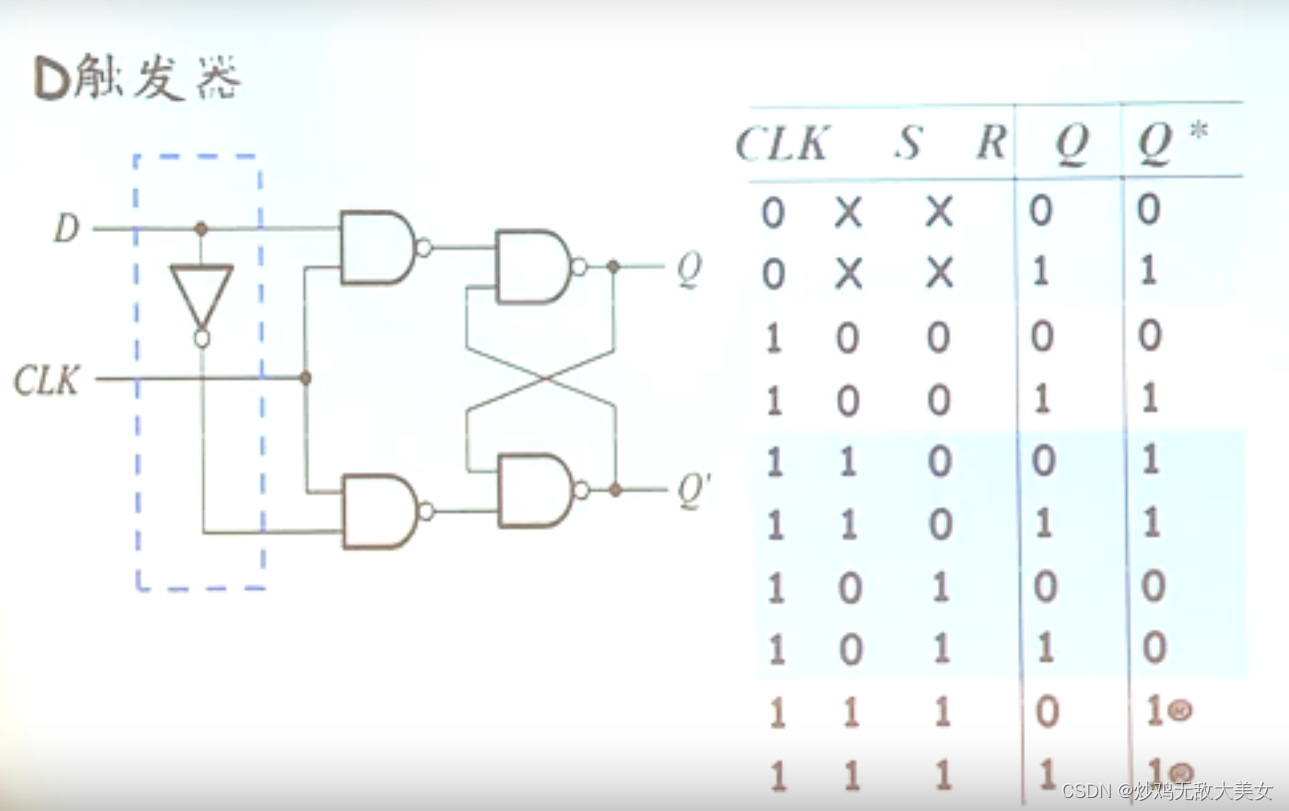

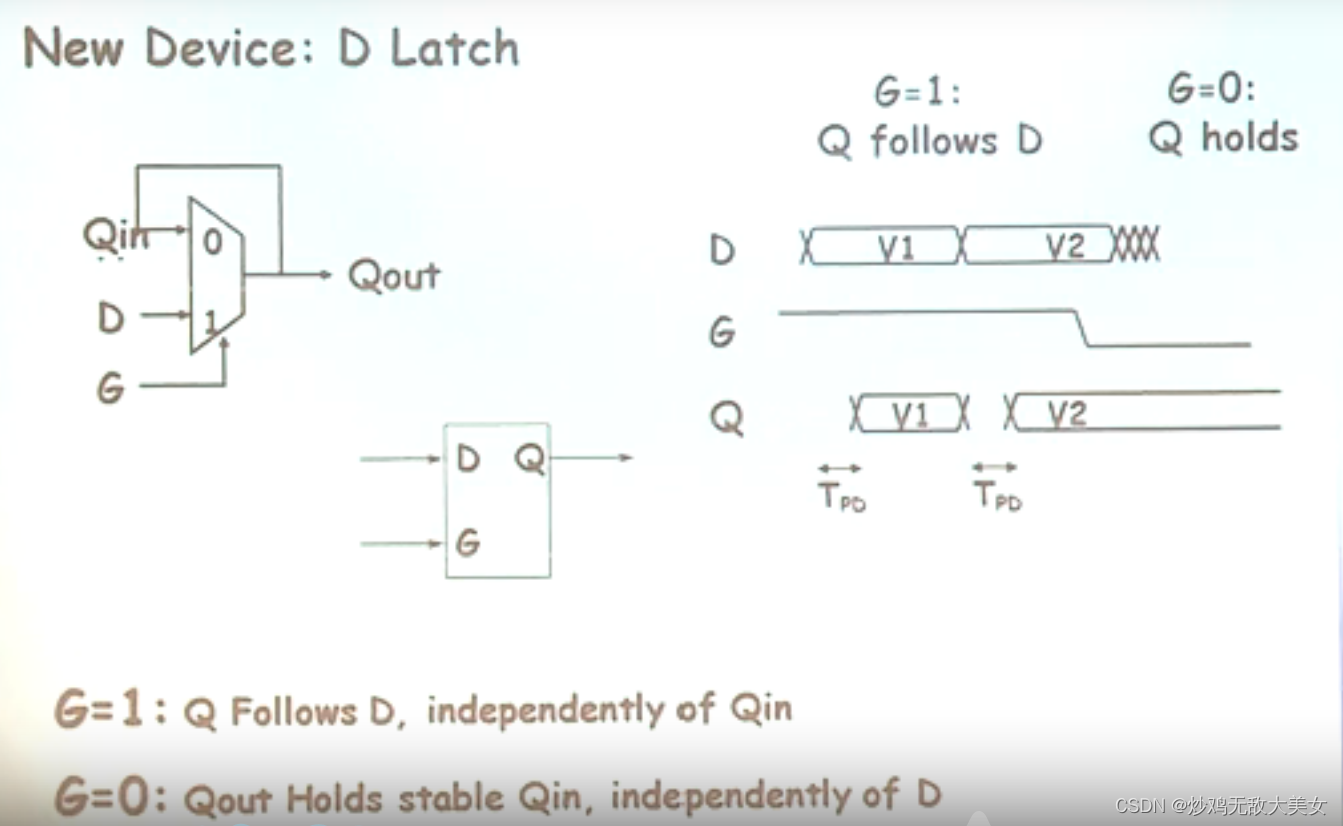

3.2.D触发器(也被称为D型锁存器)

如图所示为电平触发的D触发器。

可以将上图等价于使用数据选择器选择的电路,如下图所示。

其动作特点如下图所示:

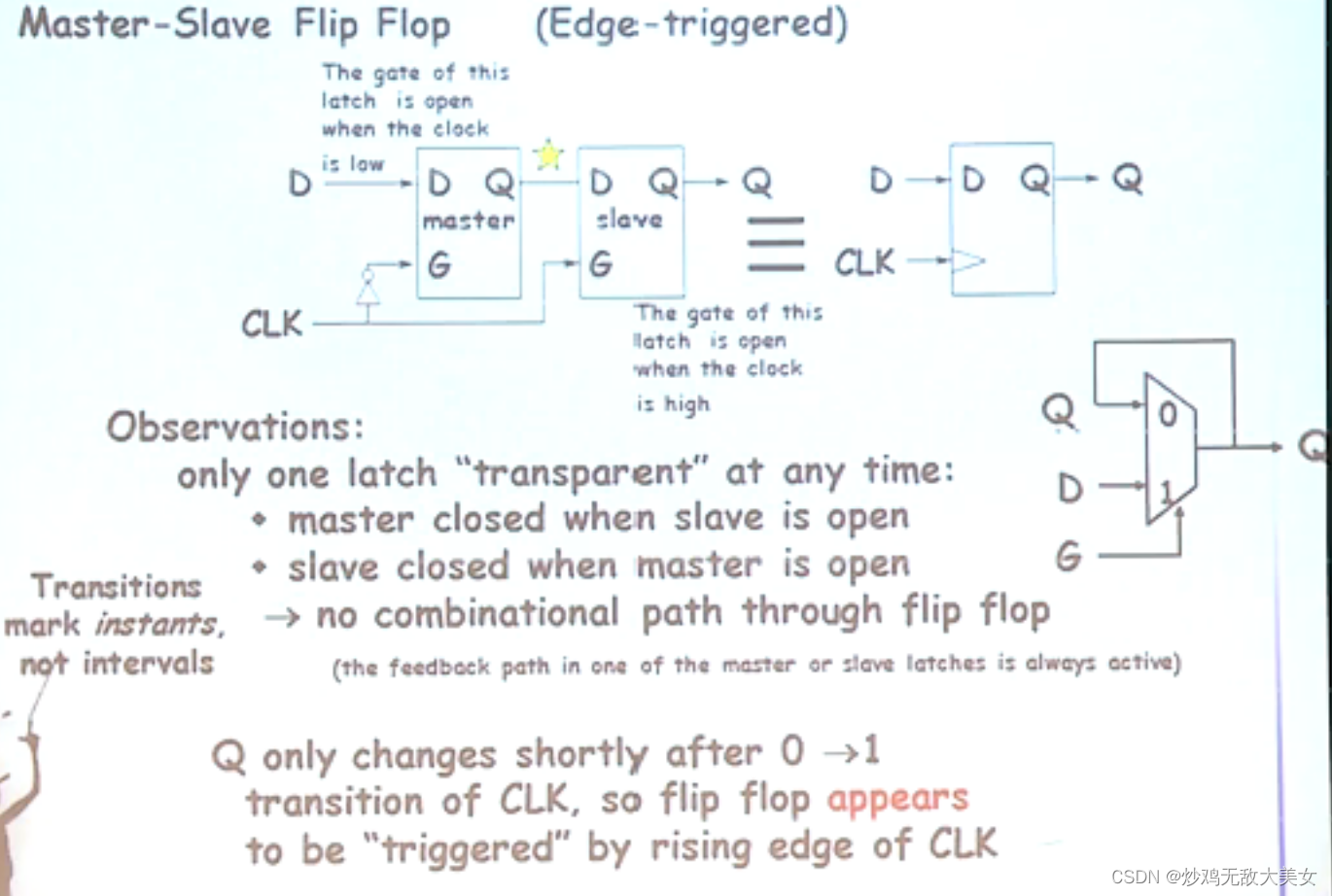

3.3.边沿触发的触发器(两个D锁存器)

下图所示是用两个电平触发的D触发器组成的边沿触发D触发器的原理框图。

注意: 观察图中所示的原理框图,当clk处于低电平时,主触发器(master,即左边第一个触发器)中的Q=D,而从触发器(slave,即右边的触发器)由于clk为低电平,输出Q直接保持着原来的状态不变;如果clk为高电平,则主触发器保持着原来的状态不变,此时从触发器的clk有效,输出端Q=D。

主从触发器的触发方式为脉冲触发,所有的锁存器都可以构成主从触发器。

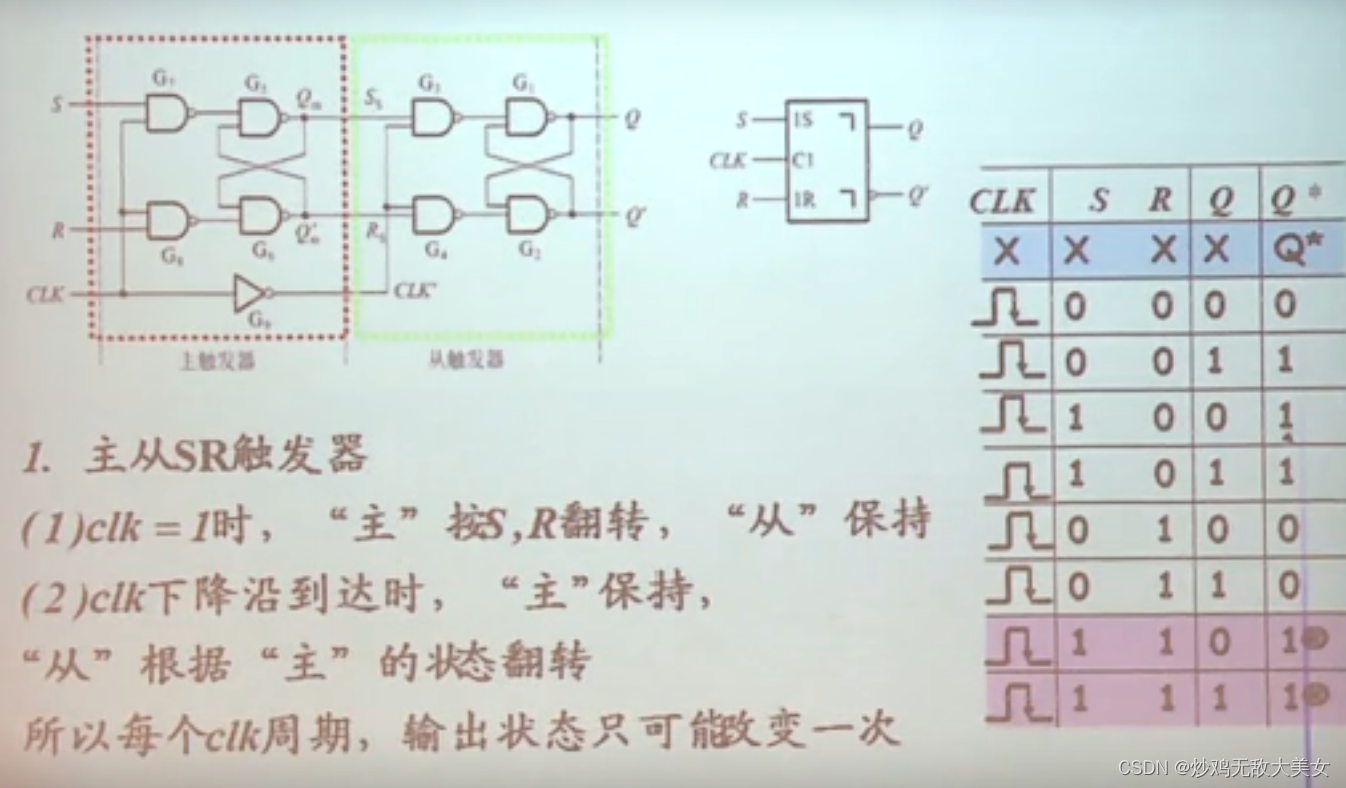

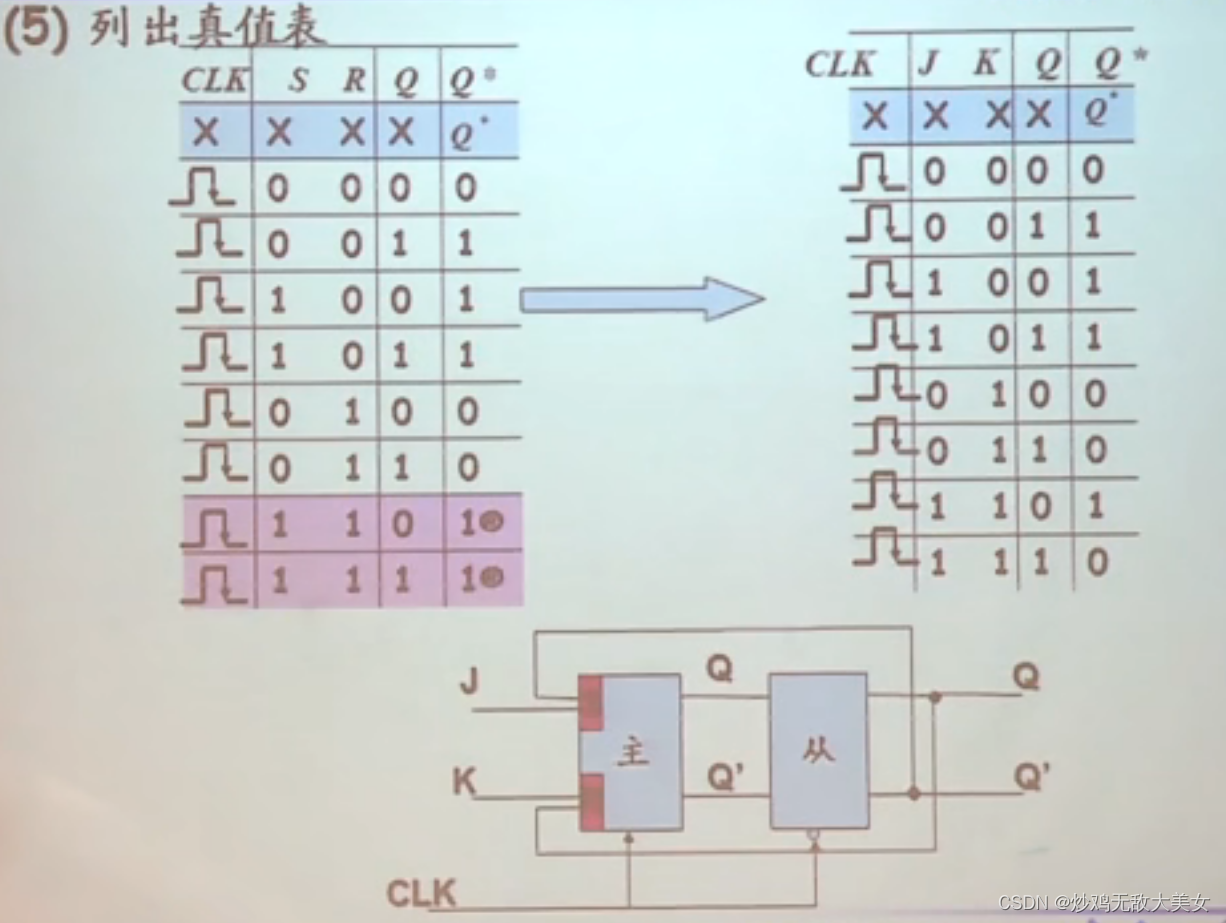

3.4.主从RS触发器

主从RS触发器为下降沿有效,与上述所说的边沿触发的触发器的上升沿触发方式相反,这是因为主从RS触发器的主触发器的clk是高电平有效。

如下图所示的主从RS触发器的图形符号,只需要画出主触发器部分,从触发器根据主触发器的状态取输入值,图中的图形符号表示下降沿有效。

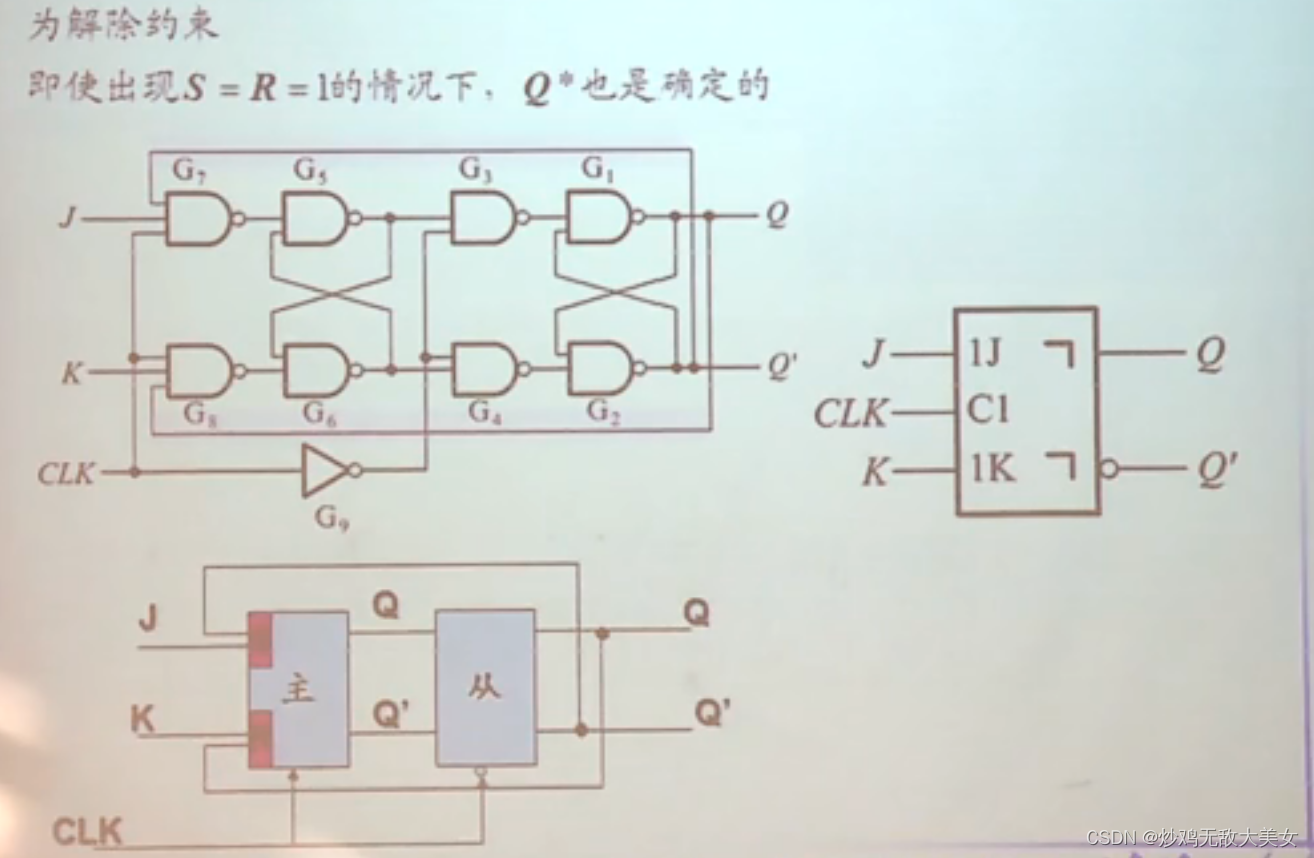

3.5.主从JK触发器

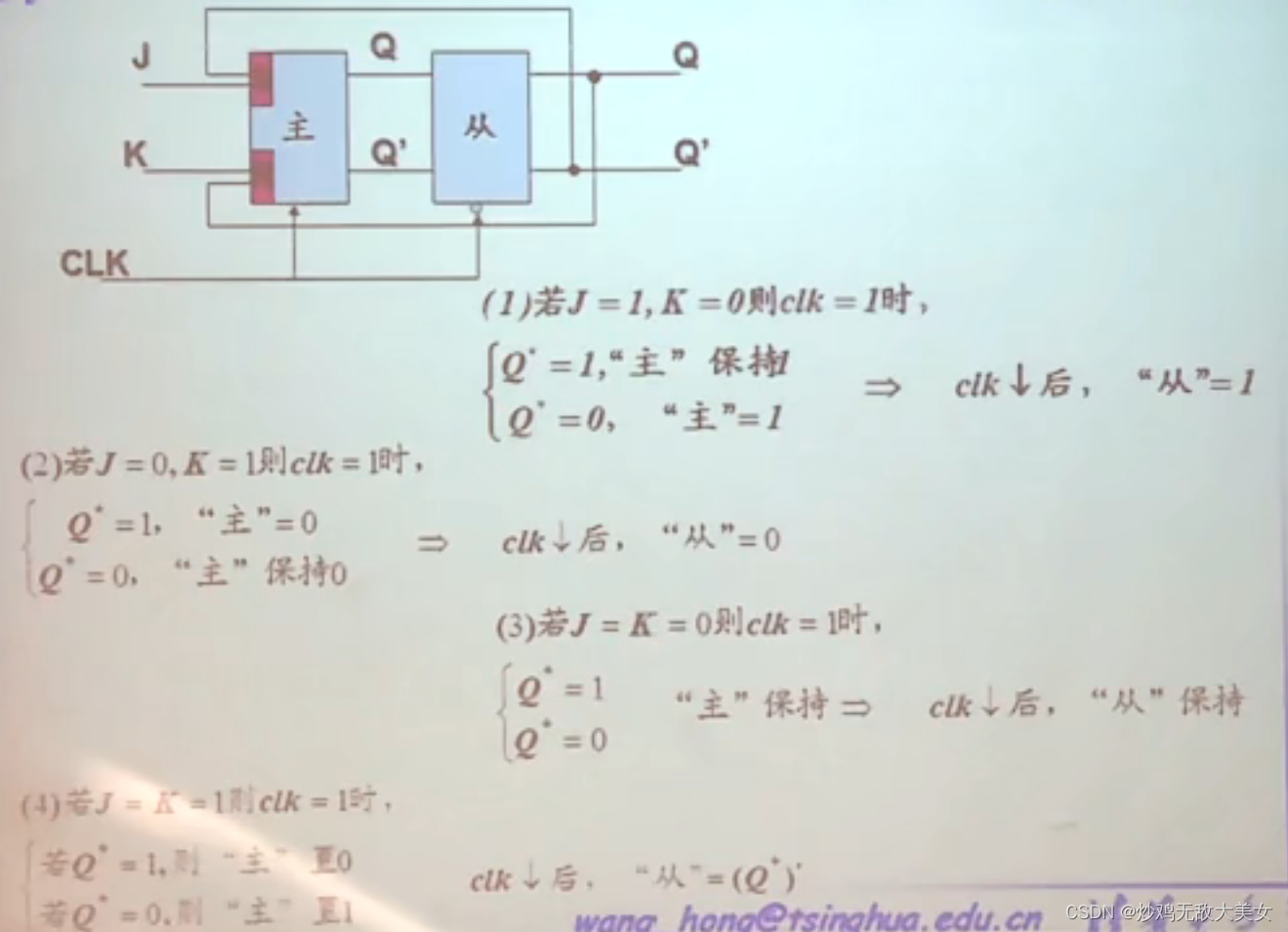

下图所示为主从JK触发器。相比于上述的主从RS触发器来说,分别从从触发器的输出端接反馈线至输入端,构成主从JK触发器。

J相当于置1端,K相当于置0端。J连接的是从触发器的Q'端,K连接的是从触发器的Q端。

过程分析如下:

其真值表如下:

四、按照电路的逻辑功能上来分

从电路的逻辑功能上来区分触发器可分为:RS触发器(SR触发器),JK触发器、T触发器、D触发器。

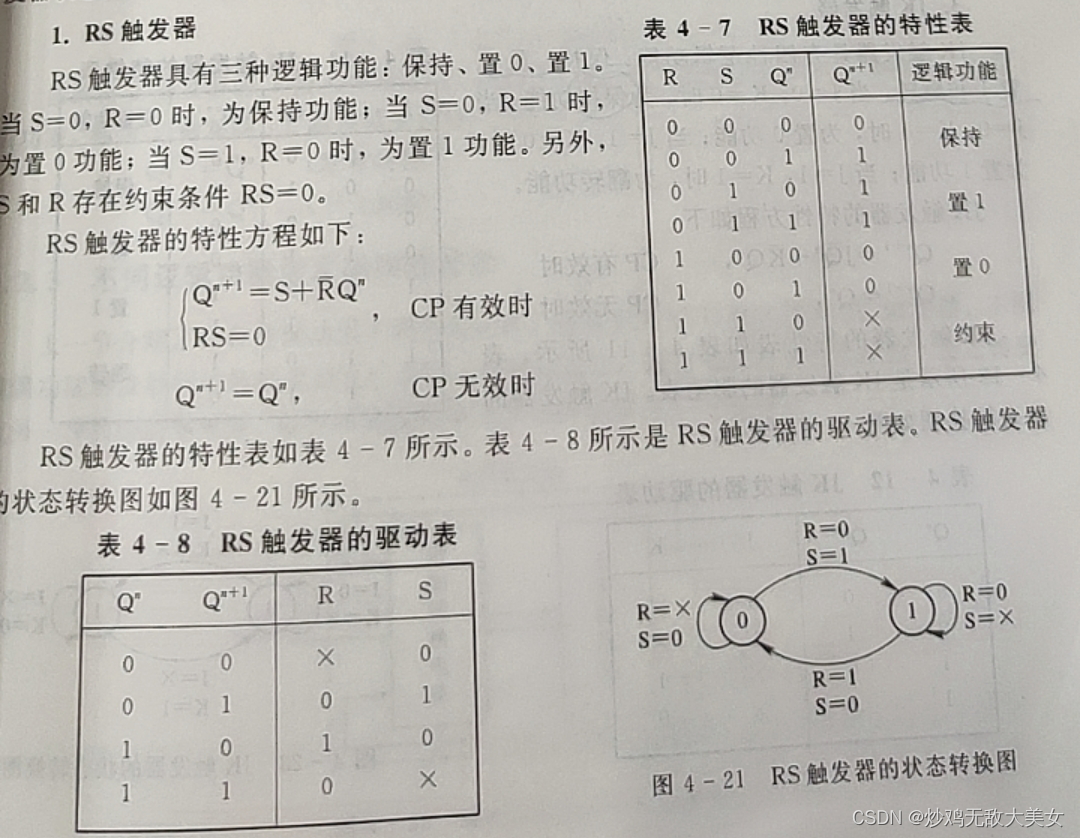

4.1 RS触发器

RS触发器具有三种逻辑功能:保持、置0、置1。其中S端为置1端,R为置0端。当S=0,R=0时,触发器为保持功能。触发器的特性表和特性方程如下:可以看出,RS触发器具有约束条件。

4.2 D触发器

D触发器在电路设计中是一类很重要的触发器。相比于RS触发器的功能,D触发器只有两种功能:置0和置1。

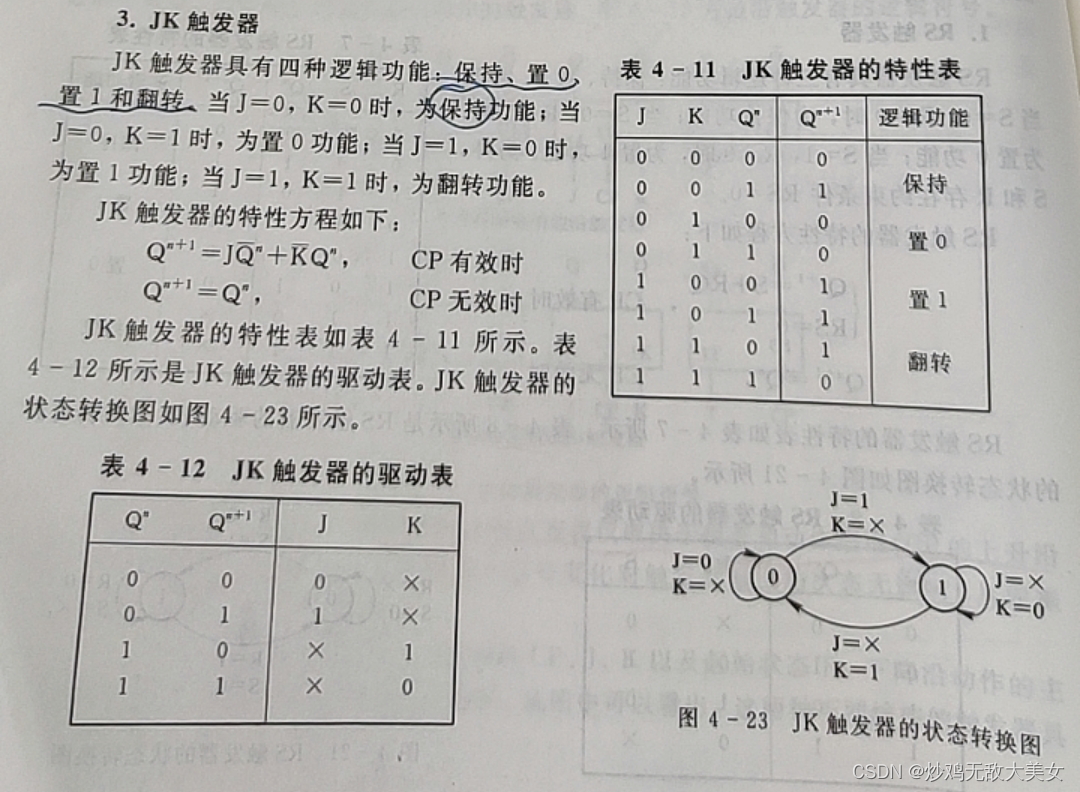

4.3 JK触发器

JK触发器具有四种逻辑功能:保持,置0、置1和翻转。

其中J相当于置1端。K相当于置0端。

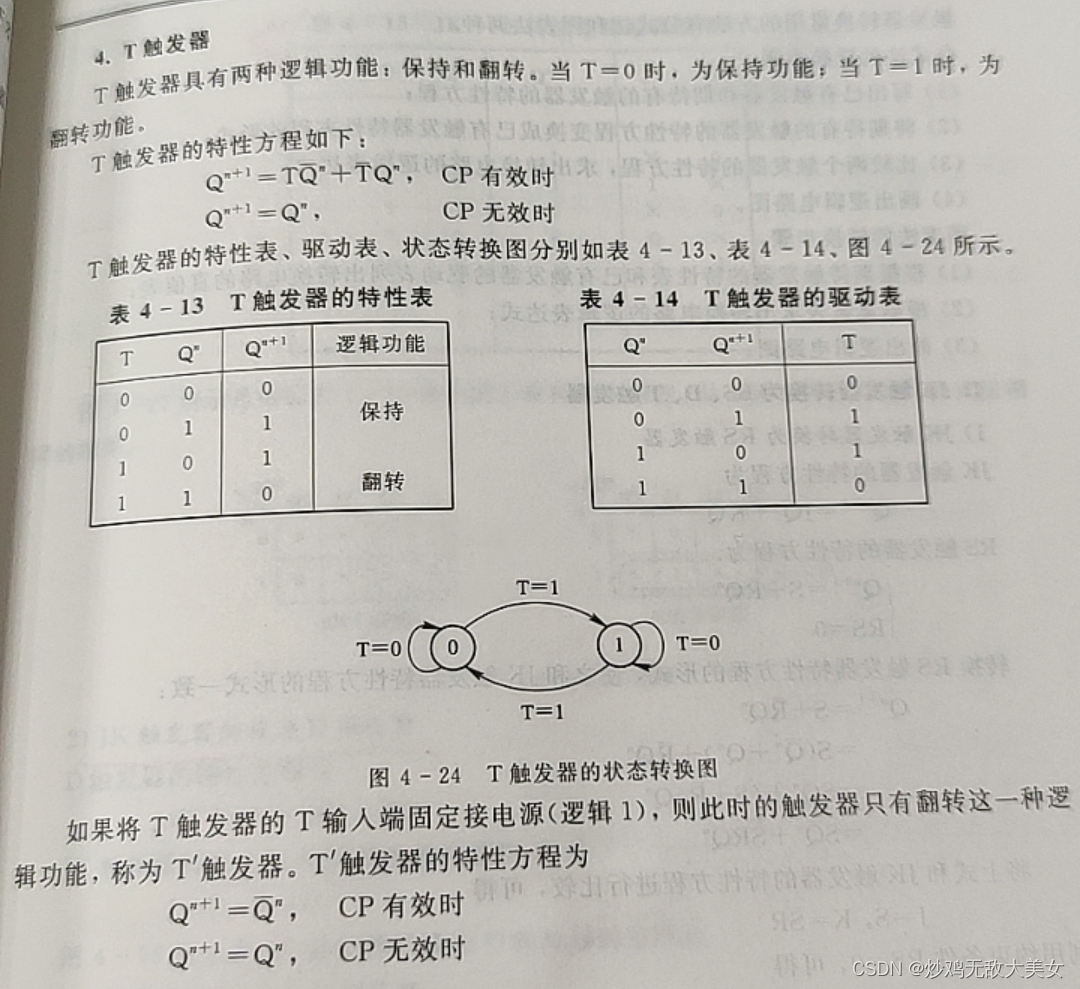

4.4 T触发器

T触发器具有两种逻辑功能:保持和翻转。当T=0时,为保持功能;当T=1时,为翻转功能。

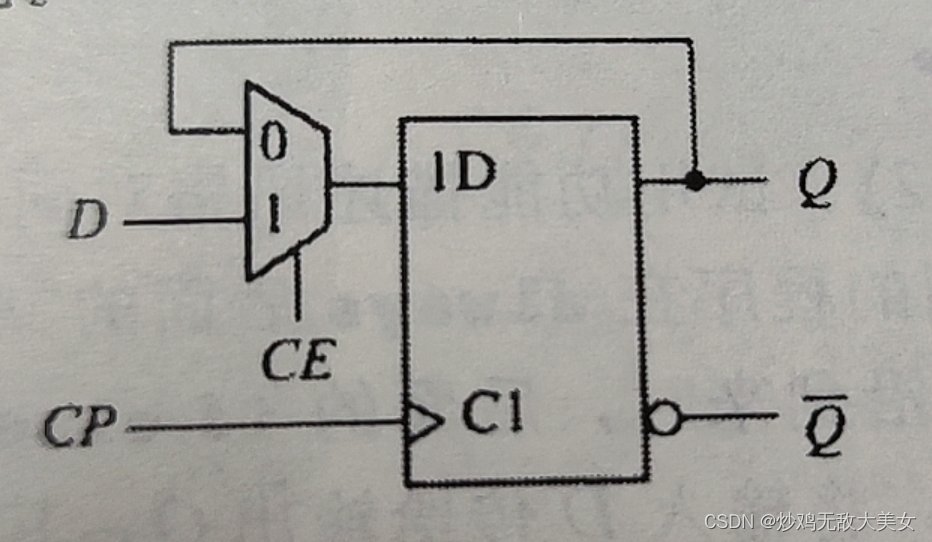

五、带有使能端的D触发器

这是一个具有时钟使能端的D触发器,如下图所示。这种触发器于普通的D触发器不同之处在于它是使用一个2选1的数据选择器进行控制。当CE=0时,选择Q端的状态作为输入数据送入到1D端,时钟上升沿到来时,仍然维持着;当CE=1时,选择外部D端作为输入数据,时钟上升沿到来时,实现普通的D触发器功能。

1709

1709

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?